# uTCA and MTCA.4 hardware used at KEK *Shin MICHIZONO* (KEK)

Contents:

- Facilities using TCA at KEK

- Boards used at KEK

- Performance of uTCA boards

- MTCA.4 board

## **Facilities using TCA Hardware at KEK**

### **High Energy Accelerator Research Organization (KEK)**

### Superconducting RF Test Facility (STF)

- ILC R&D facility

- 1.3GHz pulse SC

### **Compact Energy Recovery Linac (cERL)** •Test facility for a future 3 GeV ERL •1.3GHz CW SC

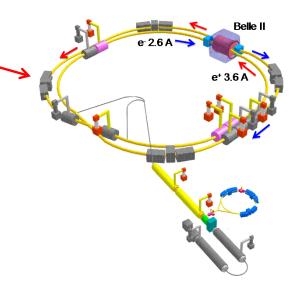

- **SuperKEKB**

- •Electron-positron collider

- •40x higher luminosity as

- the previous KEKB

- •Explore new physics

- beyond the standard model •509MHz CW NC&SC

## **Boards developed at KEK**

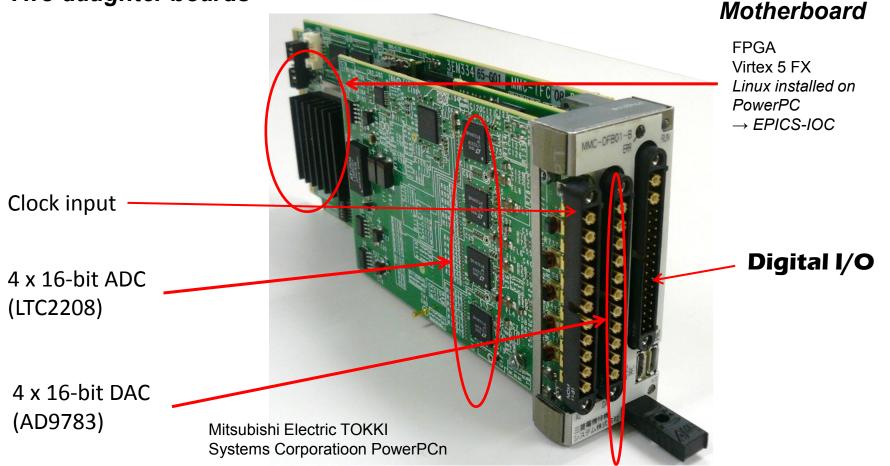

Past, present, and future TCA hardware used at KEK developed by KEK and manufactured by Mitsubishi Electric Tokki Systems Corporation

|                    | AD/DA/FPGA                                                                            | Software                                 | Application                                              |

|--------------------|---------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------|

| Board 1:<br>uTCA   | 4 16 bit ADCs (LTC2208 130 MSPS)<br>4 16 bit DACs (AD9783 500MSPS )<br>Virtex-5 FX    | EPICS<br>/Wind Rvier Linux<br>on PowerPC | cERL LLRF<br>STF LLRF<br>SuperKEKB LLRF<br>SuperKEKB BPM |

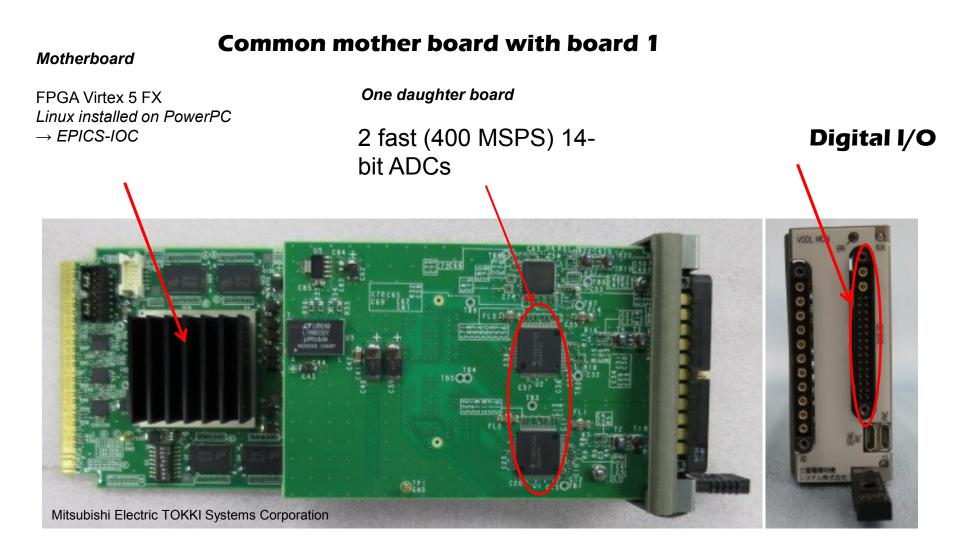

| Board 2:<br>uTCA   | 2 14 bit ADCs (ADS5474 400MSPS)<br>Virtex-5 FX                                        | EPICS<br>/Wind Rvier Linux<br>on PowerPC | SuperKEKB LLRF<br>cERL LLRF                              |

| Board 3:<br>MTCA.4 | 14 16 bit ADCs (AD9650,105MSPS)<br>2 16 bit DACs ((AD9783 500MSPS )<br>Zynq-7000 FPGA | EPICS<br>/Xilinx Linux<br>on ARM         | STF-2 LLRF                                               |

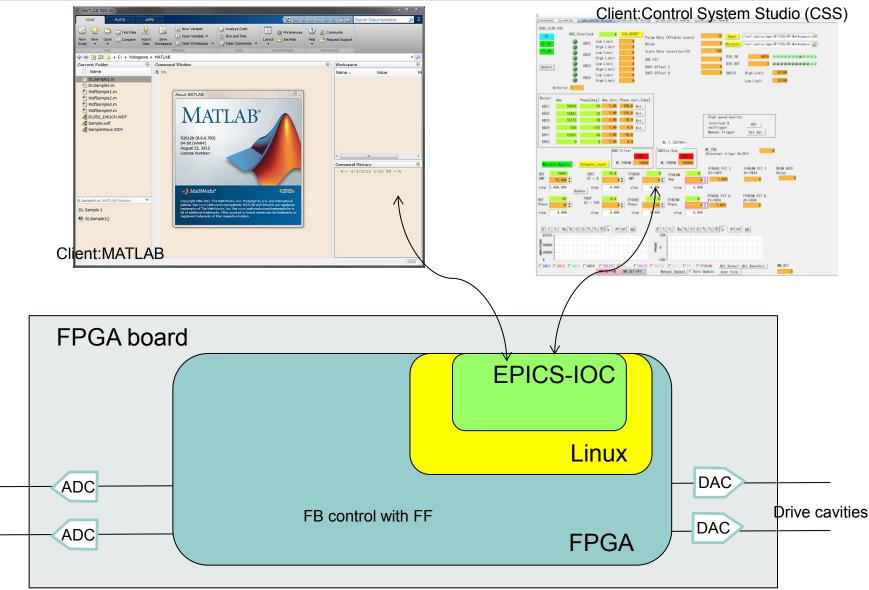

## **FPGA board and software**

Cavity 1

Cavity N

3rd MicroTCA Workshop (Shin MICHIZONO)

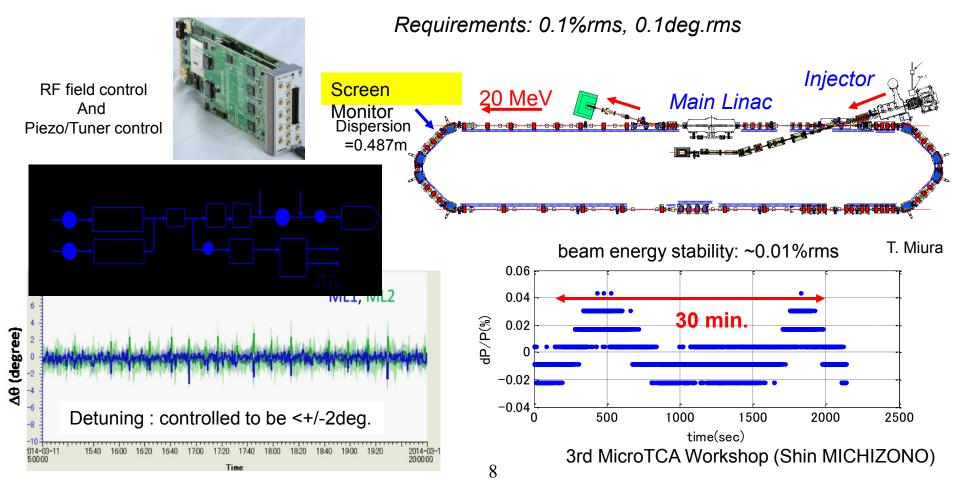

## μ**TCA AMC Board (Board 1)**

Two daughter boards

### **Board 1at STF**

### RF: 1.3 GHz pulsed (5 Hz)

#### LLRF Control Loop at STF l Q ADC Cavity Т ADC DAC ROT 2 00 DAC ROT P cavsim Select DAC2 Filter Gain DAC1 IIR ADC Cavity l Q Q ADC DAC ROT BASE FF Set BEAM FF BASE FF Set BEAM FF 800 kW Load klystron Reflector Phase LPF Cavity 1 Circ. shifter 1 400 kHz Down LO Varlable Q 1300 MHz Converter 1310 MHz Hybrid Modulator LPF Phase Reflector LPF Cavity 2 Circ. shifter 2 2 By Mathieu OMET ~0.01%rms, ~0.01deg.rms satisfy ILC stability requirements ( $\Delta A/A = 0.07\%$ , $\Delta \phi = 0.35^\circ$ ) 15 20.025 Gradient [MV/m] 20.020 Beam transient 20.015 [MV/m] 10 20.010 20.005 20.000 5 19.995 19.990 1000 1100 1200 1500 1600 1300 1400 Time [µs] 0 Mitsubishi Electric TOKKI Systems Corp 0 500 1000 1500 2000 Time [µs]

#### 3rd MicroTCA Workshop (Shin MICHIZONO)

#### 6

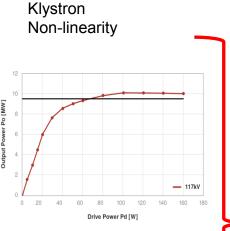

## **Klystron & cavity simulator**

- Klystron simulator based on two direct lookup tables

- Cavity simulator based on the time discrete cavity differential equation

$\dot{V}_c = -\omega_{1/2}V_c + \omega_{1/2}R_L(2I_g - 2I_{b0})$

Superconducting Cavity with beam

7

3rd MicroTCA Workshop (Shin MICHIZONO)

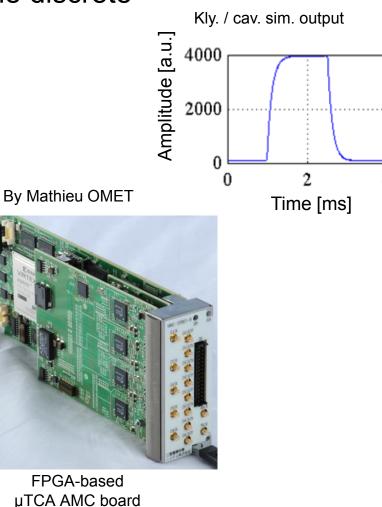

### Board 1 at cERL

|           | NC cavity | SC cavities |             |            |            |

|-----------|-----------|-------------|-------------|------------|------------|

|           | BUN       | Inj1        | lnj2 & lnj3 | ML1        | ML2        |

| Amplitude | 0.05% rms | 0.01% rms   | 0.01% rms   | 0.013% rms | 0.013% rms |

| Phase     | 0.06° rms | 0.02° rms   | 0.02° rms   | 0.014° rms | 0.015° rms |

## μTCA AMC Board (Board 2)

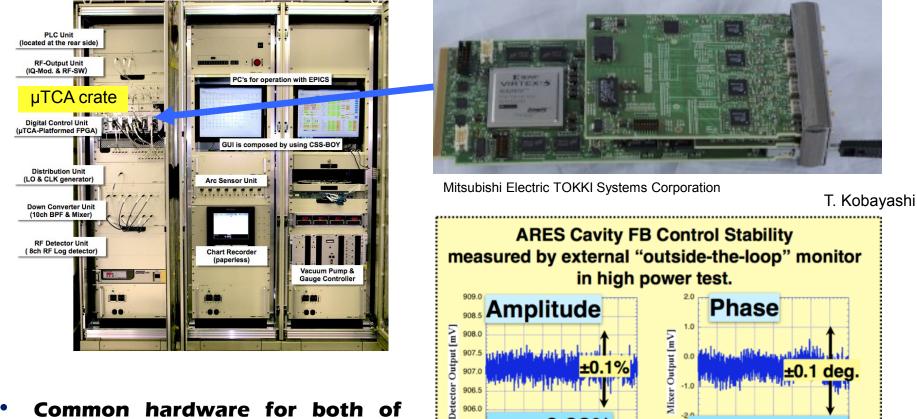

## **Board 1 at SuperKEKB**

#### New LLRF system for one klystron

Common hardware for both of ARES (NC) & SC Cavity

3rd MicroTCA Workshop (Shin MICHIZONO)

0 0.5

3.5

1 1.5

rms: 0.02 deg

Time[ms]

2.5

905.5

905.0

0.5

1.5

Time [ms]

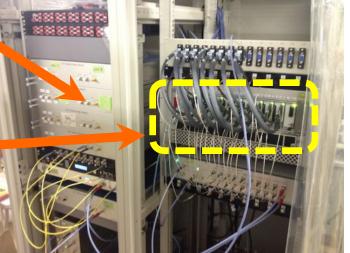

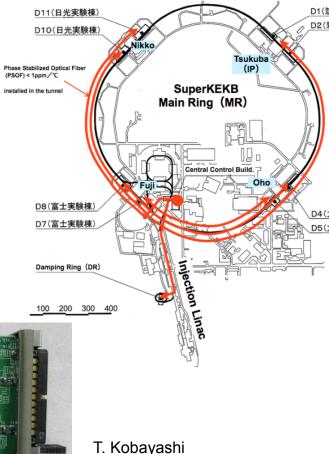

## **Board 2 at SuperKEKB**

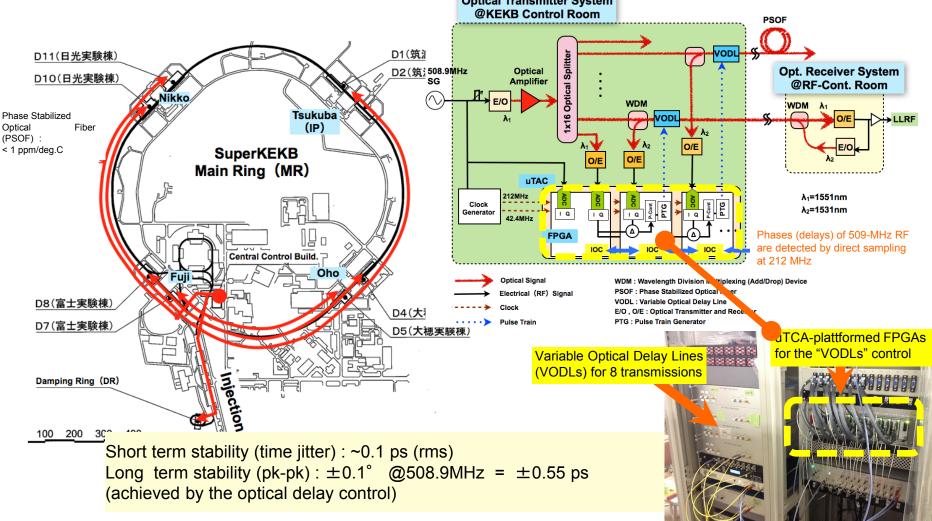

### Optical delay stabilization of the RF reference distribution

- Variable Optical Delay Lines (VODLs) for 8 transmissions

- µTCA-platformed FPGAs for the control of the variable optical delay

Phases (delays) of 509-MHz RF are detected by direct sampling at 212 MHz

> Short term stability (time jitter) : ~0.1 ps (rms) Long term stability (pk-pk) :  $\pm 0.1^{\circ}$  @508.9MHz =  $\pm 0.55$  ps (achieved by the optical delay control)

> > STA IVIICIO I CA VVOIKSHOP (SHIH IVIICHIZONO)

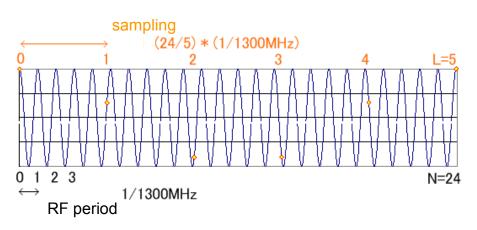

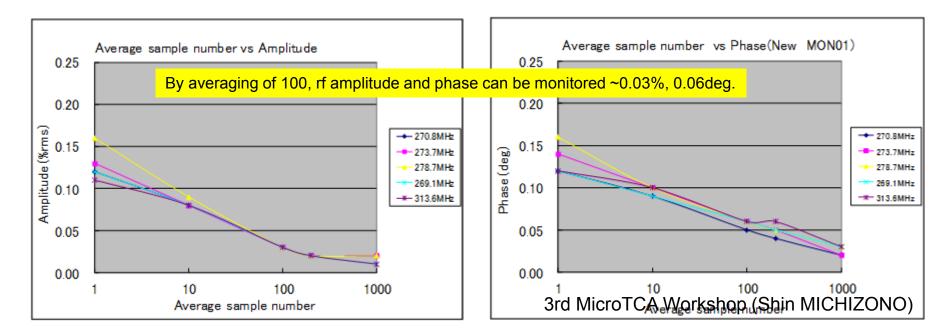

## **µTCA AMC Board (Board 2) :direct sampling**

Undersampling procedure for direct sampling. This will be installed at cERL.

| No. | Clock | RATE       | L          | Ν        |

|-----|-------|------------|------------|----------|

|     | [MHz] |            | Data cycle | RF cycle |

| 1   | 270.8 | 1300* 5/24 | 5          | 24       |

| 2   | 273.7 | 1300* 4/19 | 4          | 19       |

| 3   | 278.6 | 1300* 3/14 | 3          | 14       |

| 4   | 269.0 | 1300* 6/29 | 6          | 29       |

| 5   | 313.8 | 1300* 7/29 | 7          | 29       |

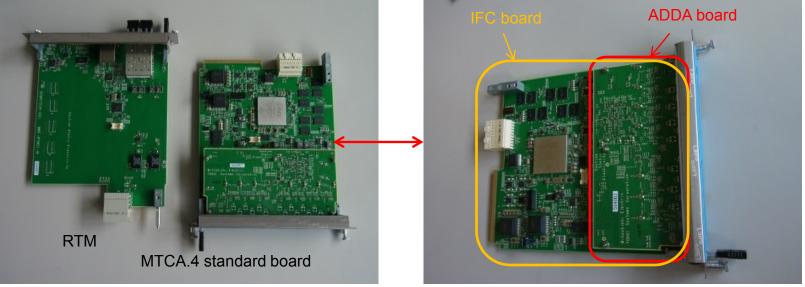

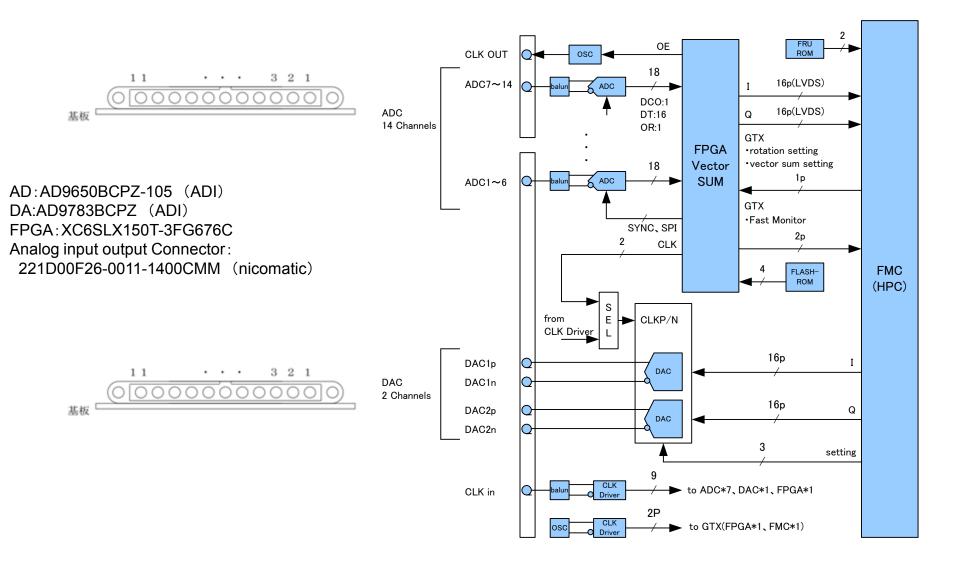

## MTCA.4 Standard Boards (Board 3)

Digital LLRF control boards for STF-2

•MTCA.4 standard board

- mother board:Zynq-7000 FPGA (XC7Z045): Linux installed on ARM (EPICS-IOC), two FMCs

- FMC (HPC) ADDA board (double width):

14ch ADCs (AD9650, 16bit), 2ch DACs (AD9783, 16bit)

- RTM module:RJ-45 connector, 14ch DIO connectors

2ch SFP connectors (Data communication between boards)

Mitsubishi Electric TOKKI Systems Corporation

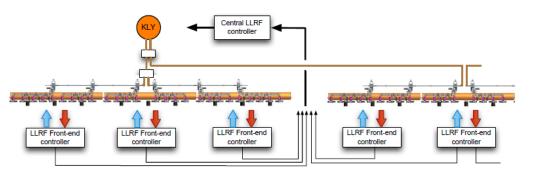

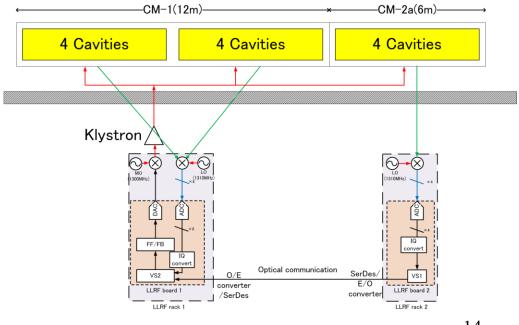

## **MTCA.4 Standard Boards at STF-2**

LLRF system in ILC-TDR (39 cavities per klystron)

LLRF system for STF-2

RF: 1.3 GHz pulsed (5 Hz)

- Each front-end controller computes partial cavity-field vector-sums and sends those to the central LLRF controller

- The central LLRF controller performs the total vector-sum calculation and feedback/feedforward operation

- At STF-2 two digital LLRF boards connected by optical communication will be configured for operation

- → minimal configuration of an ILC LLRF system

## Summary

- We have developed uTCA and MTCA.4 boards for mainly LLRF control.

- Digital FB control (board 1)

- Direct sampling (board 2)

- MTCA.4 with 14ch AD board (board 3)

- Typical performance of the LLRF system is ~0.02%rms, 0.02deg. rms and these satisfy the LLRF requirements.

3rd MicroTCA Workshop (Shin MICHIZONO)

## **AD DA FMC**

## **Board 2 for Optical Delay Stabilization**

### of **RF** Reference Distribution for SueprKEKB

T. Kobayashi, et al.

- RF reference signal is optically distributed into 8 sections by means of "Star" topology configuration from the central control room (CCR).

- "Phase Stabilized Optical Fiber", which has quite small thermal coefficient, is adapted : < 1ppm/°C (5 ps/km//°C)

- Furthermore, for thermal drift compensation, variable optical delay lines (VODLs) are controlled by uTCA-FPGAs at CCR for all transmission fibers.