# MicroTCA.4-based Timing System used at XFEL and FLASH/FLASH2

## \_ Agenda

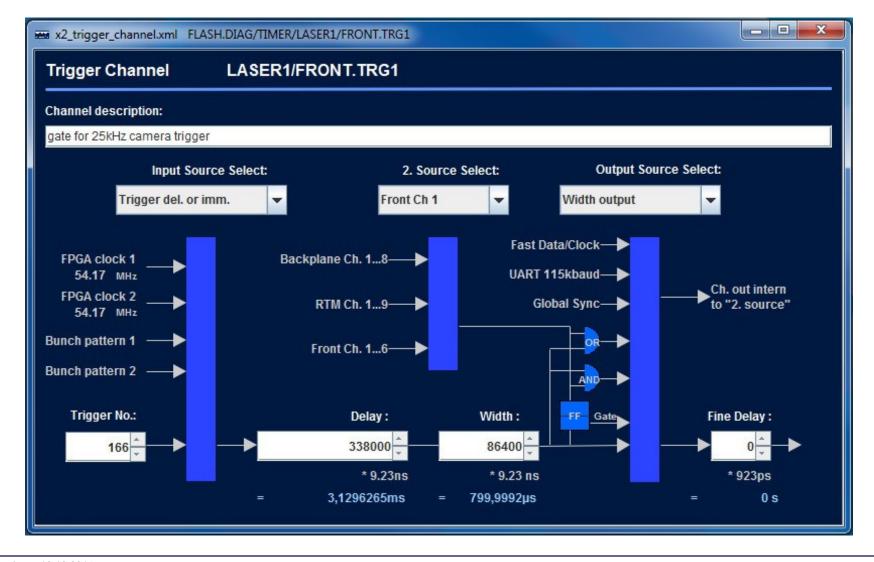

- x2timer parameters

- Hardware implementation

- External timing adapter (ETA)

- Timing system setup

- Drift compensation daughterboard

- Rear Transition Module Types

- Software implementation

- Setup in FLASH

- Setup in XFEL outlook

#### x2timer parameters

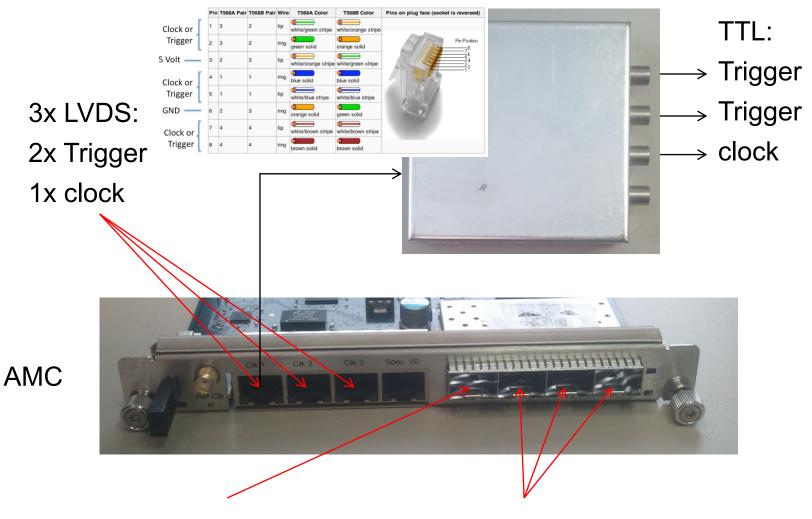

- double-width AMC

- receives/transmits 1 1.3GHz optical timing signal

- Trigger/bunch pattern/FPGA clocks outputs via

- 3x RJ45 front connectors (2 triggers per connector)

- LVDS signal level / TTL with external hardware

- → 8x on µTCA backplane (MLVDS bus on port 17-21)

- → 9x on optional RTM LVDS & TTL level

- Low jitter clock output via

- 3x RJ45 front connectors

- TCLKA/TCLKB and crosspoint switch on MCH

#### **External timing adapter**

**Input from Timing Master**

**Output to other Timing Receivers**

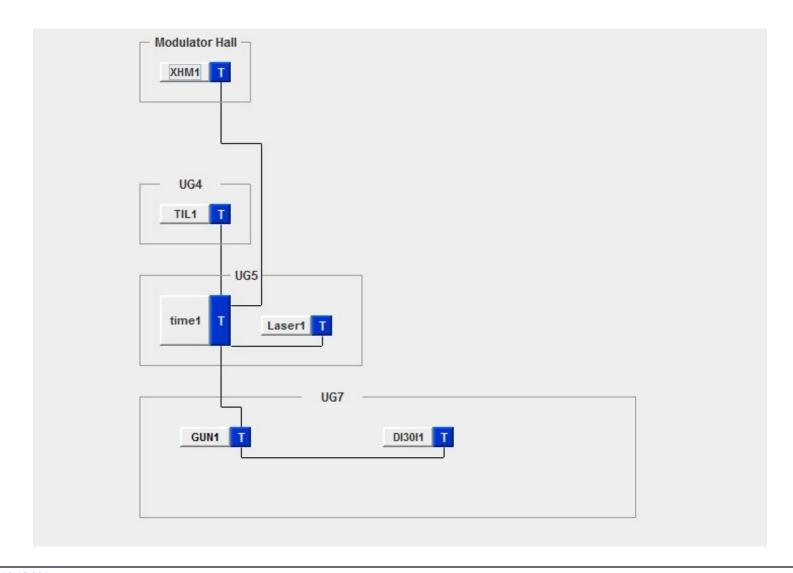

#### Timing system setup

- Star topology

- One timing master, synchronized by Master Oscillator

- Also connected to machine protection system

- Master oscillator clock is recovered on each receiver

- No limitation in no. of receivers

- each receiver can forward signal to another system

- Timing information is (de-)coded in onboard FPGA

- System keeps running even when CPU/network fails

- Receivers can be added/removed during runtime

# XFEL Hardware implementation

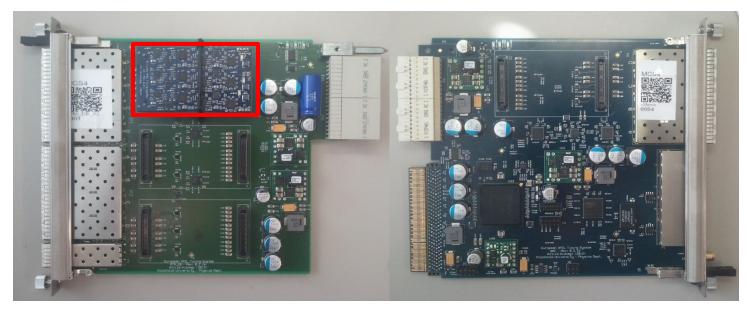

#### **Rear Transition Module**

#### **AMC**

Hardware design @ Physics Department of Stockholm University

#### Drift compensation daughterboard

- Addon board for AMC and transmitter RTM

- 3 channels, each controlled by seperate microcontroller

- Programmable via HPM.1

- Measure phase difference between MO clock and looped signal

- Increase / decrease delay by some picoseconds to keep phase stable (long-term phase drift below 80ps peak-peak)

#### Rear transition module types

- Type 1: daughter-board RTM (available)

- Up to 9 \* output of optical timing signal for other systems, cable length and drift compensated per output channel

- Type 2: TTL Trigger RTM (in production)

- Up to 9 \* TTL level trigger output on LEMO connector

- 2 \* high-precision output with rise-/fall-delay in steps of 100ps

- Type 3: optical Trigger RTM (under development)

- Up to 9 \* optical trigger output on ST connector

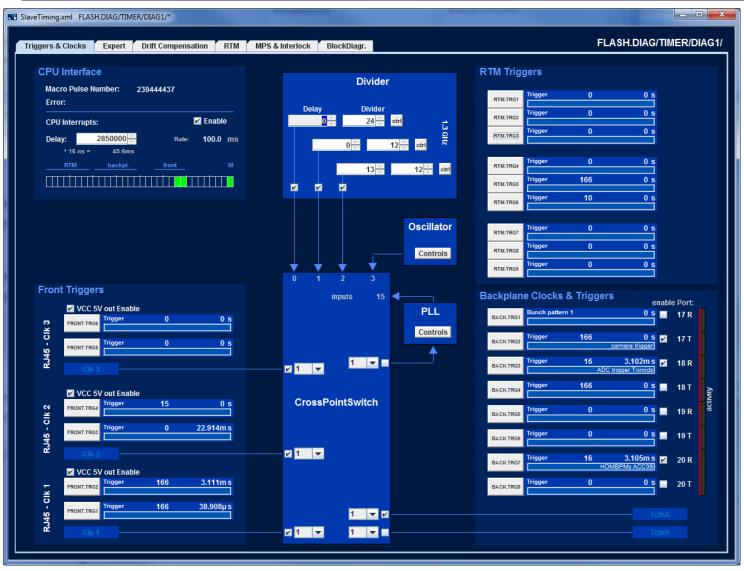

#### FEL | Software implementation

- Each crate contains one CPU AMC

- x2timer server running on that CPU

- One server can manage several x2timer AMCs via PCIe

- Configurable remotely via DOOCS / Ethernet

- FPGA firmware upgrade also possble via PCIe

- x2timer hardware generates CPU interrupts that may be used for other parts of the system, e.g. sampling of ADC channel, data aquisition, etc.

#### Software implementation

### **XFEL** Configuration of x2timer - 2

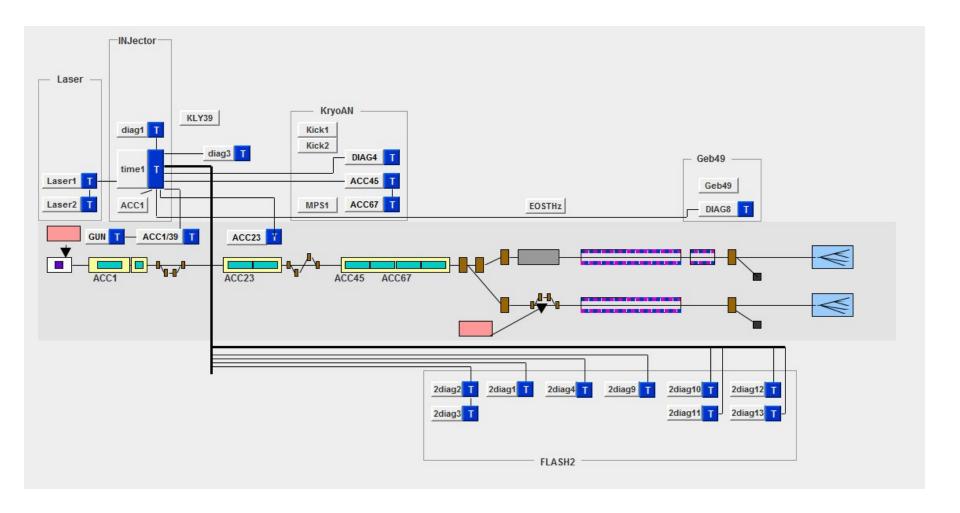

### x2timer setup in FLASH/FLASH2

## XFEL x2timer setup in XFEL