# Conceptual Design of LCLS II BPM System on MicroTCA.4

## LCLS-II (Phase I: 2010-2013 RIP)

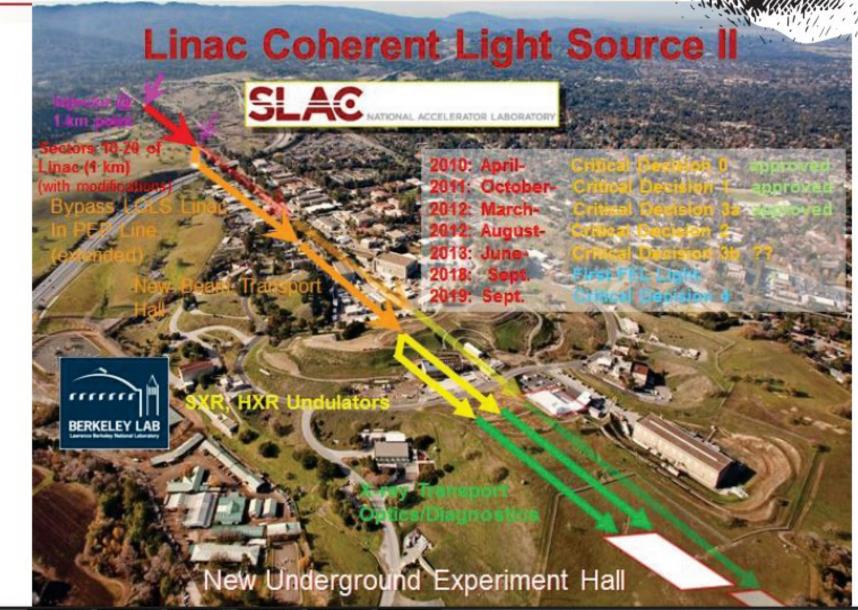

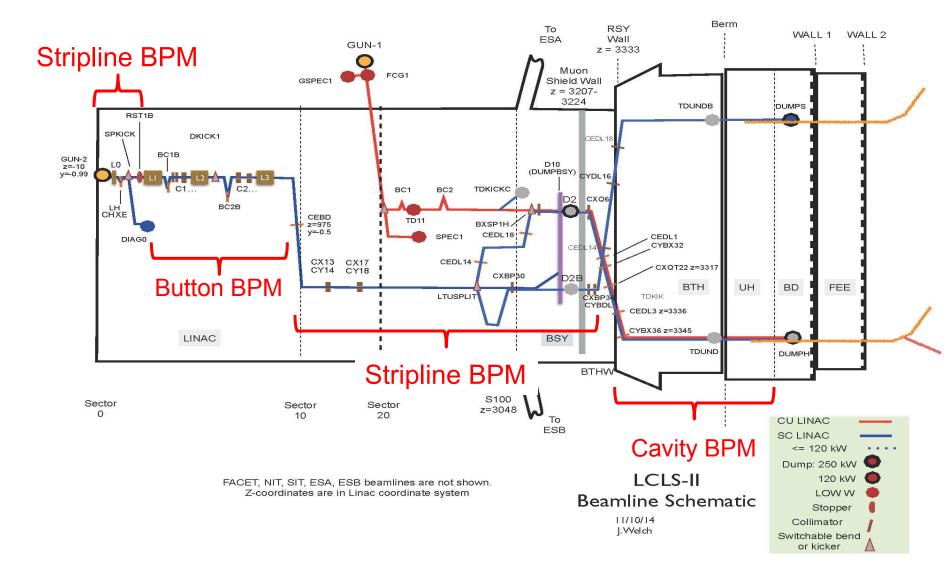

#### LCLS II Project

- LCLS-II is a XFEL with super conducting LINAC

- It is capable of 1 MHz CW beam

- Maximum beam power will reach ~1MW

- Maximum bunch charge 300pC

- Minimum bunch charge 10pC

<del>SLAC</del>

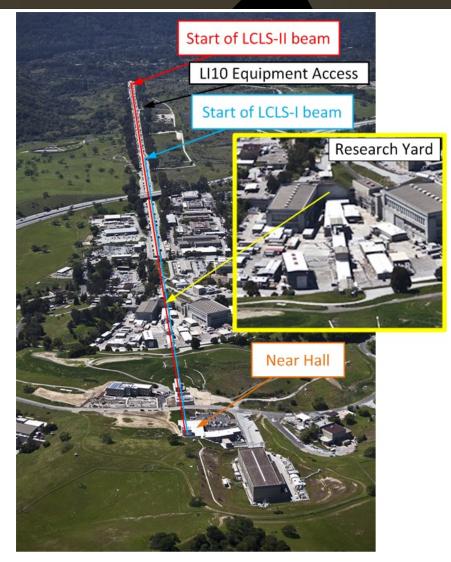

#### LCLS II Project

-SLAC

- Build BPM control system for LCLS-II

- Stripline BPM (SLAC, LBNL)

- Button BPM

- Cavity BPM

- Provide orbit and TMIT information to fastfeedback and machine protection system

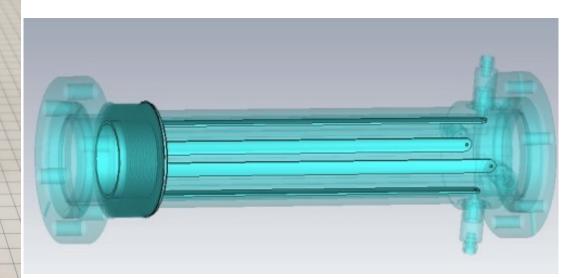

#### Stripline BPM

- Standard SLAC Linac pickups, 1" diameter, 4.75" length

- LBNL APEX Gun pickup, 1.18" diameter, 5.11" length

- Process BPM signal at 300MHz

**SLAC BPM**

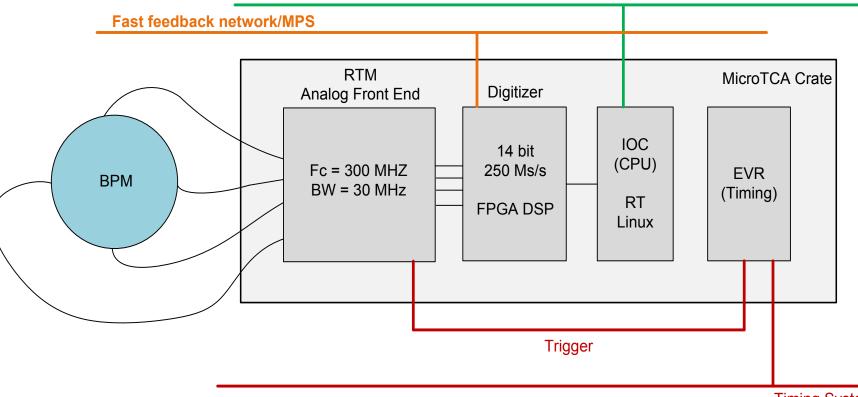

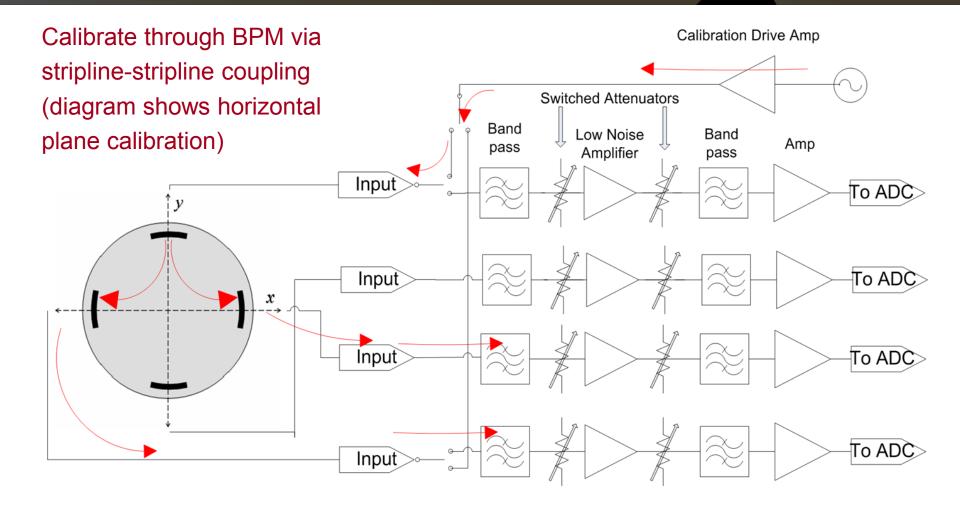

#### **Stripline BPM System Architecture**

Timing System

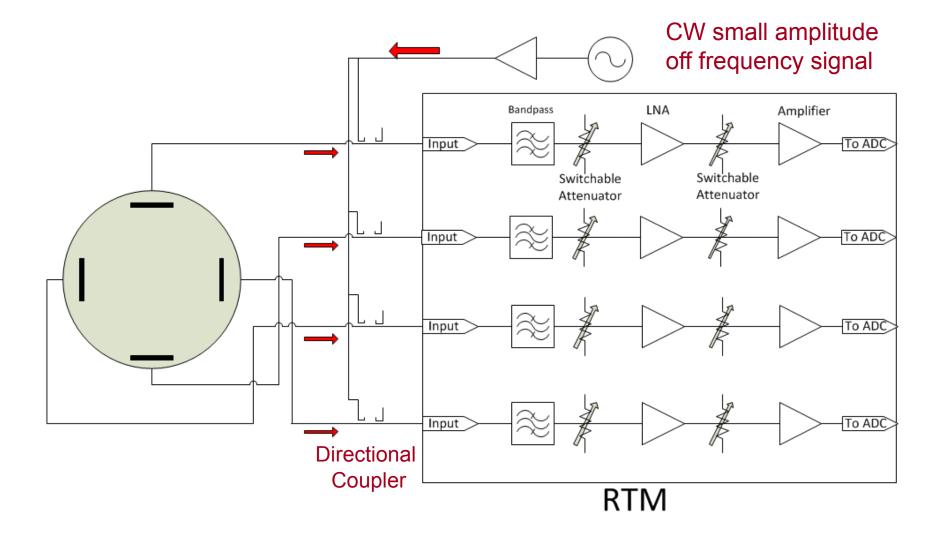

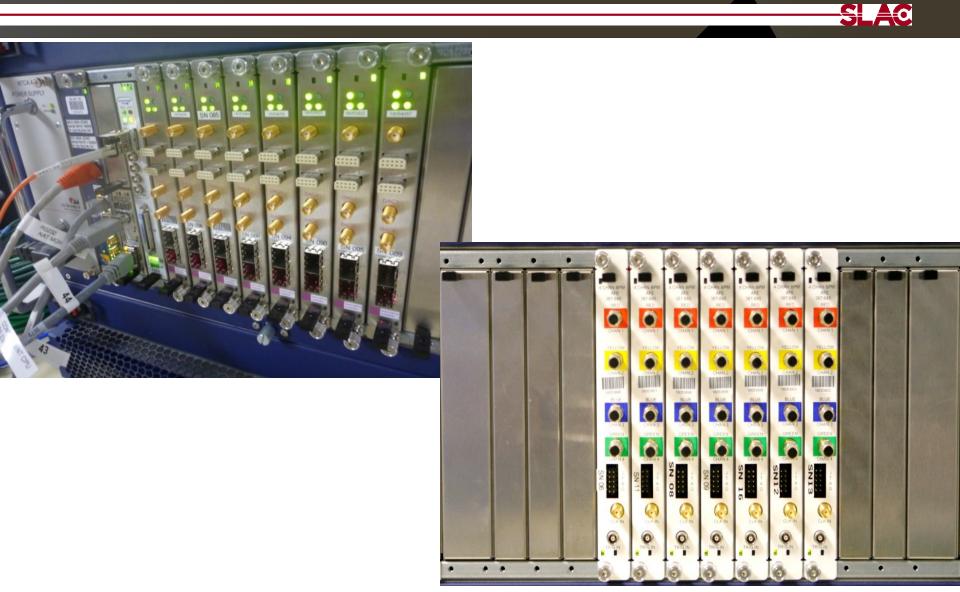

#### SLAC BPM RTM for LCLS-I

- We will utilize the signal processing portion of the BPM RTM designed for LCLS-I

- BPM calibration circuit has to be redesigned to accommodate 1MHz beam rate

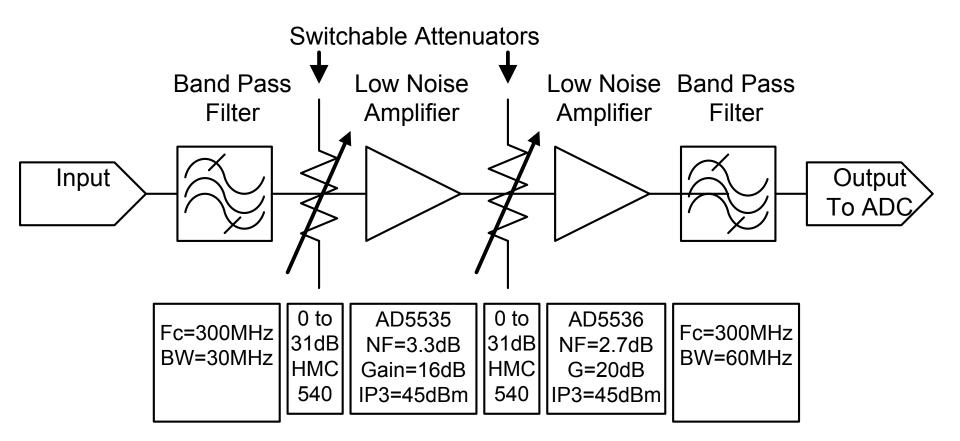

### **AFE Block Diagram**

#### Self-Calibration

-SLAC

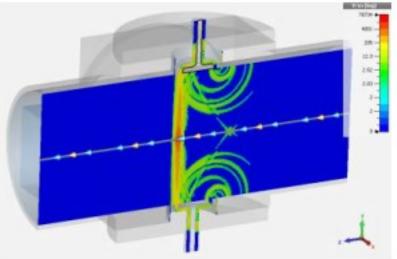

- Button BPMs are located in the cryomodule

- Designed by Fermilab

- It is very similar to the European XFEL cold button BPM pick up

- The pickup has 20mm diameter with 3mm gap

Simulation of the pickup in CST Curtesy of A. Lunin FNAL

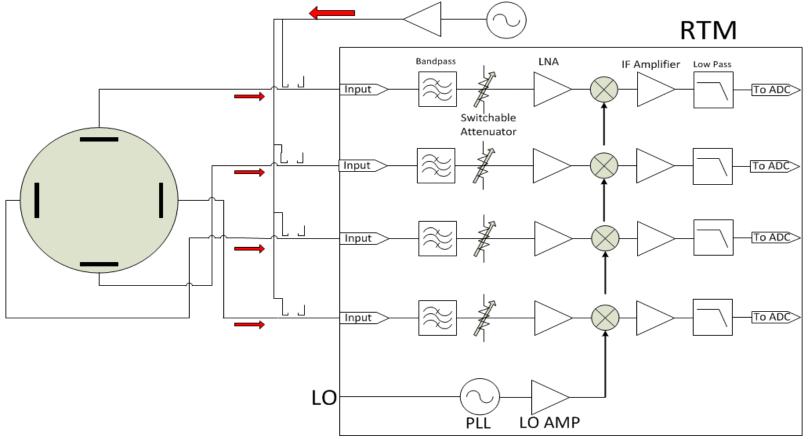

#### **Button BPM Electronic**

- The BPM signals will be processed 1.5 2GHz

- Signal will be down-mixed to an IF signal and sampled at 119MHz

<u>SLAC</u>

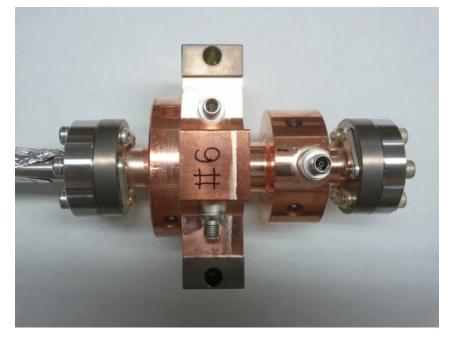

- BPM pickup developed in collaboration with PAL

- Currently being used at LCLS-I's undulator hall

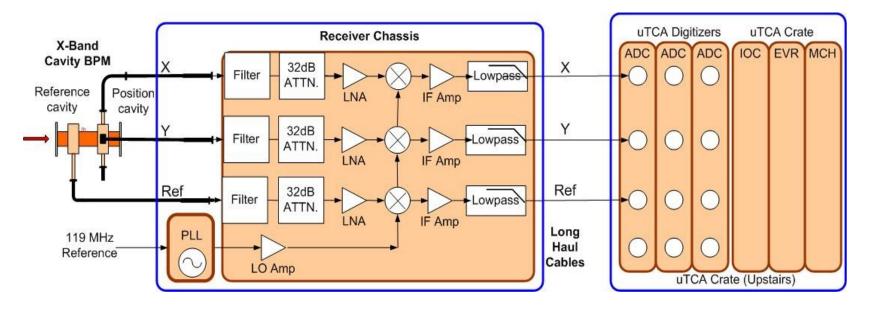

- The receiver will processes the TM010 monopole reference cavity signal and a TM110 dipole cavity signal at approximately 11 GHz using a heterodyne technique

#### X-Band Cavity BPM Electronic

- Due to the high loss of signal strength over cables, the down-converter has to reside inside the tunnel

- The ADC and processing electronics will reside in the surface building

Curtesy of A. Young

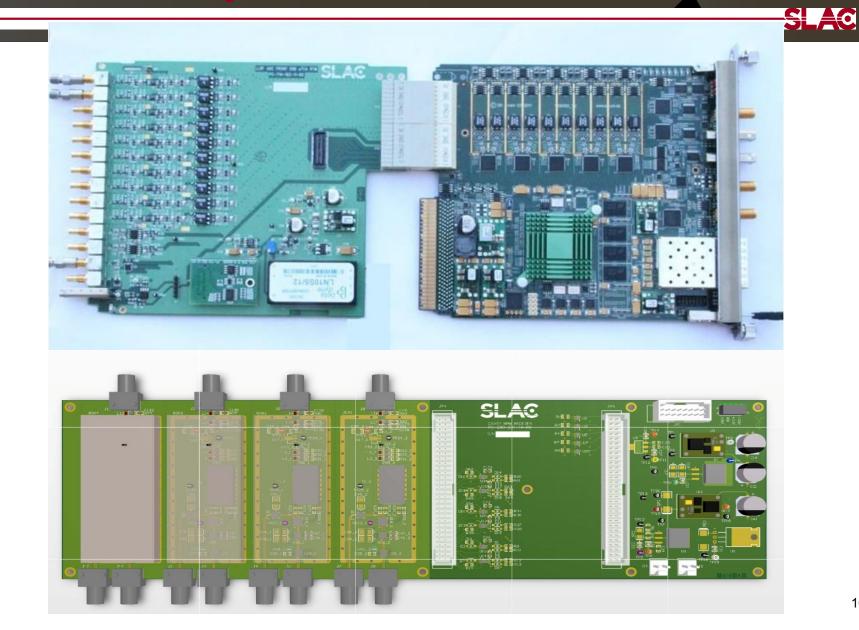

#### Digitizer

- Struck Digitizer

(SIS8300/SIS8300-L/SIS8325)

- With SLAC modifications

- 250 MSa/sec sampling clock 14bit ADC

- 125 MSa/sec sampling clock 16 bit ADC

- The BPM and LLRF system will try to use the same digitizer

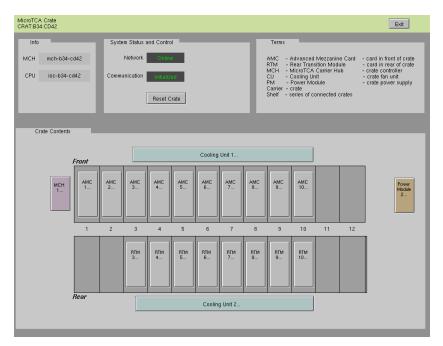

### **MicroTCA Components**

### CPU: Concurrent Technologies AM 310/302-52

- 2-core Core i7 processor

- 2 GB RAM

- Ethernet interface

- Serial port for IOC console

- MicroTCA Carrier Hub

- 2 Gigabit Ethernet interfaces

- Serial port for MCH console

<u>SLAC</u>

#### Power Supply and Timing

- The plan is to use Wiener's 1kW power module due to the low power noise ripple

- LCLS-II will be a 1MHz machine

- Can no longer use the MRF EVR module for timing

- SLAC has to develop a new timing system

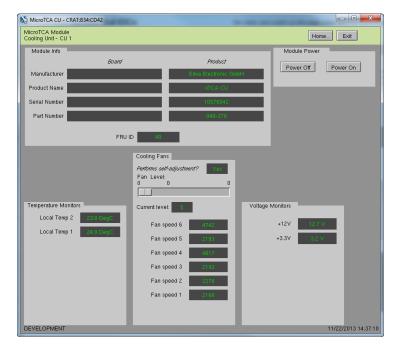

#### **IPMI Monitoring using EPICS**

The SLAC EPICS IPMI software provides remote monitoring and control of MicroTCA systems via their MCHs. EPICS monitors temperature, voltage, current, and fan speed sensors and system reset. These readbacks and control signals are available to users via EPICS PVs. The software runs in an EPICS IOC process and is configured with a list of MicroTCA systems to monitor. For each remote system, it discovers the MCH vendor and uses the appropriate message protocol

#### **BPM System**

# Thank you

mTCA Workshop DESY December 9-11 2014