# ELMA MTCA.4 3rd MTCA Wokshop

**Aksel Saltuklar**

#### **Overview**

| System Solutions                                                           | Enclosures & Components         | Rotary Switches              |  |

|----------------------------------------------------------------------------|---------------------------------|------------------------------|--|

| Integrated Systems Chassis Platforms Backplanes Embedded Products Cabinets | Enclosures Front Panels Handles | Switches/Encoders Knobs LEDs |  |

## MTCA.4 crate news

- ➢ ELMA MCH INSTR

- Demonstration

#### MTCA.4 1U System platform

- 2x MTCA.4 front and rear slots

- Ix CPU slot

- 300 Watt single/redundant PSU

- Cooling unit pull // push pull

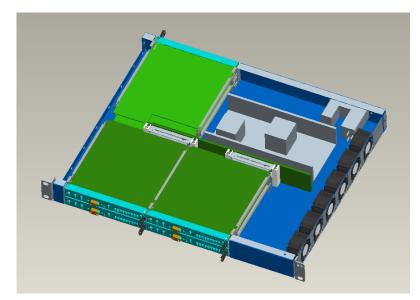

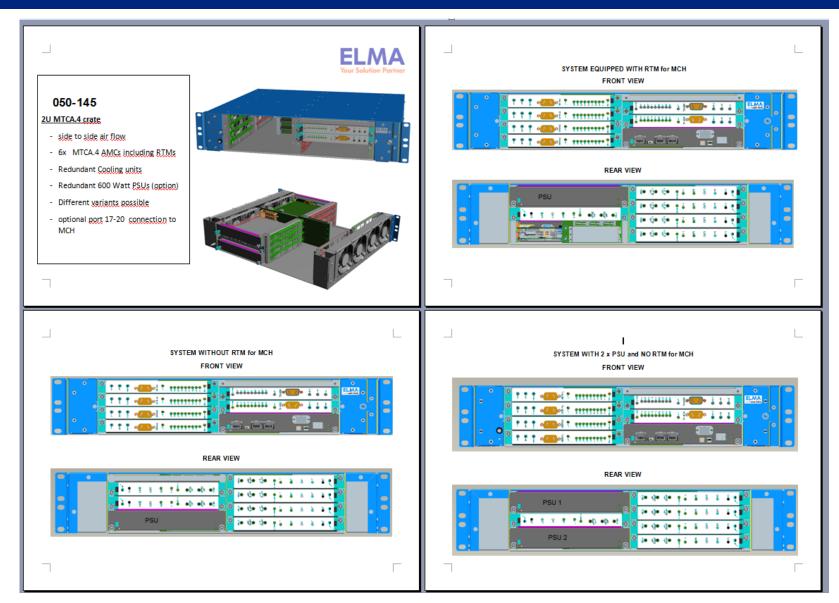

#### MTCA.4 2U System platform

• 6x MTCA.4 front and rear slots

- 600 Watt single PSU

- Cooling unit pull // push pull

#### MTCA.4 2U System platform

## MTCA.4 2U System platform

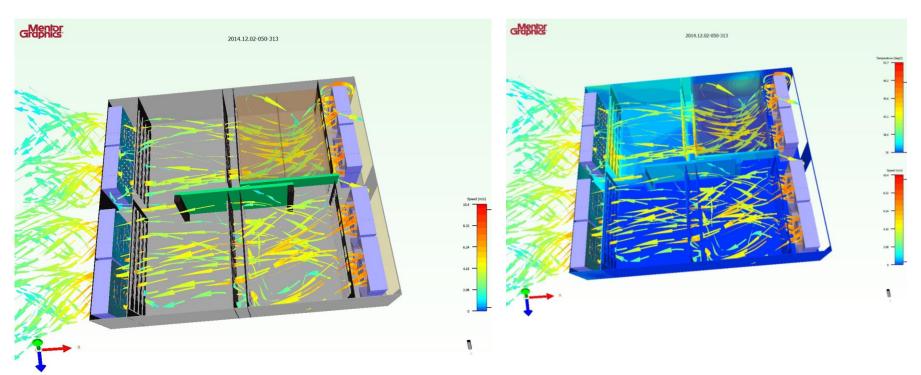

#### Temperature

#### Air flow rate

Main assembly

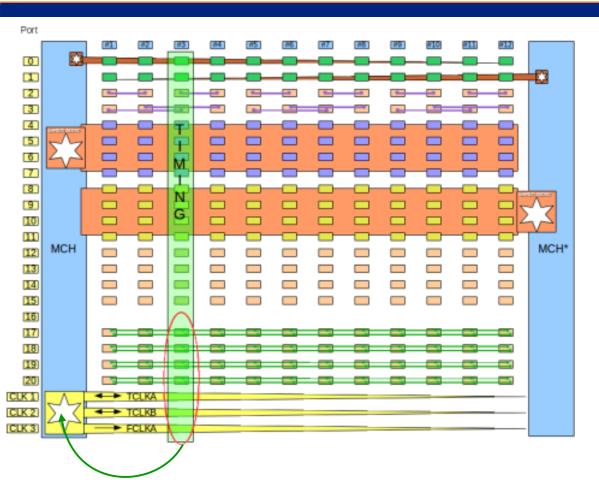

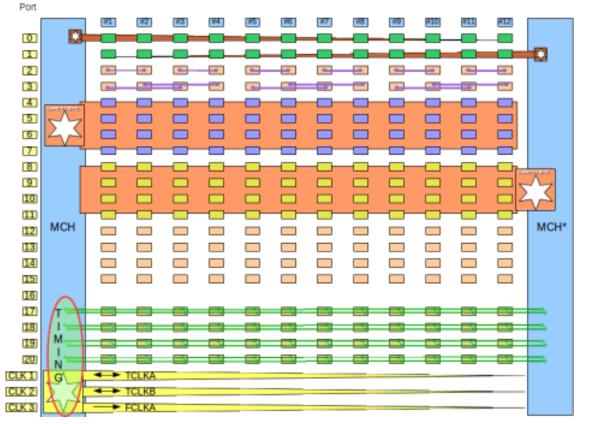

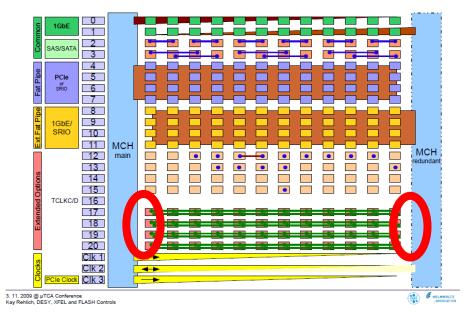

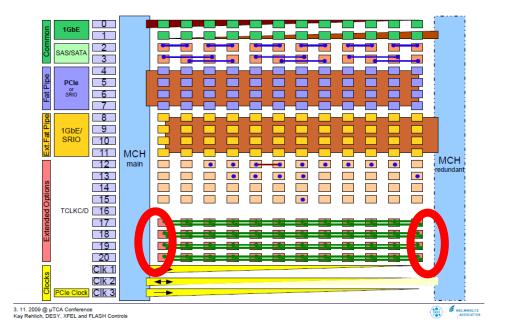

# The speciality of the ELMA MCH INST is, that the tongue 2 is a timing/syncroniation tongue based on an FPGA

Timing

**ELMA** Your Solution Partner

Each DAQ/Control System has timing

Clock signal recovered/generate in AMC slot send to MCH and then distributed – added jitter <sup>111</sup>

© Elma Group, 2011 www.elma.com

Timing integration into MCH

#### Reduced added jitter

Save slot for application

#### **Backplane variants**

#### 1x MCH

#### MTCA 6 slot crate

#### **XTCA-6 Slot**

•6 mid size double units in front and rear

•PSU 600W

#### MTCA 12 slot LLRF crate

#### MTCA 12 slot LLRF crate

ELMA

#### MTCA 12 slot PICMG crate

#### 2x redundand MCHs

2

#### JTAG communication

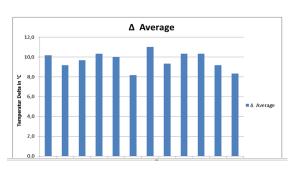

#### Temperature & airflow tests

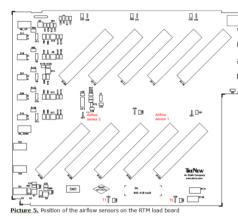

#### 7.Airflow measurements on each RTM Slot

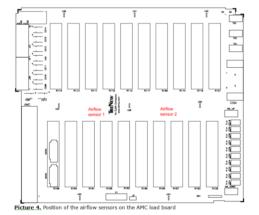

#### 4.Temperature measurement with 80W Load on each AMC

|        | Temp 1 | Temp 2 | Temp 3 | Temp 4 | Temp 5 | Temp 6 | Temp 7 | Temp 8 |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| AMC 1  | 31     | 30     | 44     | 56     | 49     | 37     | 48     | 37     |

| AMC 2  | 31     | 30     | 43     | 54     | 46     | 36     | 47     | 36     |

| AMC 3  | 31     | 29     | 44     | 56     | 48     | 36     | 48     | 35     |

| AMC 4  | 32     | 30     | 45     | 58     | 50     | 38     | 49     | 37     |

| AMC 5  | 33     | 31     | 45     | 60     | 51     | 39     | 49     | 38     |

| AMC 6  | 33     | 32     | 44     | 56     | 49     | 38     | 47     | 37     |

| AMC 7  | 30     | 30     | 42     | 56     | 49     | 38     | 48     | 37     |

| AMC 8  | 31     | 31     | 43     | 56     | 48     | 37     | 47     | 37     |

| AMC 9  | 30     | 30     | 43     | 57     | 48     | 37     | 47     | 37     |

| AMC 10 | 32     | 30     | 44     | 58     | 48     | 38     | 48     | 38     |

| AMC 11 | 31     | 30     | 44     | 57     | 49     | 37     | 46     | 36     |

| AMC 12 | 32     | 30     | 43     | 54     | 48     | 37     | 45     | 36     |

Table 2. Measurements results in °C

|        | Air speed on RTM Slots |              |             |

|--------|------------------------|--------------|-------------|

|        | Sensor 1 m/s           | Sensor 2 m/s | Average m/s |

| RTM 1  | 0,73                   | 1,2          | 0,97        |

| RTM 2  | 0,36                   | 1,67         | 1,02        |

| RTM 3  | 0,49                   | 1,57         | 1,03        |

| RTM 4  | 1,65                   | 1,54         | 1,60        |

| RTM 5  | 1,16                   | 1,15         | 1,16        |

| RTM 6  | 1,33                   | 0,56         | 0,95        |

| RTM 7  | 1,22                   | 0,9          | 1,06        |

| RTM 8  | 0,39                   | 1,77         | 1,08        |

| RTM 9  | 0,67                   | 1,81         | 1,24        |

| RTM 10 | 1,12                   | 1,74         | 1,43        |

| RTM 11 | 1,2                    | 0,82         | 1,01        |

| RTM 12 | 0,82                   | 1,34         | 1,08        |

Table 4. Airspeed measurements results in m/s

© Elma Group, 2011 www.elma.com

#### 11.12.2014

| Features at a glance                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

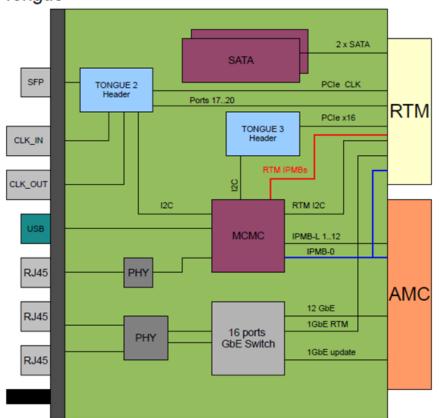

| Management                              | <ul> <li>For up to 12 AMCs, 12 uRTMs, up to 4 PMs, up to 2 CUs</li> <li>On-board Carrier manager</li> <li>CLI via Telnet or USB</li> <li>Firmware update via the front-panel USB or TFTP</li> <li>Web based GUI</li> <li>10/100 Ethernet management port that supports DHCP, RMCP, Telnet, HTTP and SNMP.</li> </ul>                                                                                                                                                                                                                                                                                                                                                      |  |

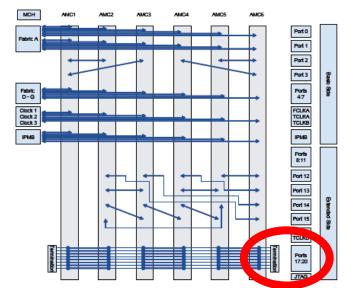

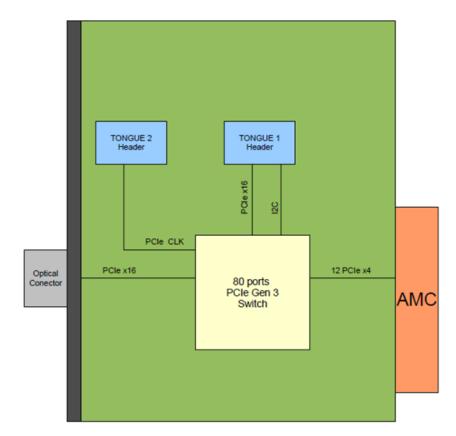

| Switches<br>Front Panel connec-<br>tors | <ul> <li>16 Port GbE switch Fabric A to 12 AMCs, 2<br/>front panel uplink ports and an update link to the<br/>second MCH slot</li> <li>FPGA based Clock Distribution: <ul> <li>Trigger distribution for ports 17 to 20 of the<br/>extended AMC backplane</li> <li>WhiteRabbit Clock Distribution (this synchro-<br/>nization protocol was developed by CERN<br/>and can be used to connect the MCH<br/>directly to the WhiteRabbit network )</li> <li>80 lanes, 20 port PCI Express Gen3 Switch<br/>(Gen3 backwards compatible to Gen 2 and<br/>Gen1) Fabric D-F to 12 AMCs (x4), x16 to RTM<br/>and x16 to the front panel optic uplink connector</li> </ul> </li> </ul> |  |

|                                         | <ul> <li>10/100 Ethernet Management port</li> <li>x16 fibre optic PCle uplink</li> <li>2x SMA: clock input and clock output for the clock distribution circuit</li> <li>SFP module for connecting to the Gigabit interface of the clock distribution module.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Storage                                 | • 2 x connectors for half size mSATA SSD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Compliance                              | Compliant to the following specifications:<br>• MTCA.0<br>• MTCA.1<br>• MTCA.4 R1.0,<br>• AMC.0 R2.0<br>• IPMI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

Tongue 1 (Base Tongue)

**Base Tongue**

- Management

- ✤ 16 port GbE switch

- Extern CLK's

- ✤ Storage

Tongue 1 (Base Tongue)

Tongue 2

#### Datasheet

#### **Description:**

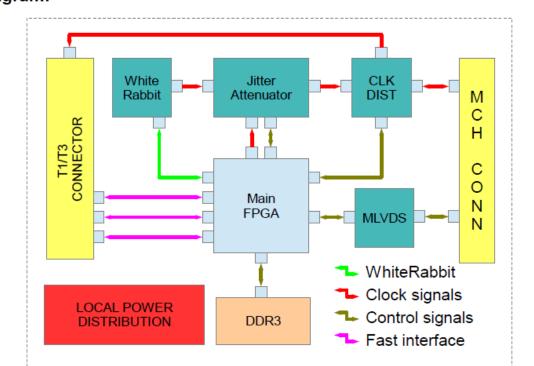

MCH Clock Board is a part of MCH module responsible for clock generation and distribution inside uTCA chassis. It extends capabilities of MCH base board and it is placed as a Tongue 2 of the whole module. It interfaces with clock distribution part of AMC backplane and passes all needed signals between Base Board, Tongue 3 and Tongue 4. The board is equipped with additional components and interfaces, which allow to implement advanced synchronization protocol handling (such as WhiteRabbit or IEEE1588)

Block Diagram:

11.12

#### Tongue 2

| Features                                |                                                                                                                                                                                                                                                                                                                                                            |  |  |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Processing Unit with<br>fast interfaces | Central device of the board is FPGA based processing and control which is used as a primary management device. It communicates with base board and receives configuration data for the whole clock distribut part and other peripherals. It plays the main role in an implementation synchronization protocols.                                            |  |  |

|                                         | The FPGA unit is connected with other Tongues with fast interfaces:                                                                                                                                                                                                                                                                                        |  |  |

|                                         | <ul> <li>Gigabit Interface to SFP module on the Base Board – the interface<br/>allows to connect module to synchronization or Ethernet networks.<br/>When combined with Ethernet link it can be the only connection to<br/>Ethernet network for the whole chassis.</li> </ul>                                                                              |  |  |

|                                         | <ul> <li>Ethernet switch on the Base Board – provides access to Ethernet<br/>network. It can be used either as an up-link or endpoint.</li> </ul>                                                                                                                                                                                                          |  |  |

|                                         | <ul> <li>PCle link to Tongue 3 and 4 – allows to map clock board into PCle<br/>tree of the root complex implemented in CPU board (either on RTM<br/>or any AMC slot). This allows to distribute events, timestamps and<br/>other information directly to software layer.</li> </ul>                                                                        |  |  |

| Trigger Distribution                    | The board is equipped with dedicated MLVDS buffers to control ports 17-<br>of extended AMC back-plane (for version with ports extended up to MC<br>slot). It can be a source or a receiver of the signals. The trigger signals ca<br>be decoded or coded locally by Main FPGA chip and the information<br>passed to RTM module plugged in behind RTM slot. |  |  |

Tongue 2

| Clock Distribution       | The clock distribution part is responsible for generation of two independent clocks for each slot in the chassis. The clock can be synthesized based on a local oscillator, front panel SMA input, clock form advanced synchronization interface or an input clock generated by AMC modules in the chassis. The subsystem also generates global PCle reference clock, which is distributed to the modules and RTM.     |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| WhiteRabbit              | The Clock Distribution part has been extended with the components required<br>by WhiteRabbit synchronization protocol developed by CERN. This creates<br>the possibility to connect the MCH directly to WhiteRabbit network. The<br>components can also be used for custom protocol implementations.<br>WhiteRabit (or other protocol) events can be forwarded to MLVDS bus and<br>distributed throughout the chassis. |  |

| Local Power Distribution | Local power distribution generates all local voltages based on single 12V power supply distributed throughout MCH tongues.                                                                                                                                                                                                                                                                                             |  |

| Management               | The firmware for main FPGA can be upgraded using several interfaces including USB, PCIe, ETH. All configuration memories are back buffered so the chance of damaging the board is minimal.                                                                                                                                                                                                                             |  |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

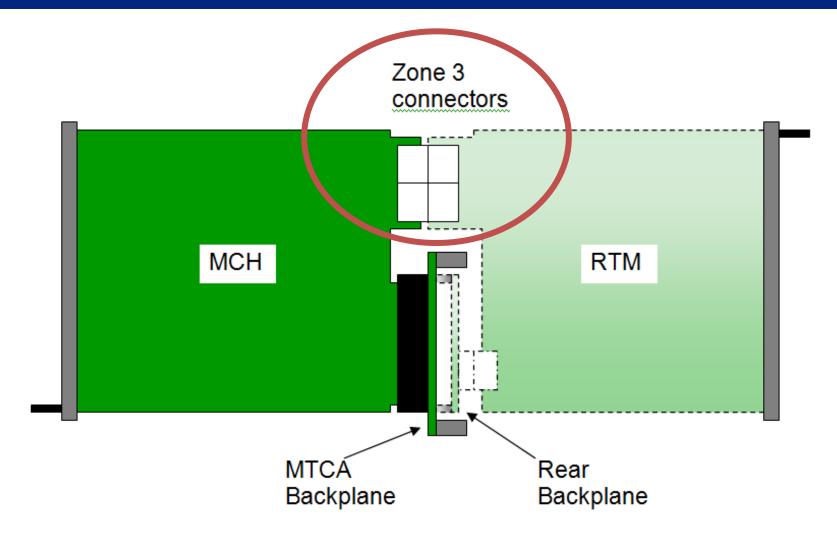

Tongue 3-4

PCIe gen3 switching

x4 PCIe links to 12 slots

x16 PCIe fiber optic uplink

x16 PCIe link to RTM

#### **Fiber optics**

# Fiber optics

11.12.2014

www.elma.com

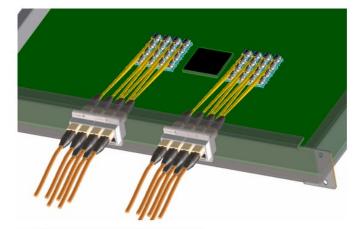

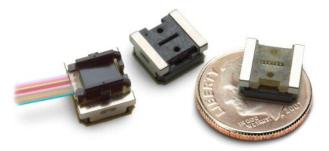

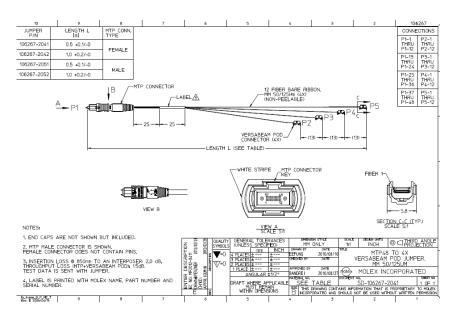

Figure 18. MiniPOD Modules Interfaced Through a 72 fiber Circular MT Connector

PCI-e gen3 fibre optic connection

Figure 15. Application of tiled MicroPOD modules in a high density switch

#### **Fiber optics**

#### **Optical Engine Technology**

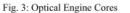

Fig. *3* shows several examples of optical engine cores from different companies. Note that I use the word *core* on purpose here: this is only part of the story. A complete, practically useable optical engine solution comprises of an electrical connector, an optical connector, a mechanical retention system, fiber stress relief and a heat-sinking solution. In practice, these extraneous elements are often much more important than the optical technology used in the core engine itself. Note that all these cores, despite using different technologies, look relatively similar. Differences will become more apparent when we consider the complete solutions in the next section.

Avago Micropod (x12)

Reflex Photonics (x12)

Luxtera (x4 bidirectional)

#### MicroPOD™ AFBR-77D1SZ, AFBR-78D1SZ

10 Gbps/Channel Twelve Channel Parallel Fiber Optics Modules

## **Fiber optics**

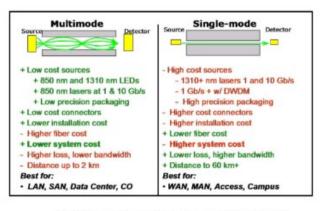

: Multimode vs. Single-Mode Fiber (source: Furukawa)

: MT ferrules and MTP® connector (source: US Coec)

Male and Female MTP Connectors with Bulkhead Connector

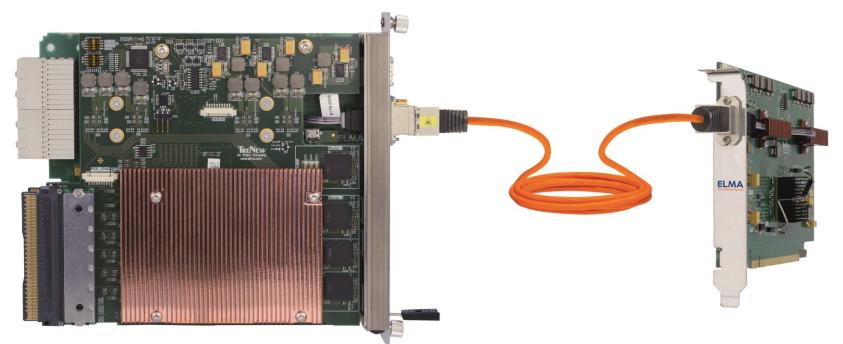

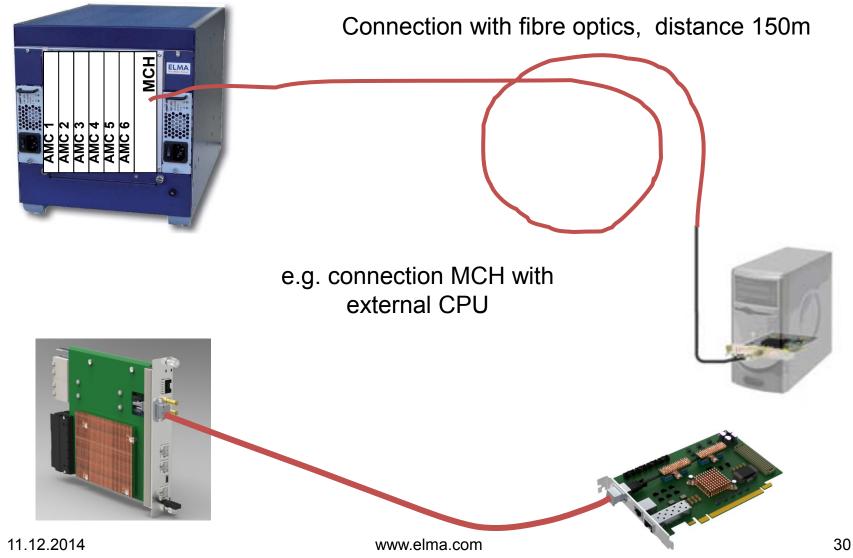

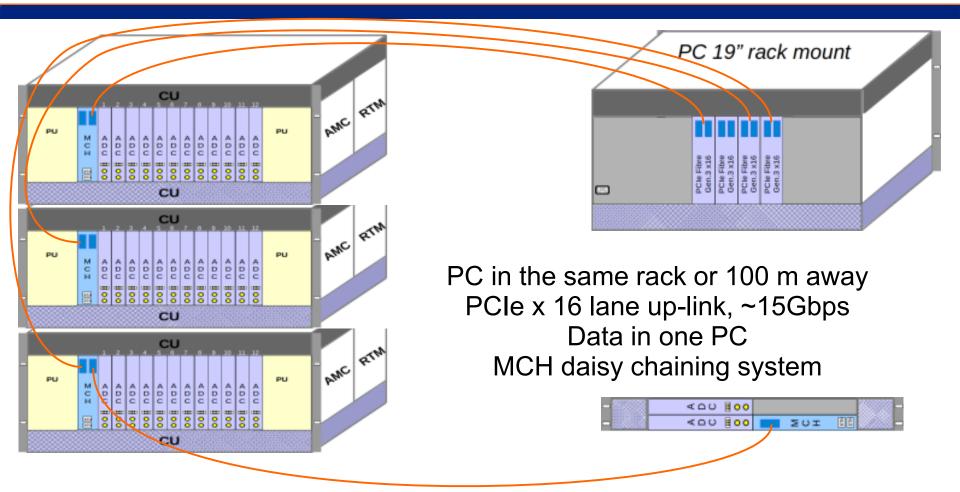

#### **ELMA-MCH-INSTR** and **PC BOARD**

- External, powerful PC might be connected to several MTCA.4

- Distance between PC and chassis (field &office) is possible

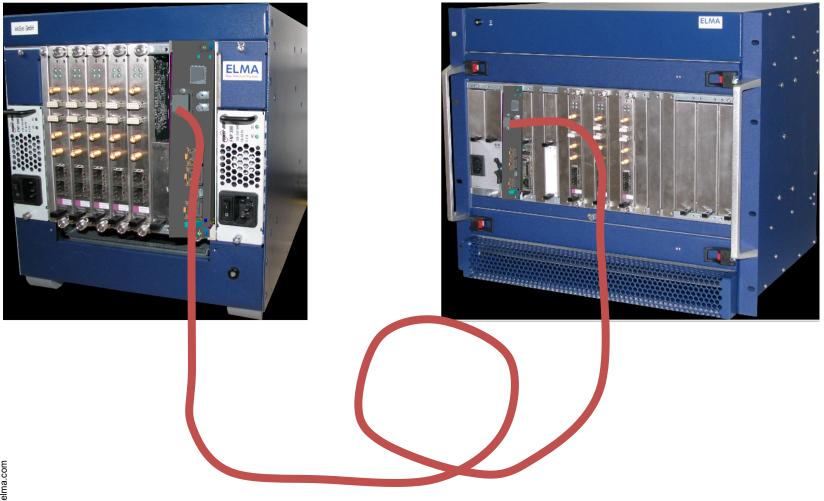

Daisy chain between MTCA.4 system possible

#### ELMA Your Solution Partner

#### **Fiber optics**

#### Daisy chaning several MTCA.4 crates

#### Using several MTCA.4 crates

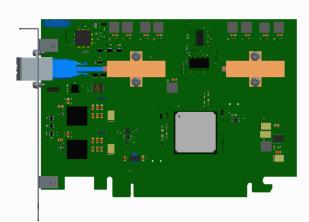

## 050-395 PCI-express PC board

#### PCIe PC Board

The PCI Express PC Board provides a nonblocking switching architecture that serves as bridge

between a Personal Computer and a MTCA system. The board uses a PEX8748 chip that is fully compliant with the PCI Express Base Specification r3.0, and backwards compatible to older PCI Express Base Specifications.

The interfaces consists of two x16 links: one to the PC, and one to the MCH.

By default, the PC link is designated as the upstream port, but the MCH can also be set up as the root complex.

The second configuration is used to connect together two MCHs. The board uses a standard PCIe card format and can be plugged in any x16 main board PCIe slot.

The PC board could operate also in x8, x4, x2 or x1 mode. The PCIe PC Board has an optical connector on the front panel,

that supports an external PCIe x16 optical connection. The optical interface uses 4 Avago MicroPOD,

12 channels parallel fiber optic modules. The external optical PCIe connection could be configured as a single x16 upstream link or as two x8 upstream, which could allow connection to two MTCA systems.

www.elma.com

11.12.2014

#### Thank you for your attention.