# Optimizing the built-in amplifier in HV-CMOS CHESSI

Vitaliy Fadeyev, Zach Galloway , Herve Grabas Alexander Grillo , Zhijun Liang , Abe Seiden Jennifer Volk, Forest Martinez-Mckinney

University of California, Santa Cruz

## Isolated amplifier in CHESSI chip

- HV-CMOS CHESSI chip has built-in isolated amplifiers

- designed to optimize amplifier performance

- Six amplifier biasing control

0

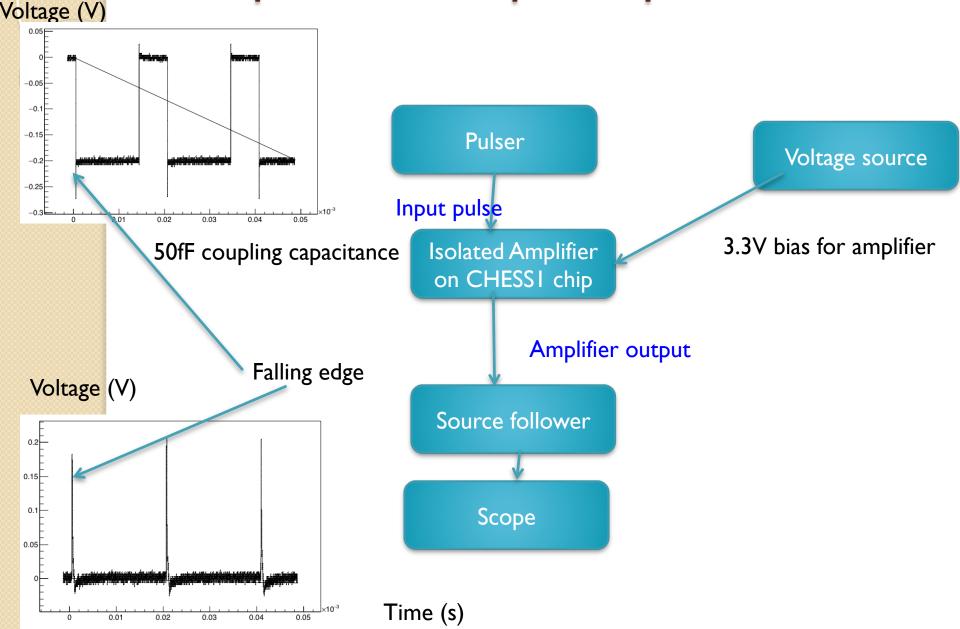

- Optimization can be done with pulser, without using laser injection or beta source.

- Change its gain and output signal shape by changing biasing control

- Try to study the amplifier performance as input to CHESS2 design

| Pad number | Pad name | Value |

|------------|----------|-------|

| 1          | iN       | 65µA  |

| 2          | Casc     | 2.4V  |

| 3          | VPload   | 1.85V |

| 4          | iBias    | 7nA   |

| 5          | iFB      | 2nA   |

| 6          | iNSF     | 20nA  |

Table 3.4-e: Fast Amplifier Biasing for optimum performances

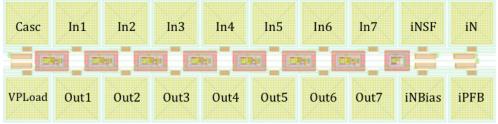

#### 3.5. Isolated Fast Amplifier

An array of 7 isolated fast amplifiers circuits is included with an input and out pad. This is to separately test the characteristics of the amplifier in order to separate its characteristics and their evolution with radiation from that of the passive pixel sensors. The amplifier used is the same as the one included in the active pixel array. However instead of being capacitively coupled to the nwell they are capacitively coupled to the input pad. Multiple copies of the amplifier are included to allow testing of matching of amplifiers in close proximity to each other. It will also allow comparing the performance of amplifiers on several of the test chips available to test similar matching across a wafer.

Figure 3-4: Layout of the isolated fast amplifiers.

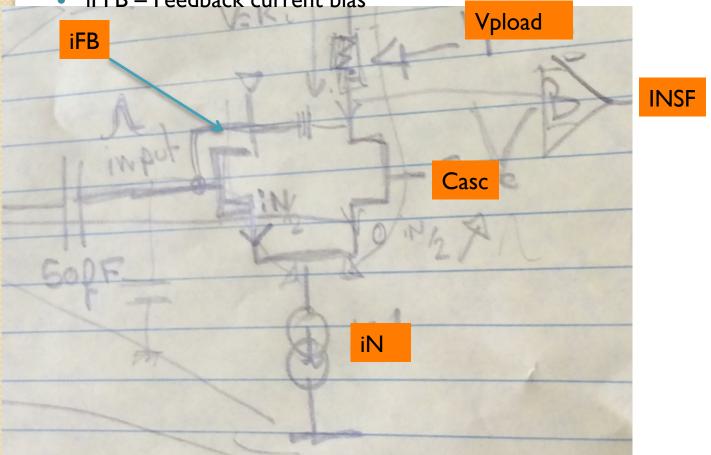

## **Amplifier Biasing**

- Casc -Cascode bias

- iNSF Source Follower Bias

- iN Amplifier current source bias

- VPLoad Amplifier Resistive Load bias

- iNBias Nwell resistive path bias

- iPFB Feedback current bias

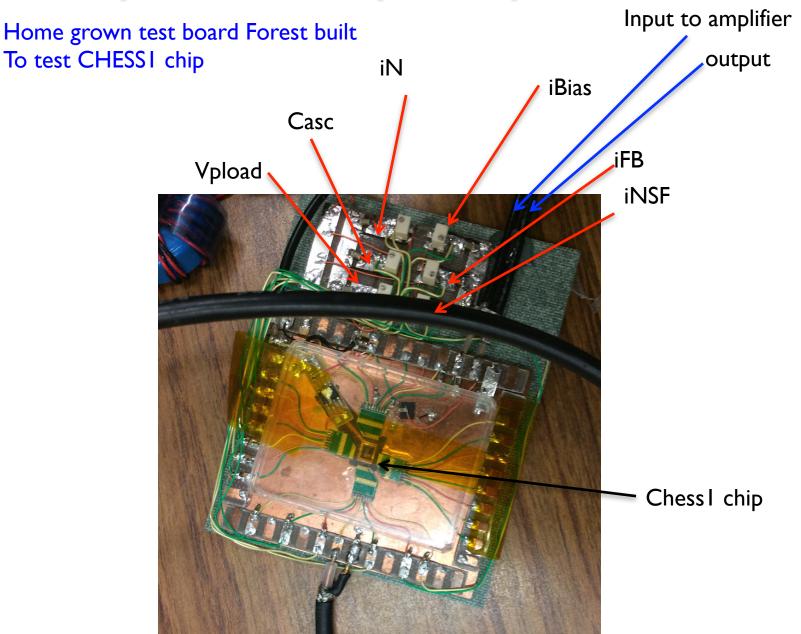

## Setup to test amplifier performance

## Setup to test amplifier performance

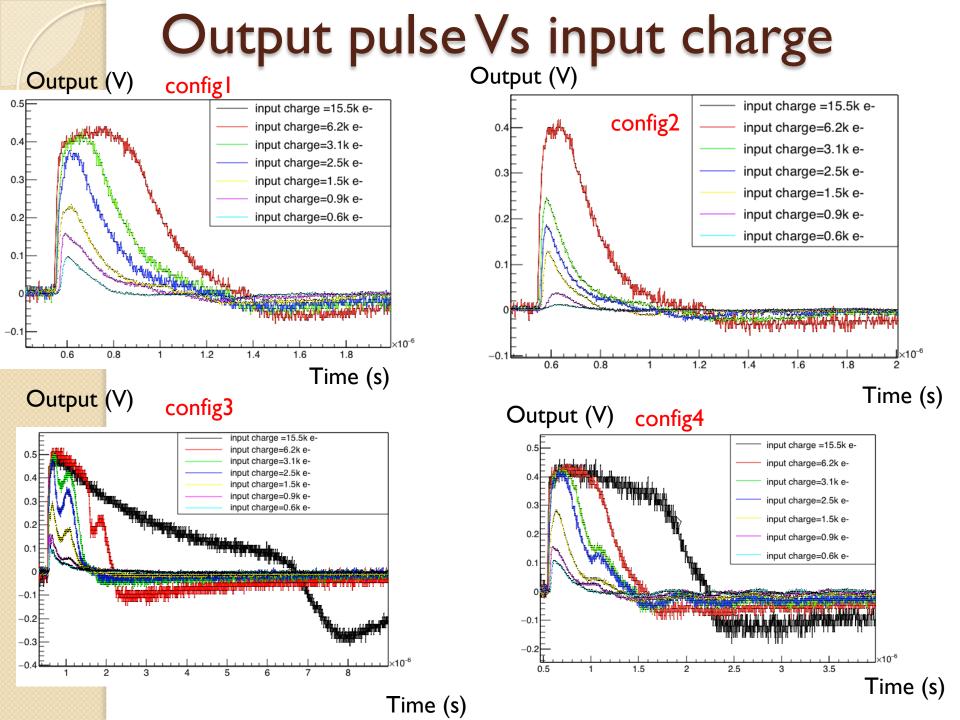

## 4 configuration of amplifier setting

- Keep iBias, Cacs, Vpload, iN constant

- iBias=0.34V. Cacs =2.6V, Vpload=2.1V, iN=1.4

- Varying iFB and iNSF to optimize the performance

### • Config1:

- iFB=2.664V, iNSF=0.569V

- Config 2

- iFB=2.597V,iNSF=0.576V

- Config 3

- iFB=2.71V,iNSF=0.766V

- Config 4

- iFB=2.682V,iNSF=0.566V

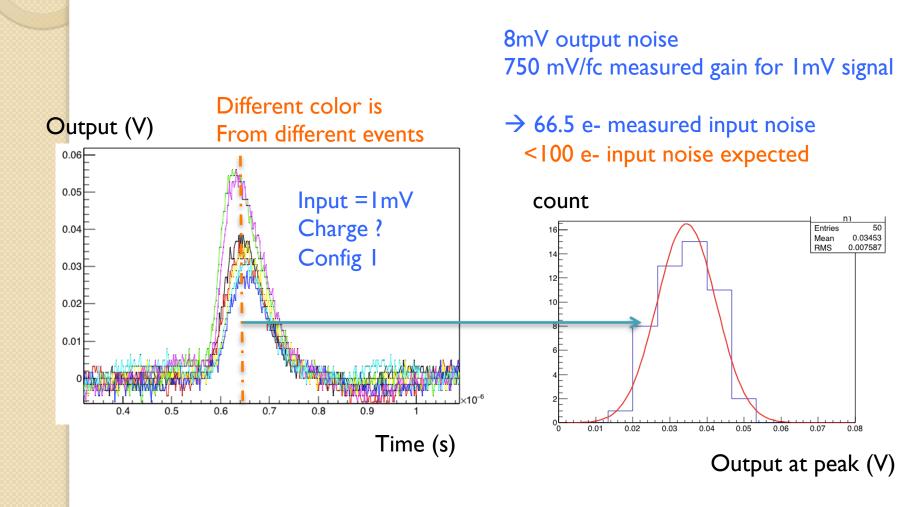

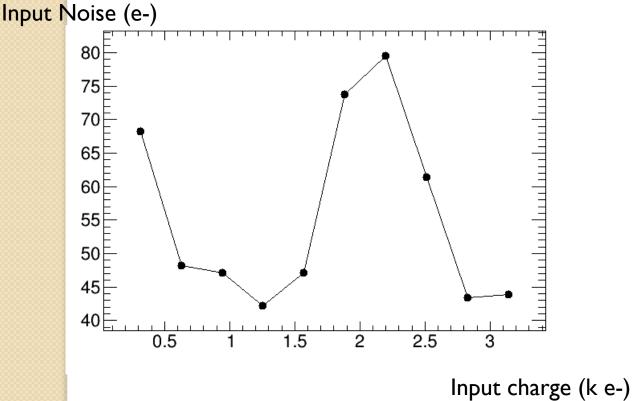

## **Amplifier Noise**

• Noise of the amplifier (upper limit) can be estimated by measuring the event-by-event variation in signal peak

## **Amplifier Noise**

• Input Noise : 40~80 e- (<100 e- expected)

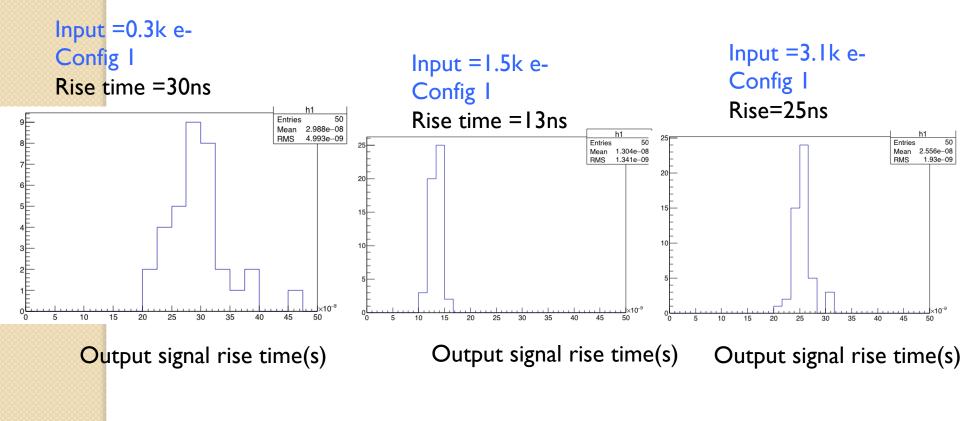

## Amplifier output signal rise time

- Pulser input signal has 9ns rise time

- Amplifier output Rise time (10%-90%) vary between 13ns 30ns

- Depending on the input signal amplitude

## Amplifier output signal rise time

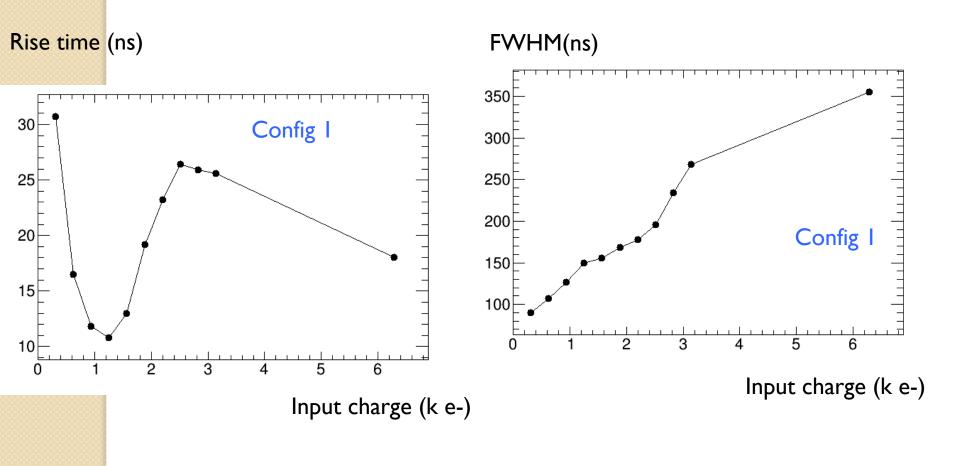

- Rise time : 10~30 ns depending on signal size

- Full width at half maximum is from 80ns ~360ns depending on signal size.

## Summary

first exercise on optimizing the built-in CMOS based amplifier in CHESS1 chip

- As input to CHESS2 active array design

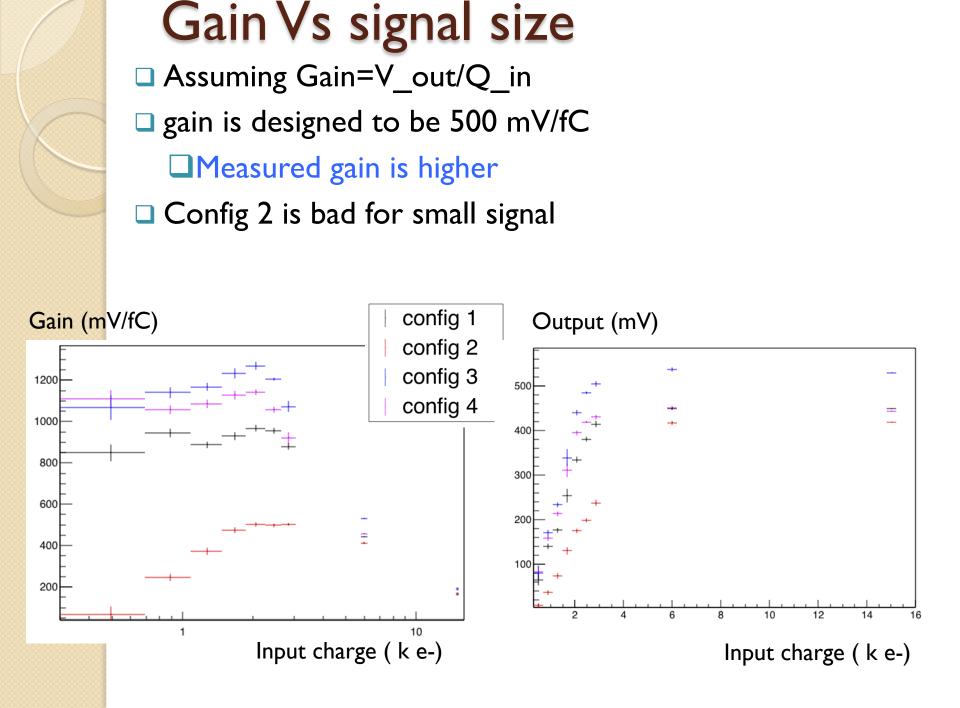

- Measured Amplifier performance

- Gain : 500 ~ 1300mV/fC ( 500 mV/fc is expected)

- Input Noise : 40~80 e- (<100 e- expected)</li>

- Input noise is good

- But It is measured in isolated amplifier without sensor

- It may be nosier in real detector

- Rise time : 10~30 ns depending on signal size (15ns expected)

- Full width at half maximum is from 80ns ~360ns depending on signal size.

- Configuration I gave the best performance

- Best balance between gain and output signal shape.

- iBias=0.34V. Cacs =2.6V, Vpload=2.1V, iN=1.4

- iFB=2.664V, iNSF=0.569V

- Next steps:

•

- Try to reduce power consumption by reducing Amplifier current source bias(iN)

- Study signal to noise using laser injection in active pixel array