# Cryring BPM

Development of MicroTCA.4 bunch position measurement system for Cryring@ESR

P. Miedzik, H.Bräuning, T. Hoffmann, W. Kaufmann, A. Reiter, R. Singh

## **Agenda**

- Motivation

- Base platform

- MMC firmware

- Beam Position Monitor

- Tools

- Summary

#### **Motivation**

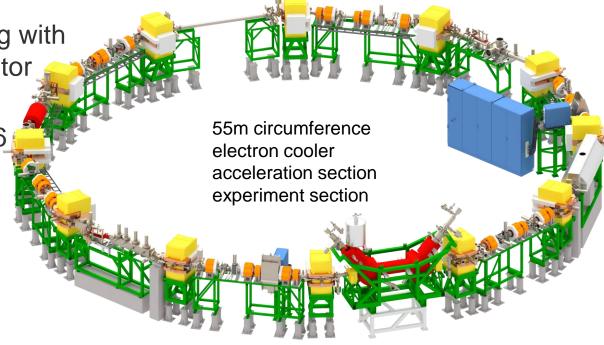

Experimental storage ring with new bunch position monitor \_\_\_

system (8X + 8Y)

Commissioning mid 2016

AMC/MicroTCA.4

ANSI/VITA FMC

WhiteRabbit timing

Front-end software architecture (FESA)

CRYRING@ESR

the heavy ion storage ring

formerly located at

Stockholm University,

Swedish in-kind contribution to FAIR

#### **Base platform**

2013-01-28

Platform ordered

2013-02-28

Expected hardware delivery

2014-12-10

Arrived to GSI

2015-03-02

Position calculation algorithm tests with hardware

2015-06-15

Tests and design verification finished

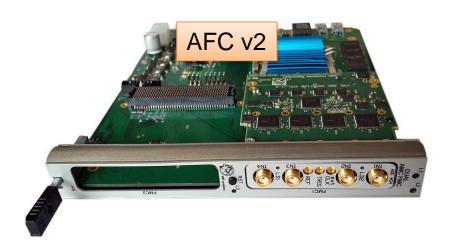

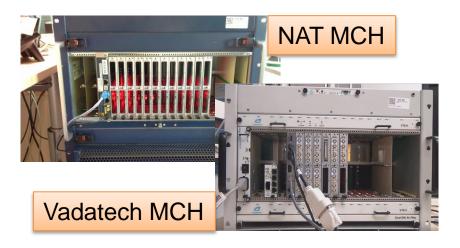

- 8U MicroTCA.4 chassis (VT811)

- 500W power supply (UTC017)

- MCH Vadatech (UTC002)

- CPU Concurrent (AM 902/411)

- 6x AFCv2

- 9x FMC ADC 250M 16b 4cha

- 1x FMC DIO32

#### **Work Order**

- MMC (Module Management Controller)

- 2. HDL design improvements

- ADC initialization

- DDR3 memory

- PCI Express

"There's only one way to do the job, the right way. My way\*"

Gus

\*Includes collaboration

#### **MMC - Existing implementations**

- Original AFCv2 firmware (LPC1764)

- CoreIPM (LPC2368, MSP430)

- University of Wisconsin (UC3A1512)

- DESY (ATxmega128A1)

- DESY/CERN (ATmega128)

- Vadatech (32bit RISC ???)

- N.A.T. (ATxmega128A4U)

- Kontron (LPC2136)

- •

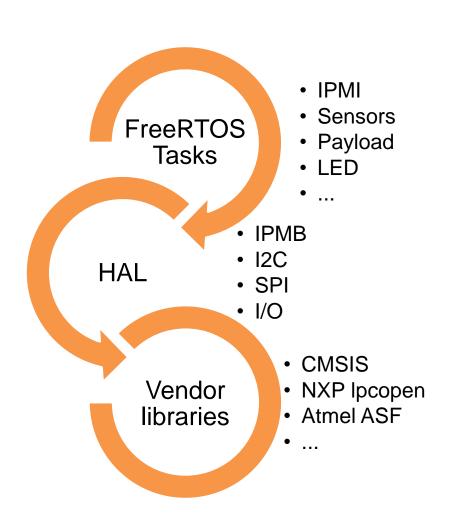

## **MMC** - firmware requirements

- Reliable

- Portable

- RTOS based

- Extendible

- sensors and drivers

- New OEM commands without any modification to MMC core

- Additional user task

- Community based development model

- GSI (Germany)

- Creotech (Poland)

- Warsaw University of Technology

- LNLS (Brazil)

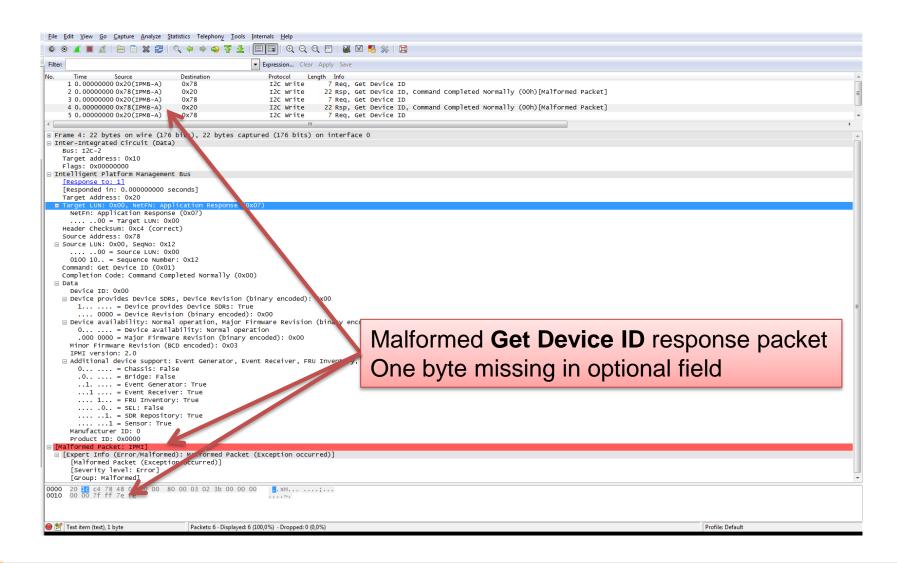

- IPMI debug channel to Wireshark

## MMC – architecture comparison

|                        | Cortex-M3     | AVRxmega                       |

|------------------------|---------------|--------------------------------|

| Architecture           | 32bit         | 8bit                           |

| Bit Band regions       | 1MB + 1MB     | Partial                        |

| Internal RAM           | Up to 512MB   | Up to 56KB                     |

| External RAM           | Up to 1GB     | Up to 16MB                     |

| Memory space           | Unified       | Two (Flash/Data)               |

| Multiple stacks        | Yes (MSP/PSP) | No                             |

| SVC/PendSV             | Yes           | No                             |

| System Timer           | Yes           | No                             |

| Memory Protection Unit | Optional      | No                             |

| Bootloader protection  | No            | Yes                            |

| Used by                | Advantech     | N.A.T., DESY,<br>CERN(AVRMega) |

<sup>\*</sup>ARM7 is used by denx-cs, CoreIPM, kontron, and many other

#### MMC - added features

- IPMI

- requests triggers handlers with well known API

- stored as table of pointers (created during linking stage)

- Sensors

- array of sensors with pointers to callbacks

- FRU

- stored as array of chars

- created with external tool

- replace without recompilation

- Payload

- power sequence different for each board

- Replaceable User Tasks and IPMI

## **MMC** - supported boards

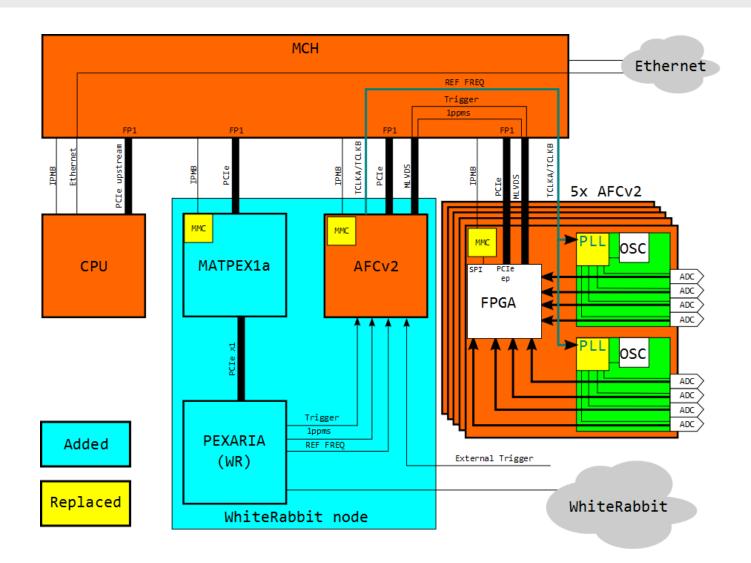

#### **BPM DAQ - crate setup**

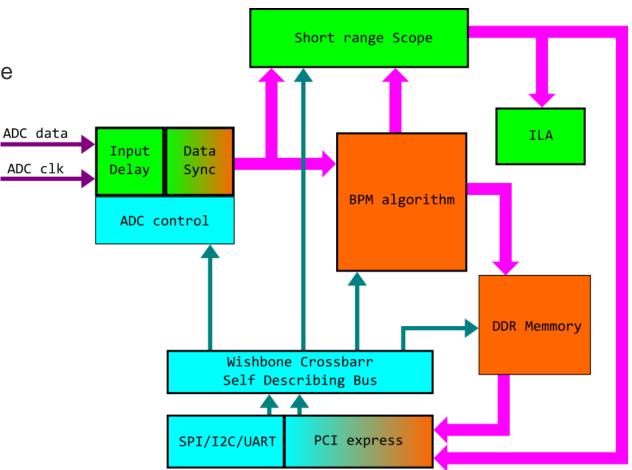

## **BPM DAQ – HDL block design**

- AMC/MicroTCA.4 features:

- TCLK: ADC reference frequency

- MLVDS: Trigger / Interlock

- Wishbone + SDB

- Two masters

- UART

- SPI

- I2C

- PCI-Express

- Separate path for processing data

- Short range scope mode

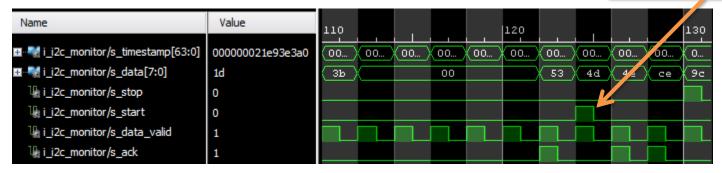

# Tools developed IPMI and I2C sniffer

- RedPitaya based standalone sniffer for arbitrary

- IPMI logs channel over UART

- Operation modes:

- Logic analyzer

- Wireshark

RedPitaya board

Reapeated start

Logic analyser view

# Tools developed IPMI and I2C sniffer – Wireshark mode

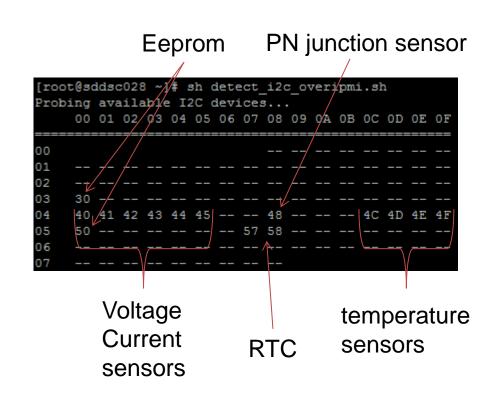

# Tools developed ipmitool wrappers

- I2C

- i2c transfer

- i2c detect

- SPI

- SPI/Flash reader/writer

- Wishbone access

- DPRAM access

- IO

- MMC IO state view and change

- clock resources configurator

- ADC board initialize

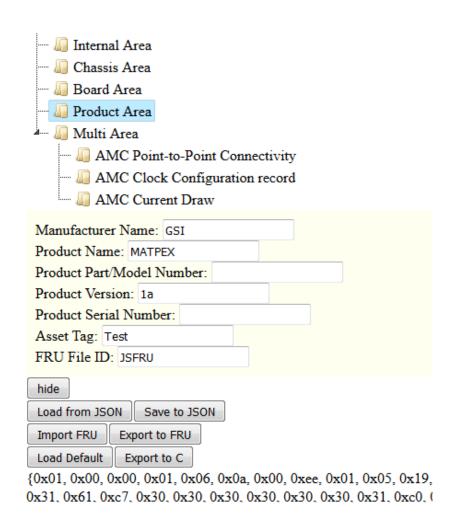

# Tools developed FRU editor

- HTML5 and JavaScript based

- Data import/export

- binary

- JSON

- C array (export only)

- Allows to define:

- Internal Area

- Chassis Area

- Board Area

- Product Area

- AMC Current Draw

- AMC Point-to-Point connectivity

- AMC Clock Configuration record

- FMC and RTM FRU support planned

#### **Project summary**

#### Finished:

- MMC IPMI

- System hardware delivered

- AFC Master board firmware

- WhiteRabbit timing node prototype

#### TODO:

- AFC ADC boards firmware (FPGA)

- DDR3 memory IP Core (FPGA)

- PCI Express IP Core (FPGA)

- Safe firmware upgrade (MMC)

- Flexible build system (MMC)

- FESA class and data acquisition software