# MTCA.4-based LLRF control system experience at ELBE

Igor Rutkowski with a lot of help from DESY, HZDR, ISE, TUL

Institute of Electronic Systems Warsaw University of Technology

25.11.2015

# Outline

- Project description

- System architecture

- 3 Tests

- 4 Outlook

- Project description

- System architecture

- Tests

- 4 Outlook

Project description System architecture Tests Outlook

#### Briefly

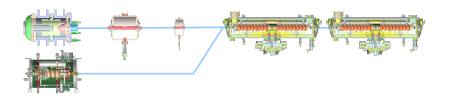

Setup MTCA.4-based single cavity regulation system at the ELBE facility.

#### Goals

- Prepare a robust solution for the CW operation.

- Develop a MTCA.4-based LLRF control system suitable for external users.

- Minimize the maintenance effort needed.

- Increase the flexibility.

- Project description

- System architecture

- Tests

- 4 Outlook

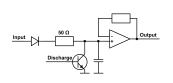

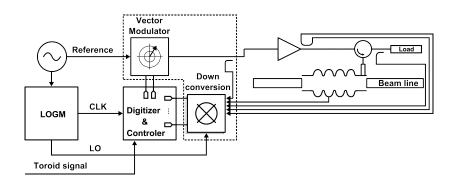

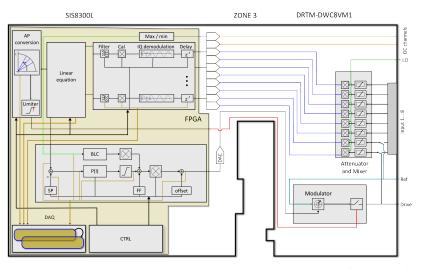

## Real-time FB Loop Overview

# Hardware platform

#### Control loop - main components (per cavity)

- DRTM-DWC8VM1 / DRTM-DS8VM1

- Struck SIS8300L2

#### Other components

- MTCA.4 Crate

- CPU

- Power Supply

- Timing module

- MCH

#### External

- LO Generation Module (LOGM)

- ICT signal conditioning front-end

- Timing system

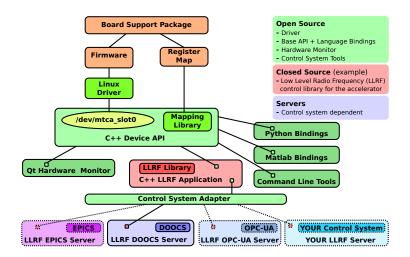

#### <u>Firmware</u>

#### Software

Courtasy of Martin Killenberg.

- Project description

- System architecture

- 3 Tests

- 4 Outlook

#### Test runs

#### November 2013

- First experience

- Integration isssues (Timing)

- Cavity 3 and 4

#### 2014

- Cavity 1 and 2

- 260 MHz buncher

- Performance optimization

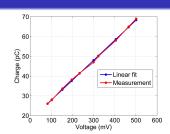

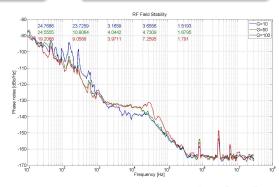

Gradient:  $10.5 \frac{MV}{m}$ Beam current: 800 uA

| Gain (A.U.) | Jitter (fs) |

|-------------|-------------|

| 10          | 34.67       |

| 50          | 27.59       |

| 100         | 22.86       |

Reference jitter: 21.2 fs

# Test runs (cont.)

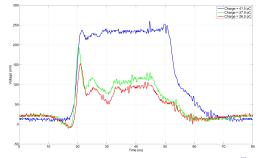

#### 2015

- Real-time BLC

- Automation (server, close loop ramp up procedure)

- Focus on the system integration

#### Common problems

- Phase Alignment

- Warm and Cold Windows Interlock

- Timing signal

- MTCA management and OS configuration (RTM CPU issues)

#### Small mistake with big consequences (Nov 9th 2015)

- Error in communication

- Wrong gradient

- Beam on (CW)

- Below beam loss interlock treshold

- Vaccum broken

- Project description

- System architecture

- Tests

- 4 Outlook

#### Most important todos

- Control system adaptor

- Interlock integration

- Timing

- UNILOGM (Q1 2016)

#### Other tasks

- DAQ

- Real-time BLC

- New diagnostic and automation

roject description System architecture Tests **Outlook**

# Questions

# Backup slide - BLC