# Preparations for PXD9 Module Testing

### Philipp Leitl

phleitl@mpp.mpg.de

Max Planck Institute for Physics Munich

Bi-weekly PXD Meeting 10th of January 2017

Max-Planck-Institut für Physik (Werner-Heisenberg-Institut)

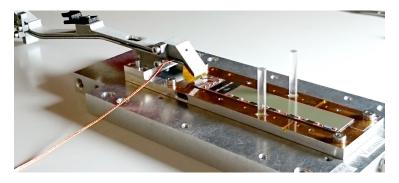

## **Probe Card**

First module tests will be done before kapton attachment with needle cards.

Design A: IF, OB modules  $\rightarrow$  ready and tested at HLL

Design B: IB, OF modules  $\rightarrow$  design ready, fabrication and assembly ongoing

# After Kapton Attachment

The production of the module is now finished, no rework foreseen any longer.

The modules will be tested again to ensure that the kapton attachment was successful (no shorts, no cracks introduced).

But the main task is the **characterization** of the modules: find the optimal settings, make a performance grading, choose the best modules for the PXD.

# Configuration Database

Optimal settings (all PVs) are stored in the configuration database:

- new "file" for the PXD9 production modules

- own "branch" for each module (e.g. W31\_OB1)

- module specific values can easily be reloaded later by just one number: commitid

### **Production Database**

Test results as well as grading to be stored in the **production database**: grading criteria not yet defined! more experience / statistics needed!

Meeting with Marca, Manfred and Pablo about checklist and grading in the DB.

### Suggestion:

percentage grading 100 % for ideal resulsts deductions for failures

- DHPT link stability

- ratio of working pixels

- pedestal spread

- ADC transfer curves (INL, DNL, gain, noise)

- signal to noise

- clear efficiency

- gated mode (turn on/off time, relaxation time)

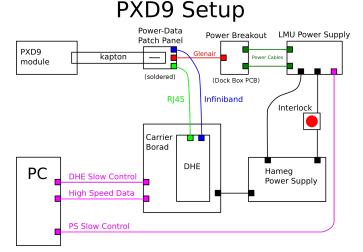

# Test Setup

- setup close to final configuration

- (no DHC, still DHE Carrier Cards)

- final PS, PS cables, Patch Panel, dockbox PCB

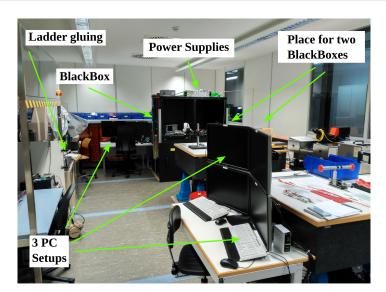

# Required Hardware for 4 Setups

We are currently building 4 setups for parallel working (2 modules, 1 ladder). Only few missing parts:

- new blackboxes (parts were delivered, will be painted black)

- new Patch Panels (first prototyps were debugged and used with new W31 modules)

- Cd source and Laser (already delivered, not yet installed)

- motorstage

spreadsheet: PXD9 Pilot Run/EMCM Setup

# Setups so far

## **Actual Tests and Characterization**

#### planned tests

- powerup and JTAG configuration, voltage sanity check (digital, analog, matrix)

- JTAG Boundary Scan

- DHPT link parameters "Aurora Scan"

- DHPT DCD communication "Delay Scan"

- pedestals (bit map working pixels)

- ADC transfer curves

- 2bit offset DACs

- sample point

- DEPFET optimization without source

- DEPFET optimization with source (Cd-109)

- clear efficiency

- gated mode

#### time estimate

- 10 min

- 10 min

- 30 min

- 20 min

- **3**0 min

- 270 min

- 60 min

- 60 min

- 30 min

- 120 min

- 60 min

- 60 min

$\sim$  14 h per module