## UBC STATUS UPDATE

# Previously...

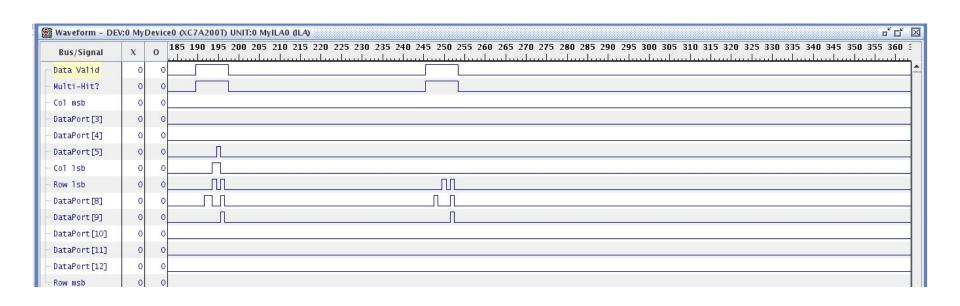

### Enable Comparator on All Pixels: 0.758 A

All Data goes to zeroes, which is what we expect

| Bus/Signal    | х | o 230 | 235 | 240 | 245 | 250 | 255 | 260 | 2 <b>6</b> 5 | 270 | 2 <b>7</b> 5 | 280 | 2 <b>8</b> 5 | 2 <b>90</b> | 2 <b>9</b> 5 | 300 | 3 <b>0</b> 5 | 310 | 315 |  |

|---------------|---|-------|-----|-----|-----|-----|-----|-----|--------------|-----|--------------|-----|--------------|-------------|--------------|-----|--------------|-----|-----|--|

| — Data Valid  | 0 | 0     |     |     |     |     |     |     |              |     |              |     |              |             |              |     |              |     |     |  |

| - Multi-Hit?  | 0 | 0     |     |     |     |     |     |     |              |     |              |     |              |             |              |     |              |     |     |  |

| -Col msb      | 0 | 0     |     |     |     |     |     |     |              |     |              |     |              |             |              |     |              |     |     |  |

| - DataPort[3] | 0 | 0     |     |     |     |     |     |     |              |     |              |     |              |             |              |     |              |     |     |  |

| DataPort[4]   | 0 | 0     |     |     |     |     |     |     |              |     |              |     |              |             |              |     |              |     |     |  |

| DataPort[5]   | 0 | 0     |     |     |     |     |     |     |              |     |              |     |              |             |              |     |              |     |     |  |

| Col 1sb       | 0 | 0     |     |     |     |     |     |     |              |     |              |     |              |             |              |     |              |     |     |  |

| Row 1sb       | 0 | 0     |     |     |     |     |     |     |              |     |              |     |              |             |              |     |              |     |     |  |

| — DataPort[8] | 0 | 0     |     |     |     |     |     |     |              |     |              |     |              |             |              |     |              |     |     |  |

| DataPort [9]  | 0 | 0     |     |     |     |     |     |     |              |     |              |     |              |             |              |     |              |     |     |  |

| DataPort[10]  | 0 | 0     |     |     |     |     |     |     |              |     |              |     |              |             |              |     |              |     |     |  |

| DataPort[11]  | 0 | 0     |     |     |     |     |     |     |              |     |              |     |              |             |              |     |              |     |     |  |

| DataPort[12]  | 0 | 0     |     |     |     |     |     |     |              |     |              |     |              |             |              |     |              |     |     |  |

| Row msb       | 0 | 0     |     |     |     |     |     |     |              |     |              |     |              |             |              |     |              |     |     |  |

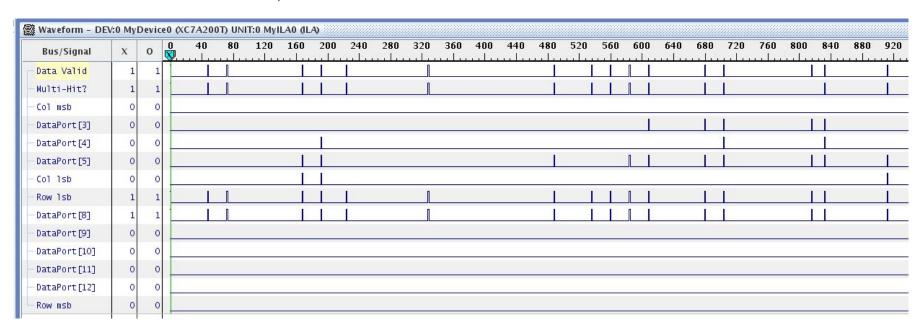

### Enable Test Mode: 0.758 A

However, test mode doesn't appear to work

| Bus/Signal    | x | o 230 | 235 | 240 | 245 | 250 | 255<br> | 260 | 2 <b>6</b> 5 | 270 | 275 | 280 | 285 | 290 | 2 <b>9</b> 5 | 300 | 305 | 310 | 315 |  |

|---------------|---|-------|-----|-----|-----|-----|---------|-----|--------------|-----|-----|-----|-----|-----|--------------|-----|-----|-----|-----|--|

| Data Valid    | 0 | 0     |     |     |     |     |         |     |              |     |     |     |     |     |              |     |     |     |     |  |

| Multi-Hit?    | 0 | 0     |     |     |     |     |         |     |              |     |     |     |     |     |              |     |     |     |     |  |

| Col msb       | 0 | 0     |     |     |     |     |         |     |              |     |     |     |     |     |              |     |     |     |     |  |

| DataPort[3]   | 0 | 0     |     |     |     |     |         |     |              |     |     |     |     |     |              |     |     |     |     |  |

| DataPort[4]   | 0 | 0     |     |     |     |     |         |     |              |     |     |     |     |     |              |     |     |     |     |  |

| DataPort[5]   | 0 | 0     |     |     |     |     |         |     |              |     |     |     |     |     |              |     |     |     |     |  |

| Col 1sb       | 0 | 0     |     |     |     |     |         |     |              |     |     |     |     |     |              |     |     |     |     |  |

| Row 1sb       | 0 | 0     |     |     |     |     |         |     |              |     |     |     |     |     |              |     |     |     |     |  |

| DataPort[8]   | 0 | 0     |     |     |     |     |         |     |              |     |     |     |     |     |              |     |     |     |     |  |

| DataPort [9]  | 0 | 0     |     |     |     |     |         |     |              |     |     |     |     |     |              |     |     |     |     |  |

| DataPort[10]  | 0 | 0     |     |     |     |     |         |     |              |     |     |     |     |     |              |     |     |     |     |  |

| DataPort[11]  | 0 | 0     |     |     |     |     |         |     |              |     |     |     |     |     |              |     |     |     |     |  |

| DataPort [12] | 0 | 0     |     |     |     |     |         |     |              |     |     |     |     |     |              |     |     |     |     |  |

| Row msb       | 0 | 0     |     |     |     |     |         |     |              |     |     |     |     |     |              |     |     |     |     |  |

## Disable Comparator on All Pixels: 0.830 A

If we disable comparators, we begin to get back data

### Test Mode Enable Row 3

Row data is correct, column data is still bad and multi-hit is still on

### Since then:

- We got test mode to work properly by cutting the 320/40MHz clocks in half to 160/20MHz

- However this throws off the timing in the rest of the firmware, which is what we ultimately want to debug

- We decided to set up the SLAC firmware and use it to debug CHESS-2

# Reasoning behind using SLAC carrier/firmware:

- We will have access to all 3 pixel arrays (perhaps the one we have access to is broken, but the others are working)

- We can check if somehow our setup/configuration is not working

- Did cross check against defaults.yml

# Building the firmware according to the directions on Confluence results in the following error

## The lines in question:

- They are all attempting to set a port to 1 or 0

- There are similar lines elsewhere in the file that do compile

```

-- 1000BASE-X core

U GigEthGtx7Core : entity work.GigEthGtx7Core

port map (

-- Clocks and Resets

gtrefclk bufg

=> sysClk125, -- Used as DRP clock in IP core

=> sysClk125. -- Used as CPLL clock reference

atrefclk

independent clock bufg => sysClk125, -- Used as stable clock reference

txoutclk

rxoutclk

=> open.

userclk

=> svsClk62.

userclk2

=> svsClk125.

=> sysClk62,

rxuserclk

=> sysClk62,

rxuserclk2

reset

=> coreRst,

=> coreRst,

pma reset

resetdone

=> open,

=> '1',

mmcm locked

mmcm reset

=> open,

cplllock

=> open,

-- PHY Interface

gmii txd

=> amiiTxd.

amii tx en

=> amiiTxEn,

qmii tx er

=> gmiiTxEr,

gmii rxd

=> gmiiRxd,

gmii rx dv

=> gmiiRxDv,

gmii rx er

=> amiiRxEr.

amii isolate

=> open,

-- MGT Ports

txp

=> gtTxP,

=> atTxN.

txn

rxp

=> atRxP.

=> atRxN.

-- Quad PLL Interface

gt0 gplloutclk in

-- OPLL not used

gt0 qplloutrefclk in

=> '0'.

-- OPLL not used

-- Configuration and Status

configuration vector

=> config.coreConfig.

status vector

=> status.coreStatus,

signal_detect

=> sigDet);

```

# Vivado project doesn't have the source linked to this component

- - > M PwrUpRst Inst: PwrUpRst(rtl) (PwrUpRst.vhd) (1)

- > @ U\_MMCM : ClockManager7(rtl) (ClockManager7.vhd)

- ✓ M GEN\_LANE[0].U\_GigEthGtx7: GigEthGtx7(mapping) (GigEthGtx7.vhd) (5)

- > M U AxiLiteAsync : AxiLiteAsync(STRUCTURE) (AxiLiteAsync.vhd)

- > M U\_SysRst : RstSync(rtl) (RstSync.vhd)

- > @ U\_MAC : EthMacTop(mapping) (EthMacTop.vhd)

- U\_GigEthGtx7Core : gigethgtx7core

- > 0 U\_GigEthReg : GigEthReg(rtl) (GigEthReg.vhd)

## Tried adding source manually in Vivado

#### Source:

/home/ibmayer/SLAC/atlas-chess2/firmware/submodules/surf/ethernet/GigEt hCore/gtx7/dcp/coregen/GigEthGtx7Core.xci

# Get a new error (appears related to the same core):

```

WARNING: [Vivado 12-4802] The synthesis checkpoint for IP '/home/ibmayer/SLAC/atlas-chess2/firmware/submodules/surf/ethernet/GigEthCore/gtx7/dcp/coregen/GigEthGtx7Core.xci' is not generated

and IP is locked. An out-of-context (OOC) run will be created and/or launched, but synthesis may not be able to complete or could result in incorrect behavior.

Please select 'Report IP Status' from the 'Tools/Report' menu or run Tcl command 'report_ip_status' for more information.

WARNING: [Project 1-576] IP '/home/ibmayer/SLAC/atlas-chess2/firmware/submodules/surf/ethernet/GigEthCore/gtx7/dcp/coregen/GigEthGtx7Core.xci' in run GigEthGtx7Core_synth_1 is locked, no out

-of-context (OOC) run will be launched. The run may not be able to complete.

Please select 'Report IP Status' from 'Tools/Report' or run the Tcl command 'report_ip_status' for more information.

CRITICAL WARNING: [IP Flow 19-4739] Writing uncustomized BOM file '/home/ibmayer/SLAC/atlas-chess2/firmware/submodules/surf/ethernet/GigEthCore/gtx7/dcp/coregen/GigEthGtx7Core.xml'

WARNING: [Project 1-576] IP '/home/ibmayer/SLAC/atlas-chess2/firmware/submodules/surf/ethernet/GigEthCore/qtx7/dcp/coregen/GigEthGtx7Core.xci' in run GigEthGtx7Core_synth_1 is locked, no out

of-context (OOC) run will be launched. The run may not be able to complete.

Please select 'Report IP Status' from 'Tools/Report' or run the Tcl command 'report ip status' for more information.

[Wed Jun 21 16:08:00 2017] Launched GigEthGtx7Core_synth_1...

Run output will be captured here: /home/ibmaver/SLAC/atlas-chess2/firmware/build/AtlasChess2FebEth/AtlasChess2FebEth project.runs/GigEthGtx7Core synth 1/runme.log

[Wed Jun 21 16:08:00 2017] Launched synth 1...

Run output will be captured here: /home/ibmayer/SLAC/atlas-chess2/firmware/build/AtlasChess2FebEth/AtlasChess2FebEth project.runs/synth 1/runme.log

launch runs: Time (s): cpu = 00:00:09; elapsed = 00:00:09. Memory (MB): peak = 1359.336; gain = 51.070; free physical = 1510; free virtual = 11346

[Wed Jun 21 16:08:00 2017] Waiting for synth_1 to finish...

[Wed Jun 21 16:08:18 2017] synth_1 finished

wait_on_run: Time (s): cpu = 00:00:17 ; elapsed = 00:00:18 . Memory (MB): peak = 1363.195 ; gain = 3.859 ; free physical = 1513 ; free virtual = 11350

```

- This says that "IP is locked"

- This seems to indicate that we do not have access to some Xilinx IP core (or perhaps a 3rd party IP core)

# The Makefile is creating a strange infinite-link directory loop

```

[ibmayer@ubc-itk-daq AtlasChess2FebEth] $ 1s -ld firmware/build/AtlasChess2FebEth/

drwxrwxr-x. 8 ibmayer ibmayer 4096 Jun 21 13:56 firmware/build/AtlasChess2FebEth/

[ibmayer@ubc-itk-daq AtlasChess2FebEth] $ 1s -ld firmware/build/AtlasChess2FebEth/firmware

lrwxrwxrwx. 1 ibmayer ibmayer 40 Jun 21 13:22 firmware/build/AtlasChess2FebEth/firmware -> /home/ibmayer/SLAC/atlas-chess2/firmware

[ibmayer@ubc-itk-daq AtlasChess2FebEth] $ pwd

/home/ibmayer/SLAC/atlas-chess2/firmware/build/AtlasChess2FebEth

[ibmayer@ubc-itk-daq AtlasChess2FebEth] $

```

- I create atlas-chess2/firmware/build/ (as per the Confluence instructions)

- The makefile creates (in the build/ dir):

AtlasChess2FebEth/firmware/build/AtlasChess2FebEth/firmware/

- The firmware/ in red is a link to the firmware/ in green

## Software Question from Robin

I've been looking through slack software/firmware package:

return((~value)&0x3F)

https://github.com/slaclab/atlas-chess2

The configure pixel payload is inverted:

Is this correct?

```

@staticmethod

def configPixel(enable, chargeInj, trimI):

# Default value: disable pixel, no charge injection, all trim bits disabled

value = 0x00

# Check if pixel is enabled

if enable:

value |= 0x20

# Check if enabling charge injection

if chargeInj:

value |= 0x01

# Set the trim current source

value |= ((trimI & 0xF) << 1)

# Return the inverted value</pre>

```