# A MTCA.4 Based System for the Control of Accelerator Magnets

#### **Petr Vetrov**

#### Thomas Delfs, Klaus Diekmann, Frantisek Krivan, Kay Rehlich, Ofir Shefer-Shalev, Manfred Zimmer

HELMHOLTZ

12/11/2017

FEA, Petr Vetrov

# **PROBLEM DOMAIN**

- The existing control system based on the SEDAC- it is fieldbus developed by DESY in 1976!

- SEDAC COPSC have many different types of controllers, which are not compatible each to other

- Old system can not be supported now and should be replaced to modern solution

- Boundary conditions: as cheap as possible, standard, high precision and versatile solution

- MTCA.4 as prototype was selected for new control system

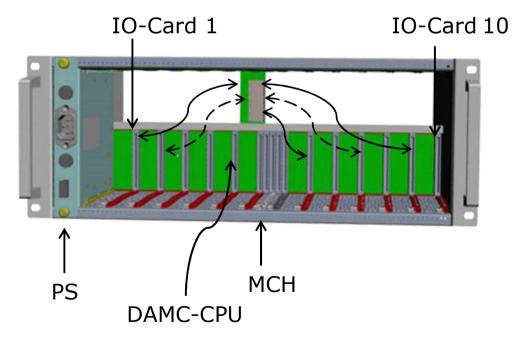

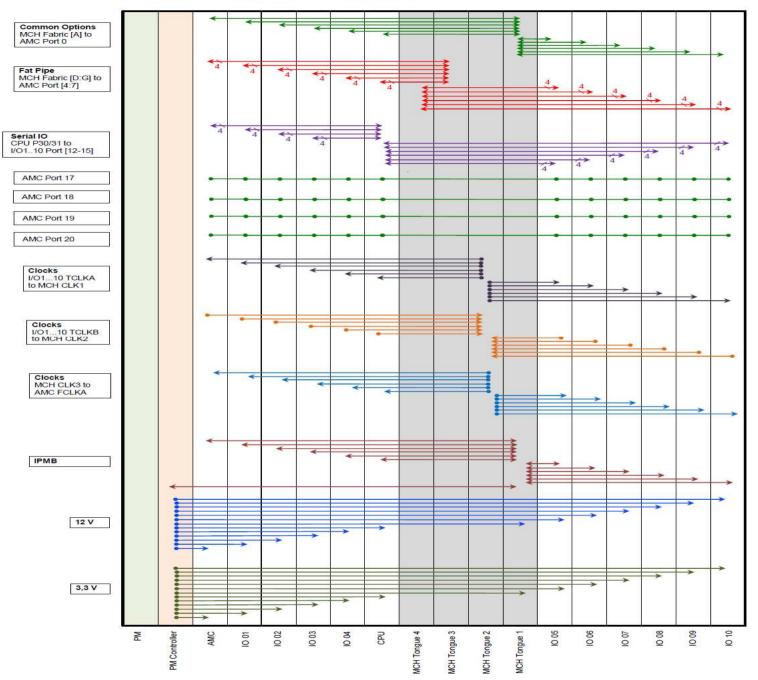

# **COPSC CRATE ARCHITECTURE**

- Concept MTCA.4 based crate was presented already at last year

- Standard set of MTCA.4 features are supported by Backplane: IPMI, PCIe, Ethernet, MLVDS bus, CLOCKs etc.

- DAMC-CPU Z3 connectors to port 12-14 of IO-Card Z1connector

- Other application can be implemented in this crate

- NO cooling unit

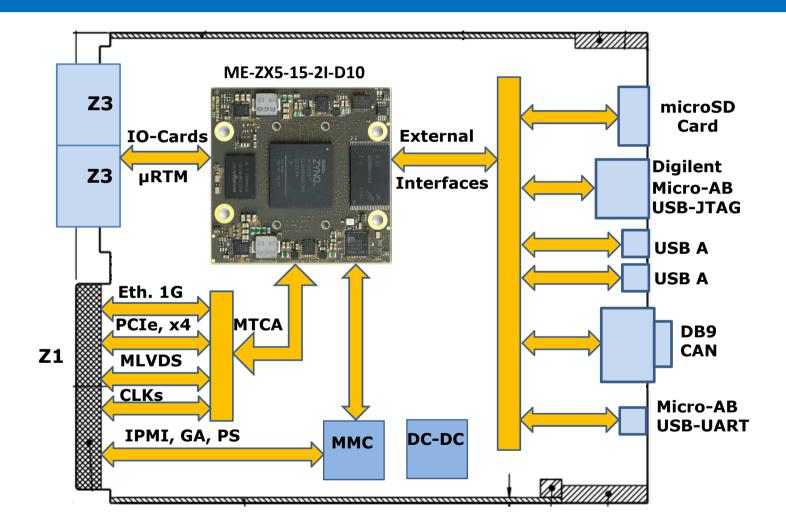

## **DAMC-CPU Card Features**

- The main part of DAMC-CPU board is Enclustra Mercury system-on-chip module ME-ZX5-15-2I-D10, which is based on the Zynq FPGA

- The DAMC-CPU board was designed by FEA and can be used as controller of IO-Cards, as simple MTCA.4 CPU or as AMC with µRTM interface

- The ZX5 boot options are defined by MMC

- The DAMC-CPU is Full Size, Double AMC

- Power consumption < 15 Watt

- Cost < 1000€

## **Block Diagram of DAMC-CPU**

12/11/2017

FEA, Petr Vetrov

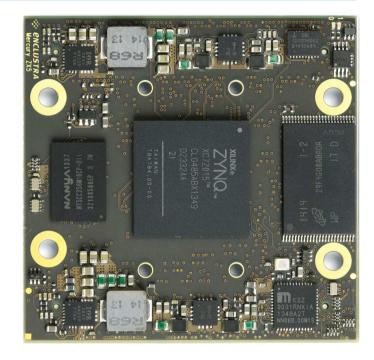

## **ZX5** Features

The Enclustra Mercury ME-ZX5-15-2I-D10 (ZX5) module includes:

- Xilinx Zynq®-7015 SoC, with:

- Dual ARM<sup>®</sup> Cortex<sup>™</sup>-A9 MPCore<sup>™</sup> based processing system (PS)

- Xilinx Artix-7 28 nm FPGA fabric based programmable logic (PL)

- PCIe Gen2 ×4, USB 2.0, Gigabit Ethernet PHY etc.

- 4 MGTs @ 6.25 Gbit/sec

- 1 GB DDR3L SDRAM, 512 MB NAND flash, 64 MB quad SPI flash

- 158 user I/Os:

- 12 ARM peripheral I/Os (SPI, SDIO, CAN, I2C, UART)

- 146 FPGA I/Os (single-ended, differential or analog)

- Small form factor (56 × 54 mm)

- 5 to 15 V supply voltage

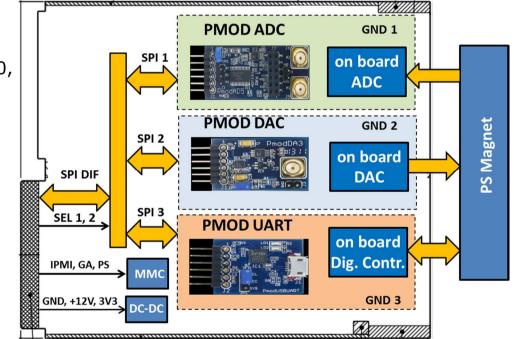

## **Features Prototype IO-Card**

- Prototype IO-Cards has two implementations of ADC and DAC and Digital controller for management of external PS:

- PMOD (Peripheral Module interface) devices

- ON board placing components

- Different types of Magnet PS can be controlled by one type of IO-Card

- Every PMOD slot has SPI interface

- The IO-Card is made on a multi-layer PCB – 14 Layers

- Power consumption of IO-Card smaller than 10 W

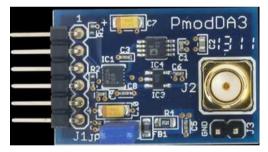

#### **Features PMOD**

- Pmod<sup>™</sup> devices are Digilent's line of small I/O interface boards

- The PMOD cards usage are very attractive, because it allows to install different ADC/DAC with different parameters and with the same interface, for example - SPI

- IT is way to extend the capabilities of programmable logic and embedded control boards.

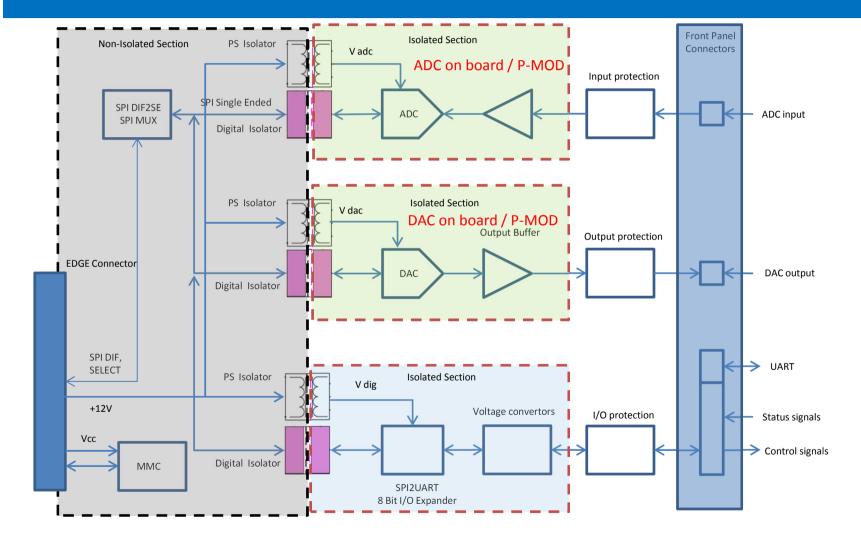

#### **Block Diagram Prototype IO-Card**

- 1. Backplane Z1 connector:

- 1. card power GND, 12V and 3,3V

- 2. SPI 4 diff signals and 2 single ended

- 3. MMC interface IPMI, GA[0:2], PS0, PS1, Enable

- 2. Power DC/DC convertors and isolation components

- 3. MMC micro controller, EPROM ID, temperature sensor

- 4. SPI interface control, isolation, splitting and multiplexing

- 5. ADC last version 24 bit ADC

- 6. DAC last version 16 bit DAC

- 7. Digital interface UART interface/ control and status signals

# Status&Conclusion

- The prototype of IO-Cards in production now

- A DAMC-CPU board will run in production at the end of 2017

- COPSC crate, Power SUPPLY, MCH will be delivered in beginning, 2018

- Using mezzanine boards for DAMC-CPU and for IO-Card greatly simplifies the design and allows you to modify the system parameters without modifying the basic boards

## Thank you for your attention!

# Addendum

#### **IO Card Block Diagram**

Draft Backplane-Topology Project I/O-Crate Variante 5 Rev. 1.5

12/1