### **FP7 - EuCARD** LLRF at FLASH

S.Simrock, M.Grecki for the LLRF team

WP 10 kick-off meeting

DESY, 24 March 2009

### Introduction

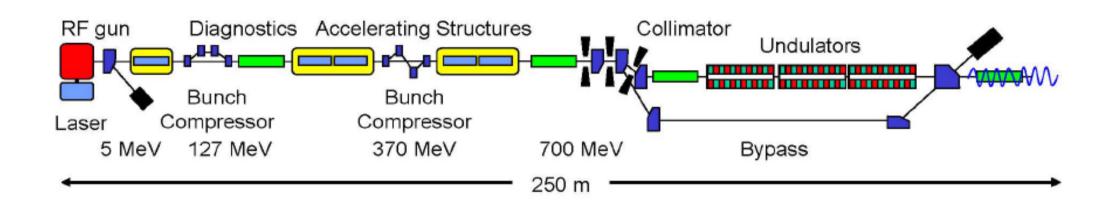

FLASH (Free-Electron LASer in Hamburg) is designed to produce SASE FEL radiation with a wavelength down to 6 nm with high brilliance

- 700MeV (12.5nm), after upgrade 1GeV (6nm)

- User experiments started in June 2005

- Test facility for technology development

#### **FLASH**

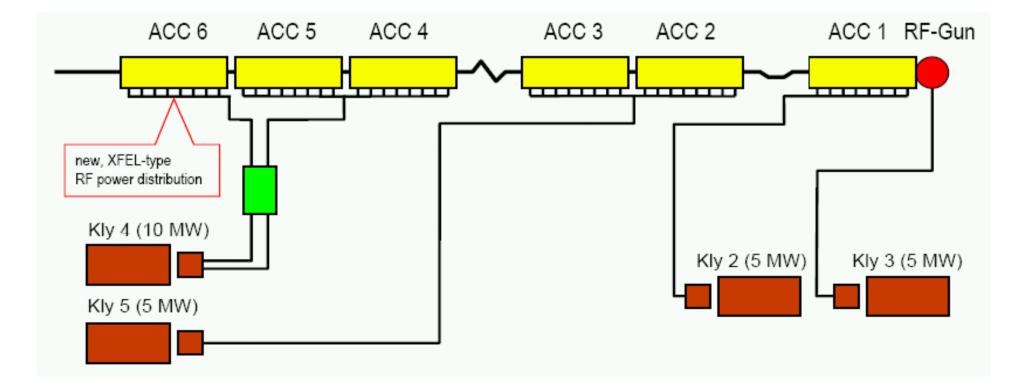

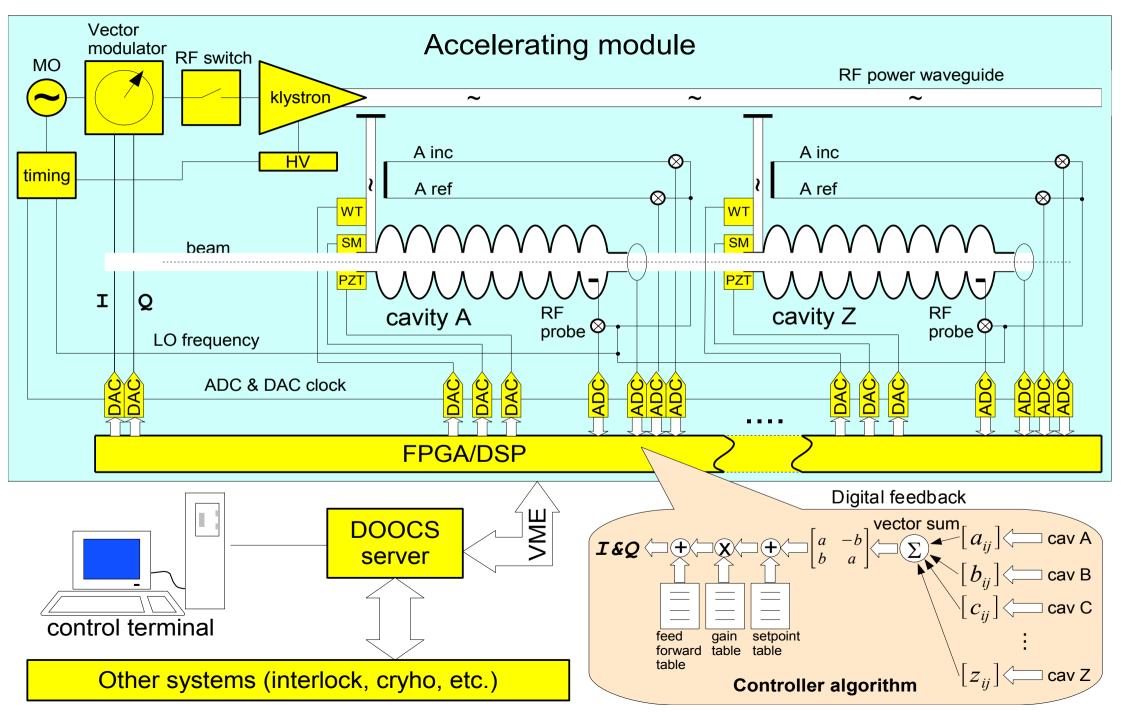

### LLRF system in FLASH

### **FLASH LLRF station**

- Several tens of analogue inputs 1.3 GHz, 0dBm

- Down-conversion required

- System latency < 1µs

- Synchronized with MO

- RF drive output

- Low latency communication to other modules (500 µs)

Piezo driver

— ...

— ...

- Communication to other systems

- Waveguide tuners

- System must be reliable, easy operable, robust...

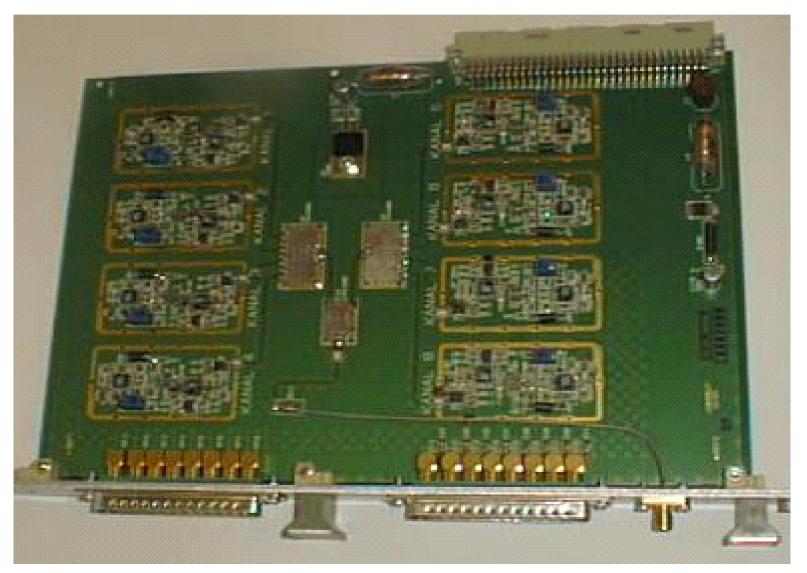

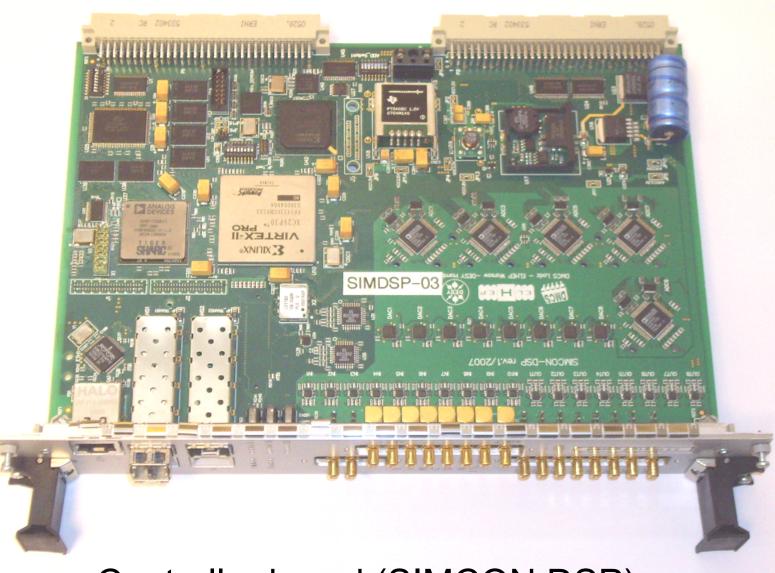

#### Downconverter board (IF=250kHz)

DSP C67 board

Controller board (SIMCON DSP)

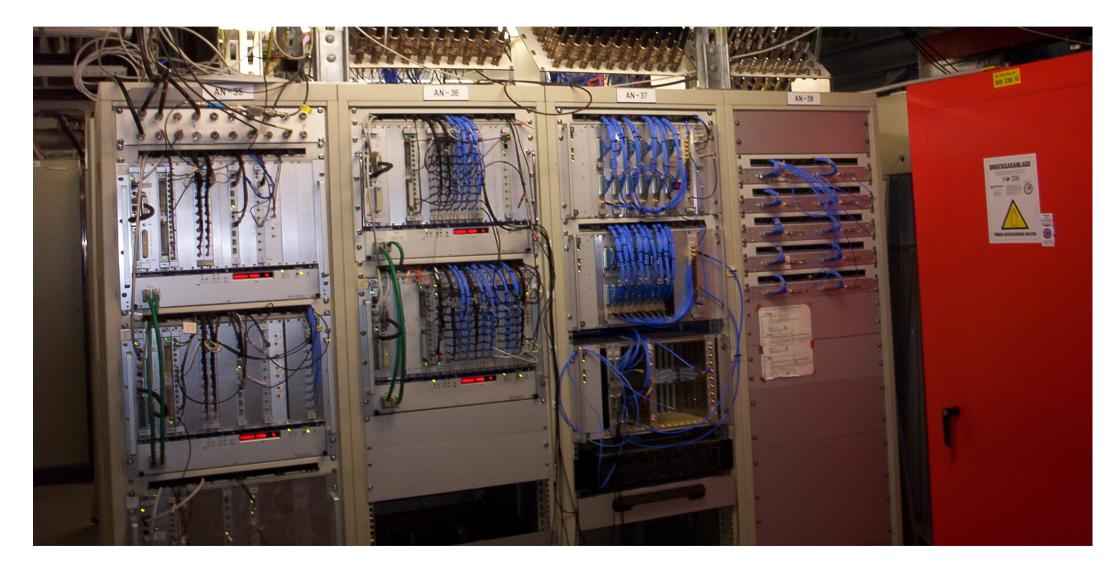

System racks (VME)

# Why we need LLRF upgrade at FLASH (1)

- The present LLRF control system at FLASH will satisfy user needs for the next 1-2 years but does not fulfill the long term (3-10 years) requirements in the following areas:

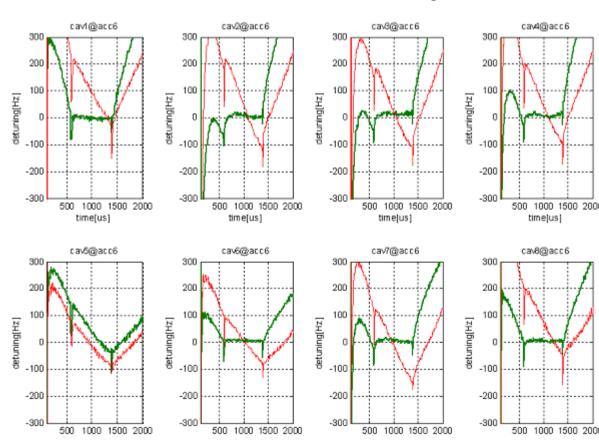

- 1. Field regulation

- The long term phase drifts especially in the injector section are to large (few ps/day). The proposed calibration scheme of the downconverters using the laser master oscillator will improve this stability by about one order of magnitude.

- The short term stability will also need some improvement (especially for the 3rd harmonics cavities) which can be achieved with a high IF/ clock scheme which is planned ot be implemented in the ATCA system. The present DSP systems clock rate is limited to 1 MHz.

- The vector sum calibration requires improvement which can be achieved with the combination of high IF/clock and power signal processing not available in the present DSP system.

# Why we need LLRF upgrade at FLASH (2)

- 2. Availability

- The ATCA concept is optimized for high availability.

- Significant diagnostics are required to support exception handling which will improve up-time. These algorithm cannot be implemented in the current DSP system

- Cables defects are one of the main problems. With the new ATCA concept with cabling from the rear side, a significant improvement is expected.

- 3. Maintenance

- The very limited resources require similar standards to be used for FLASH and XFEL. An ATCA based system will reduce resources required for maintenance.

- 4. Operability

- FLASH will require at higher degree of automation in the coming 2-3 years (~2010) to simplify changes in operating parameters (availability, performance, manpower) and guarantee high performance faster changing operational parameters. The ATCA based LLRF system can provide the necessary functionality which will be available at the XFEL after a few years of operation (~2015).

### **Project history (shortly)**

- Very ambitious first version, but...

- Budget reduction necessary

- Trials to cut down the required resources without significant scope reduction

- Limited scope of the project but not in scale with budget reduction

- wide usage of students work supervised by experts

### **Goal of FP7 LLRF for FLASH**

The goal of the project is to advance RF Control Technology in the areas of hardware and software and to test developed solutions in FLASH accelerator:

- develop LLRF implementation as HA ATCA System with required fast and ultra fast analogue and digital IO

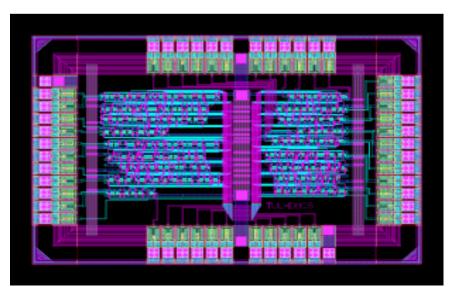

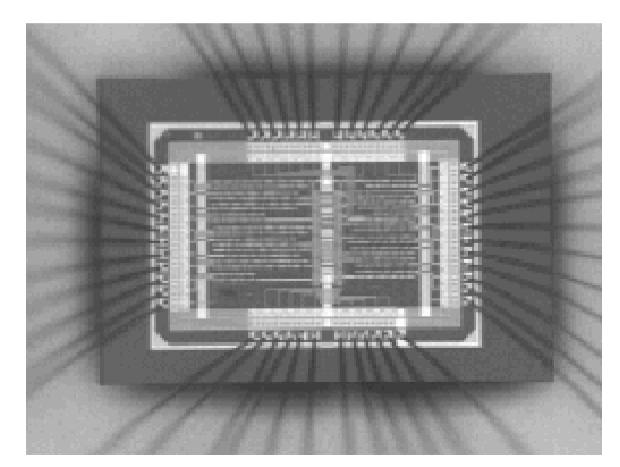

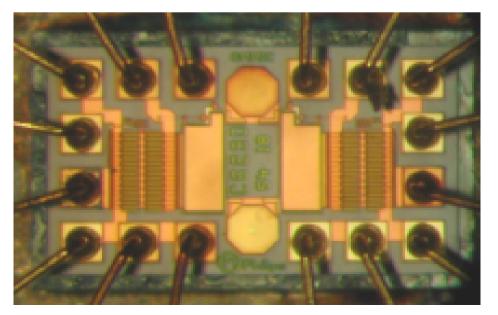

- develop new frequency conversion and multi-channel ASIC version of downconverter

- develop radiation monitoring (based on customized ASIC and standard components)

- develop other necessary control systems (piezo, waveguide) and integrate them with ATCA based LLRF system

- improve technical performance

- optimize reliability availability

- reduce cost

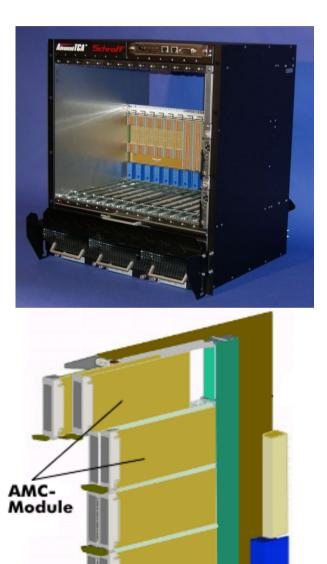

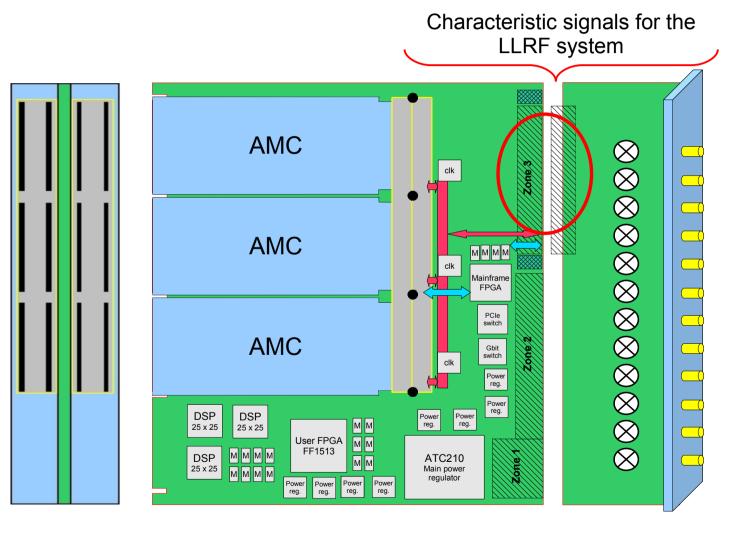

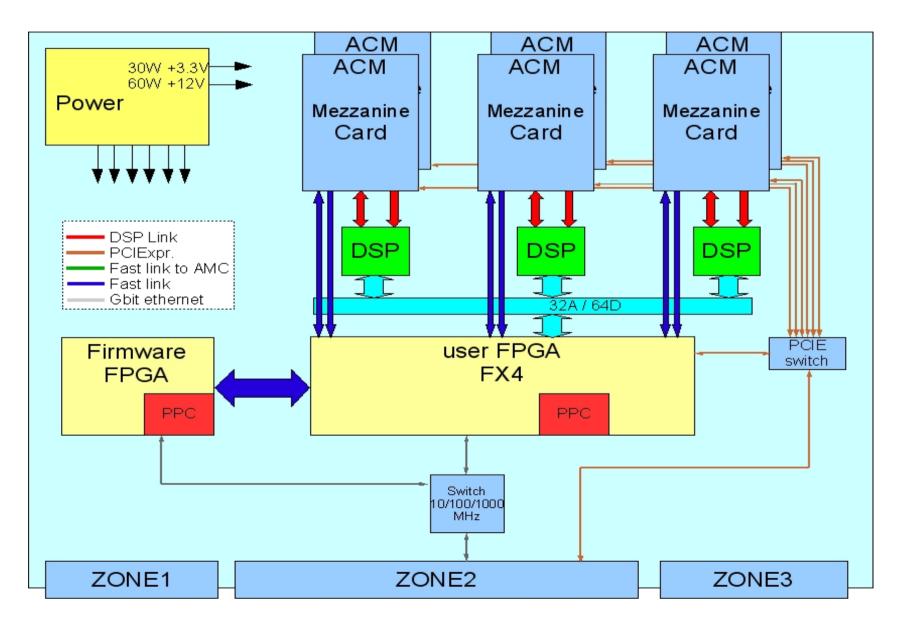

### Task 1 Development of ATCA carrier boards with FPGA, DSP

- Carries customized AMC modules

- Provides processing power and communication between system components

- Carries RF analogue signals

- Distributes timing and frequency reference signals

### Task 1 Development of ATCA carrier boards with FPGA, DSP

### Task 1 Development of ATCA carrier boards with FPGA, DSP

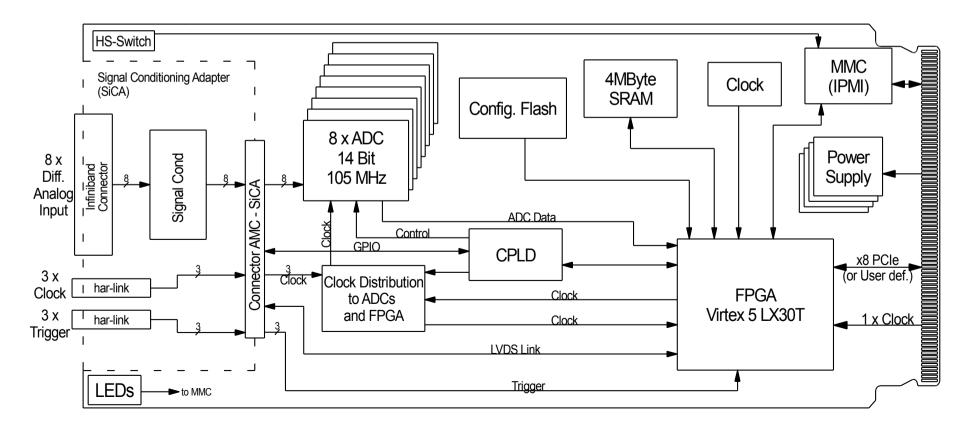

### Task 2 Development of AMC modules with fast analog and digital IO

Provides the basic input/output functionality for field regulation (at least 14b, 100MHz)

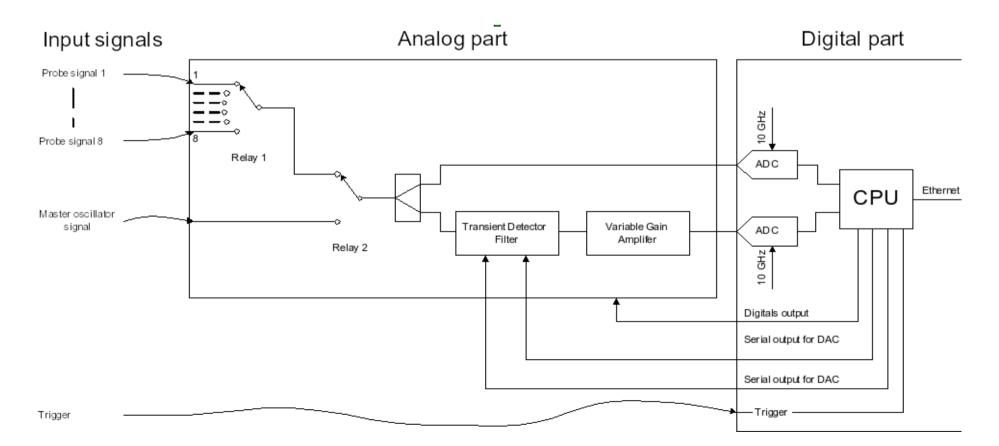

### Task 3 Development of AMC modules with ultra fast analog IO

Provides the very fast analogue input (at least 2GHz, 10b) for special purposes (direct sampling, transient detection, HOM measurements, etc.)

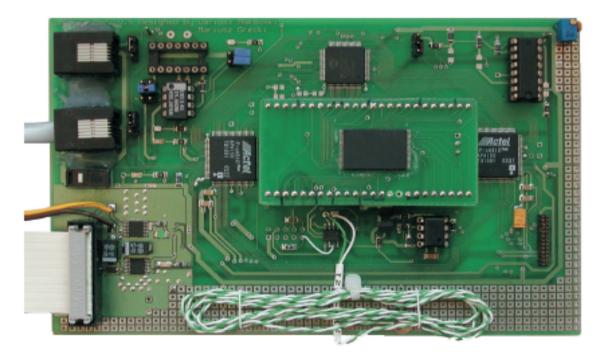

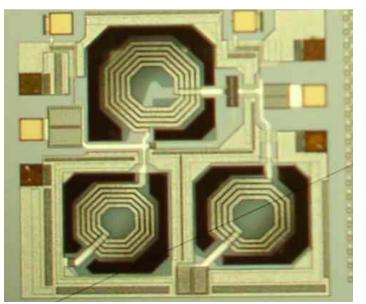

Task 4 Development of AMC module with radiation sensors (gamma and neutron detector with customized ASICs)

Provides real time radiation monitoring for diagnostics and momentum management

Task 4 Development of AMC module with radiation sensors (gamma and neutron detector with customized ASICs)

Development of specialized SRAM based neutron detector is needed

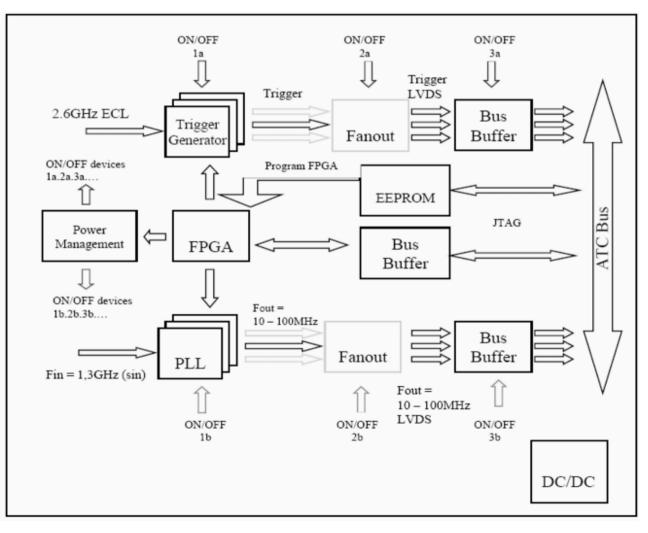

### Task 5 Development of reference, clock and timing distribution for ATCA based LLRF

- One of the problem in FLASH is a long term phase drifts, especially in the injector section

- Reference signals for downconverters are needed to reduce drifts. They must be distributed over the LLRF system.

- Also timing signals (clocks and event triggers) must be generated from reference

### Task 6 Development of AMC/RTM module for downconverters and upconverters

The main goal of this task is to test various solutions of down- and upconversion (including building specialized ASICs) to and to develop RTM (or AMC) modules with down- and upconverters.

It is expected that higher IF than it is used nowadays will improve stability and signal/noise ratio.

### Task 7 ATCA based implementation of cavity tuners & waveguide control

Other control system also have to be integrated with ATCA based LLRF system

### Task 8 Development of beam based longitudinal feedbacks for the ATCA based LLRF system

The goal of this task is to explore the possibility to build up beam based feedbacks and test a prototype at FLASH. The diagnostic devices (measuring longitudinal beam parameters like beam energy, bunch arrival etc.) will be connected by developed interfaces to ATCA based LLRF system and fast low level algorithms to extract relevant correction parameters will be implemented. The corrections will be then fed back to the LLRF system within a bunch train.

### Institutions

Coordination: S.Simrock, DESY

ISE

INP

INP

DESY Deutsches Elektronen-Synchrotron, Hamburg, Germany

**DMCS** Department of Microelectronics and Computer Science, Technical University of Lodz, Poland

Institute of Electronic Systems, Warsaw University of Technology, Poland

Niewodniczanski Institute of Nuclear Physics, Krakow, Poland

Institute for Nuclear Studies, Swierk, Poland

### **Project budget (1)**

|   |                                                                                                           | person-<br>months | hardware<br>[kE] | travel<br>[kE] |

|---|-----------------------------------------------------------------------------------------------------------|-------------------|------------------|----------------|

| 1 | Development of ATCA carrier boards with FPGA, DSP                                                         | 16                | 44               | 11             |

| 2 | Development of AMC modules with fast analog IO and digital IO                                             | 9                 | 35               | 8              |

| 3 | Development of ultra fast analog IO (2 Gs, 10 bit)                                                        | 10                | 20               | 5              |

| 4 | Development of AMC module with radiation<br>sensors (gamma and neutron detector with<br>customized ASICs) | 13                | 78.5             | 5              |

| 5 | Development of reference, clock and timing distribution for ATCA                                          | 20                | 80               | 8              |

| 6 | Development of AMC/RTM module for<br>downconverters and upconverters                                      | 17                | 50               | 8              |

| 7 | ATCA implementation of piezo & waveguide                                                                  | 13                | 40               | 11             |

| 8 | Development of beam based longitudinal feedbacks for the ATCA based LLRF system.                          | 22                | 40               | 10             |

|   | Total                                                                                                     | 120               | 387.5            | 66             |

### **Project budget (2)**

|   |                                                                                                           | DESY        | DMCS        | ISE         | INP     | INP PAN          |

|---|-----------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|---------|------------------|

| 1 | Development of ATCA carrier boards with FPGA,                                                             | 82.6        | 45          | 0           | 0       | 0                |

| 2 | Development of AMC modules with fast analog IO and digital IO                                             | 34.4        | 33.125      | 8           | 0       | 0                |

| 3 | Development of ultra fast analog IO (2 Gs, 10 bit)                                                        | 24.4        | 36          | 0           | 0       | 0                |

| 4 | Development of AMC module with radiation<br>sensors (gamma and neutron detector with<br>customized ASICs) | 39.1        | 91.75       | 0           | 0       | 0                |

| 5 | Development of reference, clock and timing distribution for ATCA                                          | 82.6        | 0           | 89.5        | 0       | 0                |

| 6 | Development of AMC/RTM module for<br>downconverters and upconverters                                      | 66.4        | 0           | 63.75       | 0       | 0                |

| 7 | ATCA implementation of piezo & waveguide<br>control                                                       | 22          | 28.375      | 0           | 38      | 0                |

| 8 | Development of beam based longitudinal feedbacks for the ATCA based LLRF system. Total                    | 43<br>394.5 | 0<br>234.25 | 0<br>161.25 | 0<br>38 | 86.875<br>86.875 |

### **Project budget (3)**

| 1st year personel<br>DESY | DMCS | ISE | INP (kra | ikow INP PAN( |       | hardware<br>DESY | DMCS | ISE | INP | INP PAN |   |     | travel<br>DESY | DMCS | ISE | INP |   | 0 total |   |

|---------------------------|------|-----|----------|---------------|-------|------------------|------|-----|-----|---------|---|-----|----------------|------|-----|-----|---|---------|---|

| 1                         | 4    | 6   |          |               | 10    | 1                | 8    | 10  |     |         |   | 28  |                | 2    | 5   |     |   |         | 7 |

| 2                         | 2    | 5   |          |               | 7     | 1                | 10   | 6   | 3   |         |   | 19  |                | 1    | 2   | 2   |   |         | 5 |

| 3                         | 2    | 4   |          |               | 6     |                  | 7    | 6   |     |         |   | 13  |                | 1    | 2   |     |   |         | 3 |

| 4                         | 3    | 7   |          |               | 10    |                  |      | 25  |     |         |   | 0,5 |                | 1    | 2   |     |   |         | 3 |

| 5                         | 5    |     | 6        |               | 11    | 1                | 15   |     | 40  |         |   | 55  |                | 2    |     | 3   |   |         | 5 |

| 6                         | 3    |     | 6        |               | 9     | 1                | 10   |     | 20  |         |   | 30  |                | 2    |     | 3   |   |         | 5 |

| 7                         |      | 3   |          | 5             | 8     | 1                | 10   | 6   |     | 6       |   | 22  |                | 1    | 2   |     | 3 |         | 6 |

| 8                         | 3    |     |          |               | 10 13 |                  |      |     |     | 2       | 0 | 20  |                | 1    |     |     |   | 5       | 6 |

|                           | 22   | 25  | 12       | 5             | 10    | 75               | ,5   | 53  | 63  | 6 2     | 0 |     | 1              | 1    | 13  | 8   | 3 | 5       |   |

| 2nd year personel<br>DESY<br>1<br>2 | DMCS<br>4 | ISE<br>2<br>2 | INP (kral | kow INP PAN(S | wi⊧total<br>6<br>2 |   | DMCS<br>12<br>10 | ISE<br>4<br>4 | INP<br>2 | inp pan | total | 16<br>16 | travel<br>DESY | DMCS<br>1<br>1 | ISE<br>3<br>1 | INP<br>1 | INP PAN | l total | 4<br>3 |

|-------------------------------------|-----------|---------------|-----------|---------------|--------------------|---|------------------|---------------|----------|---------|-------|----------|----------------|----------------|---------------|----------|---------|---------|--------|

| 3                                   |           | 4             |           |               | 4                  |   | 3                | 4             |          |         |       | 7        |                | 1              | 1             |          |         |         | 2      |

| 4<br>5                              | 3         | 3             | 6         |               | 3<br>9             | 1 | 13<br>5          | 35            | 20       |         |       | 48<br>25 |                | 1<br>1         | 1             | 2        |         |         | 2<br>3 |

| 6<br>7                              | 4         | 2             | 4         | 3             | 8<br>5             | 1 | 10<br>10         | 4             | 10       | 4       |       | 20<br>18 |                | 1<br>1         | 2             | 2        | 2       |         | 3<br>5 |

| 8                                   | 2<br>13   | 13            | 10        | 3             | 7 9<br>0           |   | 10<br>73         | 51            | 32       | 1       | 0     | 20       |                | 1<br>8         | 8             | 5        | 2       | 3<br>0  | 4      |

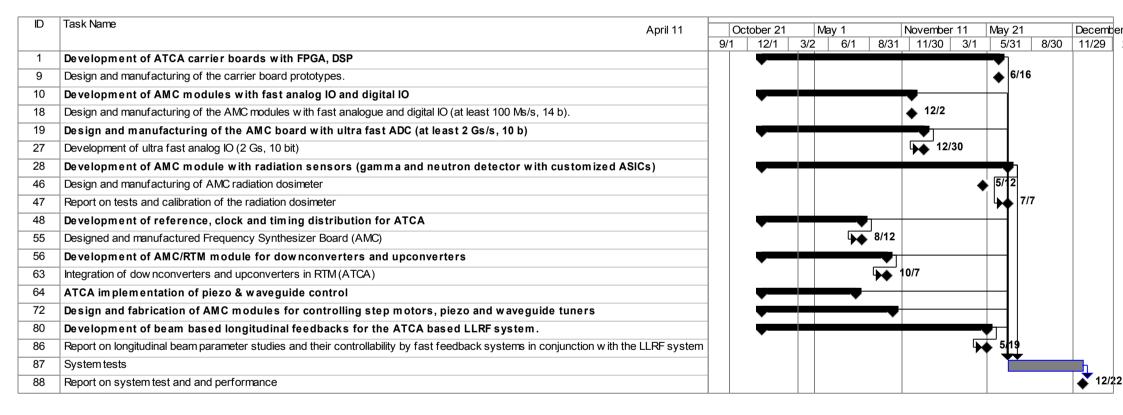

### Gantt chart of the project (1)

### Gantt chart of the project (2)

| ID | Task Name                                                 | October 21 |     | May 1 |      | November 11 | May 21 |      | Decem | nber 1 |

|----|-----------------------------------------------------------|------------|-----|-------|------|-------------|--------|------|-------|--------|

|    |                                                           | 12/1       | 3/2 | 6/1   | 8/31 | 11/30 3/1   | 5/31   | 8/30 | 11/29 | 2/2    |

| 1  | Development of ATCA carrier boards with FPGA, DSP         |            |     |       |      | · ·         |        |      |       | 1      |

| 2  | Requirements analysis and capture                         |            | h   |       |      |             |        |      |       |        |

| 3  | Schematic desig                                           |            |     |       |      |             |        |      |       |        |

| 4  | PCB design                                                |            |     |       |      |             |        |      |       |        |

| 5  | Prototype fabrication                                     |            |     |       | Ì    |             |        |      |       |        |

| 6  | Debugging                                                 |            |     |       |      | h           |        |      |       |        |

| 7  | Schematic and PCB modifications                           |            |     |       |      | <b>T</b> h  |        |      |       |        |

| 8  | Fabrication of final boards                               |            |     |       |      |             |        |      |       |        |

| 9  | Design and manufacturing of the carrier board prototypes. |            |     |       |      |             | 6/10   | 6    |       |        |

| ID | Task Name Od                                                                                             | ber 21 |     | May 1 |     | N  | Novembe | r 11 | May 21 |      | Decem | ber 1 |

|----|----------------------------------------------------------------------------------------------------------|--------|-----|-------|-----|----|---------|------|--------|------|-------|-------|

|    |                                                                                                          | 12/1   | 3/2 | 6/1   | 8/3 | 31 | 11/30   | 3/1  | 5/31   | 8/30 | 11/29 | 2/2   |

| 10 | Development of AMC modules with fast analog IO and digital IO                                            |        |     |       |     |    | •       |      |        |      |       |       |

| 11 | Requirements analysis and capture                                                                        |        |     |       |     |    |         |      |        |      |       |       |

| 12 | Schematic desig                                                                                          | - Ěh   |     |       |     |    |         |      |        |      |       |       |

| 13 | PCB design                                                                                               | Ľ      |     | h     |     |    |         |      |        |      |       |       |

| 14 | Prototype fabrication                                                                                    |        |     | Ľ.    |     |    |         |      |        |      |       |       |

| 15 | Debugging                                                                                                |        |     | Ľ     | h   |    |         |      |        |      |       |       |

| 16 | Schematic and PCB modifications                                                                          |        |     |       |     | ı  |         |      |        |      |       |       |

| 17 | Fabrication of final boards                                                                              |        |     |       | Ì   |    | h       |      |        |      |       |       |

| 18 | Design and manufacturing of the AMC modules with fast analogue and digital IO (at least 100 Ms/s, 14 b). |        |     |       |     | •  | 12/2    |      |        |      |       |       |

| ID | Task Name                                                                             | Oct | ober 21 |     | Ma | ay 1 |     | Nov | ember | 11  | May 21 |      | Decem | nber 1 |

|----|---------------------------------------------------------------------------------------|-----|---------|-----|----|------|-----|-----|-------|-----|--------|------|-------|--------|

|    |                                                                                       |     | 12/1    | 3/  | 2  | 6/1  | 8/3 | 1 1 | 1/30  | 3/1 | 5/31   | 8/30 | 11/29 | 2/2    |

| 19 | Design and manufacturing of the AMC board with ultra fast ADC (at least 2 Gs/s, 10 b) |     |         |     |    |      |     |     | ካ     |     |        |      |       |        |

| 20 | Requirements capture                                                                  |     |         | Ь   |    |      |     |     |       |     |        |      |       |        |

| 21 | Schematic desig                                                                       |     |         | Ľh. |    |      |     |     |       |     |        |      |       |        |

| 22 | PCB design                                                                            |     | 1       | Ľ   |    | h    |     |     |       |     |        |      |       |        |

| 23 | Prototype fabrication                                                                 |     |         |     |    |      | h   |     |       |     |        |      |       |        |

| 24 | Debugging                                                                             |     |         |     |    |      | Ľ   |     |       |     |        |      |       |        |

| 25 | Schematic and PCB modifications                                                       |     | 1       |     |    |      | ľ   |     |       |     |        |      |       |        |

| 26 | Fabrication of final boards                                                           |     |         |     |    |      |     |     |       |     |        |      |       |        |

| 27 | Development of ultra fast analog IO (2 Gs, 10 bit)                                    |     |         |     |    |      |     | ₩   | 12/3  | 0   |        |      |       |        |

### Gantt chart of the project (3)

| ID | Task Name                                                                                           | Oct | ober 21 |     | May 1 |          | Nove | nber 11 | May 21 |      | Decemt | ber 1 |

|----|-----------------------------------------------------------------------------------------------------|-----|---------|-----|-------|----------|------|---------|--------|------|--------|-------|

|    |                                                                                                     |     | 12/1    | 3/2 | 6/    | 1 8/3    |      |         |        | 8/30 | 11/29  |       |

| 28 | Development of AMC module with radiation sensors (gamma and neutron detector with customized ASICs) |     | -       |     |       |          |      |         |        |      |        | 1     |

| 29 | Gam m a detector board                                                                              |     |         |     |       |          |      |         |        |      |        |       |

| 30 | Study and comparison of available gamma dosimeters                                                  |     |         |     |       |          |      |         |        |      |        |       |

| 31 | Design and fabrication of prototype board for initial tests of dosimeters                           |     |         |     | h     |          |      |         |        |      |        |       |

| 32 | Radiation sensitivity tests of selected gamma dosimeters                                            |     |         |     |       | L        |      |         |        |      |        |       |

| 33 | Design of detector board                                                                            |     |         |     |       | h        | _    |         |        |      |        |       |

| 34 | Fabrication of detector board                                                                       |     |         |     |       | Ì        |      |         | 1      |      |        |       |

| 35 | Tests and calibration of gamma dosimeter                                                            |     |         |     |       |          |      |         |        |      |        |       |

| 36 | Neutron detector board                                                                              |     |         |     |       |          |      |         |        |      |        |       |

| 37 | Study, comparison and simulation of various radiation sensitive SRAM cells                          |     |         |     |       |          |      |         |        |      |        |       |

| 38 | Selection of optimum radiation-sensitive cells for the neutron dosimeter array                      |     |         | h   |       |          |      |         |        |      |        |       |

| 39 | Design of a test integrated circuit ASIC 1                                                          |     |         |     |       |          |      |         |        |      |        |       |

| 40 | Design and fabrication of a prototype board for initial tests of dosimeters                         |     |         |     |       |          |      |         |        |      |        |       |

| 41 | Fabrication of the test integrated circuit ASIC 1 in the silicon foundry                            |     |         |     |       | <b>—</b> | L.   |         |        |      |        |       |

| 42 | Tests in the radiation environment and selection of final cells and the detector structure          |     |         |     |       |          | Ľ.   |         |        |      |        |       |

| 43 | Design of the final integrated circuit ASIC 2 of the neutron fluence dosimeter                      |     |         |     |       |          |      | h       |        |      |        |       |

| 44 | Fabrication of the final integrated circuit ASIC 2 in silicon foundry                               |     |         |     |       |          |      |         |        |      |        |       |

| 45 | Tests and calibration of the neutron dosimeter                                                      |     |         |     |       |          |      | _       | Ľ –    |      |        |       |

| 46 | Design and manufacturing of AMC radiation dosimeter                                                 |     |         |     |       |          |      |         | 5/12   |      |        |       |

| 47 | Report on tests and calibration of the radiation dosimeter                                          |     |         |     |       |          |      |         | 4 ◆ 7  | /7   |        |       |

| ID | Task Name                                                                  | Oc | tober 21 |     | May 1       |    |      | Novemb | er 11 | May 21 |      | Decem | ber 1 |

|----|----------------------------------------------------------------------------|----|----------|-----|-------------|----|------|--------|-------|--------|------|-------|-------|

|    |                                                                            |    | 12/1     | 3/2 | 2 6         | /1 | 8/31 | 11/30  | 3/1   | 5/31   | 8/30 | 11/29 | 2/28  |

| 48 | Development of reference, clock and timing distribution for ATCA           |    |          |     |             | -  | ו    |        |       |        |      |       | 7     |

| 49 | Integration MLO, MO, Timing                                                |    |          | L   |             |    | -    |        |       |        |      |       |       |

| 50 | Integration pulsed optical with RF                                         |    |          |     |             |    |      |        |       |        |      |       |       |

| 51 | Precision temperature stabilization of the reference frequency coax cables |    |          |     |             |    |      |        |       |        |      |       |       |

| 52 | Calibration Reference and LO to dow nconverters                            |    |          |     |             |    |      |        |       |        |      |       |       |

| 53 | Clock synthesizer for LLRF ADCs                                            |    |          |     | <u>ال</u> د |    |      |        |       |        |      |       |       |

| 54 | Integration with ultrastable timing and clock                              |    | 1        |     |             |    |      |        |       |        |      |       |       |

| 55 | Designed and manufactured Frequency Synthesizer Board (AMC)                |    | 1        |     |             | ♦  | 8/12 |        |       |        |      |       |       |

### Gantt chart of the project (4)

| ID | Task Name                                                         | Oc | tober 21 |     | May | 1   |      | Novemb | er 11 | May 21 |      | Decem | ber 1 |

|----|-------------------------------------------------------------------|----|----------|-----|-----|-----|------|--------|-------|--------|------|-------|-------|

|    |                                                                   |    | 12/1     | 3/2 |     | 6/1 | 8/31 | 11/30  | 3/1   | 5/31   | 8/30 | 11/29 | 2/2   |

| 56 | Development of AMC/RTM module for downconverters and upconverters |    |          |     |     |     |      |        |       |        |      |       | 1     |

| 57 | Prototype design                                                  |    |          |     |     |     |      |        |       |        |      |       |       |

| 58 | Fabrication of prototype                                          |    | 1 🎽      | h   |     |     |      |        |       |        |      |       |       |

| 59 | Tests and debugging                                               |    | 1        |     | h   |     |      |        |       |        |      |       |       |

| 60 | Design modification                                               |    | 1        |     |     | L   |      |        |       |        |      |       |       |

| 61 | Production                                                        |    | 1        |     |     | i b | L    |        |       |        |      |       |       |

| 62 | Tests of final design                                             |    | 1        |     |     |     |      |        |       |        |      |       |       |

| 63 | Integration of dow nconverters and upconverters in RTM (ATCA)     |    | _        |     |     |     | •••  | 10/7   |       |        |      |       |       |

| ID | Task Name                                        | Oc | tober 21 | 1   | May 1 |      | Novembe | er 11 | May 21 |      | Decem | iber 1 |

|----|--------------------------------------------------|----|----------|-----|-------|------|---------|-------|--------|------|-------|--------|

|    |                                                  |    | 12/1     | 3/2 | 6/1   | 8/31 | 11/30   | 3/1   | 5/31   | 8/30 | 11/29 | 2/28   |

| 64 | ATCA implementation of piezo & waveguide control |    |          |     |       | l i  |         |       |        |      |       |        |

| 65 | Requirements analysis and capture                |    |          |     |       |      |         |       |        |      |       |        |

| 66 | Schematic desig                                  |    | ] 🏼 🛍    |     |       |      |         |       |        |      |       |        |

| 67 | PCB design                                       |    |          |     |       |      |         |       |        |      |       |        |

| 68 | Prototype fabrication                            |    |          |     | L I   |      |         |       |        |      |       |        |

| 69 | Debugging                                        |    |          |     | Ľ.    |      |         |       |        |      |       |        |

| 70 | Schematic and PCB modifications                  |    | 1        |     | Ĺ     |      |         |       |        |      |       |        |

| 71 | Fabrication of final boards                      |    |          |     |       |      |         |       |        |      |       |        |

| ID | Task Name                                                                                     | Oc | tober 2 | 1  | May | 1   |      | Novembe | r 11 | May 21 |      | Decem | ber 1 |

|----|-----------------------------------------------------------------------------------------------|----|---------|----|-----|-----|------|---------|------|--------|------|-------|-------|

|    |                                                                                               |    | 12/1    | 3/ | 2   | 6/1 | 8/31 | 11/30   | 3/1  | 5/31   | 8/30 | 11/29 | 2/28  |

| 72 | Design and fabrication of AMC modules for controlling step motors, piezo and waveguide tuners |    |         |    |     |     |      |         |      |        |      |       | ]     |

| 73 | Requirements analysis and capture                                                             |    |         | h  |     |     |      |         |      |        |      |       |       |

| 74 | Schematic desig                                                                               |    |         | Ľ. | F.  |     |      |         |      |        |      |       |       |

| 75 | PCB design                                                                                    |    |         |    | ľ.  |     |      |         |      |        |      |       |       |

| 76 | Prototype fabrication                                                                         |    |         |    |     | h   |      |         |      |        |      |       |       |

| 77 | Debugging                                                                                     |    |         |    |     | Ľ.  |      |         |      |        |      |       |       |

| 78 | Schematic and PCB modifications                                                               |    | 1       |    |     | Ĭ   | 1    |         |      |        |      |       |       |

| 79 | Fabrication of final boards                                                                   |    | 1       |    |     | i   |      |         |      |        |      |       |       |

### Gantt chart of the project (5)

| D  | Task Name Oc                                                                                                                         | cic | ober 21 | 1   | √lay 1 |     | Nov      | embei | r 11 | May 21     |      | Decemb      | er 1 |

|----|--------------------------------------------------------------------------------------------------------------------------------------|-----|---------|-----|--------|-----|----------|-------|------|------------|------|-------------|------|

|    |                                                                                                                                      |     | 12/1    | 3/2 | 6/1    | 8/3 | 1 1      | 1/30  | 3/1  | 5/31       | 8/30 | 11/29       | 2/28 |

| 80 | Development of beam based longitudinal feedbacks for the ATCA based LLRF system.                                                     |     |         |     |        |     |          |       |      | <b>•</b> n |      |             |      |

| 81 | Requirements analysis and capture                                                                                                    |     |         | Ъl  |        |     |          |       |      |            |      |             |      |

| 82 | Design of required interfaces to LLRF controller                                                                                     |     |         |     | h      |     |          |       |      |            |      |             |      |

| 83 | Software development                                                                                                                 |     |         |     |        |     | <u>h</u> |       |      |            |      |             |      |

| 84 | Installation and debugging                                                                                                           |     |         |     |        |     |          |       | ı l  |            |      |             |      |

| 85 | Performance tests                                                                                                                    |     |         |     |        |     |          | Ì     |      |            |      |             |      |

| 86 | Report on longitudinal beam parameter studies and their controllability by fast feedback systems in conjunction with the LLRF system | ٦   |         |     |        |     |          |       |      | ♦ 5/19     |      |             |      |

| 87 | System tests                                                                                                                         |     |         |     |        |     |          |       |      |            |      |             |      |

| 88 | Report on system test and and performance                                                                                            |     |         |     |        |     |          |       |      |            |      | <b>12/2</b> | 22   |