### **BELLE II PXD WORKSHOP**

### **PXD9 PROBE CARD MASS TESTING**

L. ANDRICEK+, M. BORONAT\*, J. FUSTER\*, P. GOMIS\*,

M. HENSEL+, D. KLOSE+, C. KOFFMANE+, C. MARIÑAS°, M. VOS\*

\* IFIC (UNIVERSITAT DE VALÈNCIA/CSIC)

+ HLL (MPG MÜNCHEN)

° UNIVERSITÄT BONN

#### CONTENTS

#### 1. Motivation

- 2. Probe card: design and features

- **3.** Setup at HLL

- 4. Testing protocol

- 5. Output of the tests

- 6. Results

- 7. Overview

- 8. Lessons learned

- 9. Summary

- DEPFET modules fully assembled are attached to a kapton cable.

- Pre-testing of the modules before the attachment avoids having to remove the kapton in the case that the module doesn't behave as expected, simplifying the rework procedure.

- A needle card is required for this purpose.

### **PROBE CARD: FEATURES**

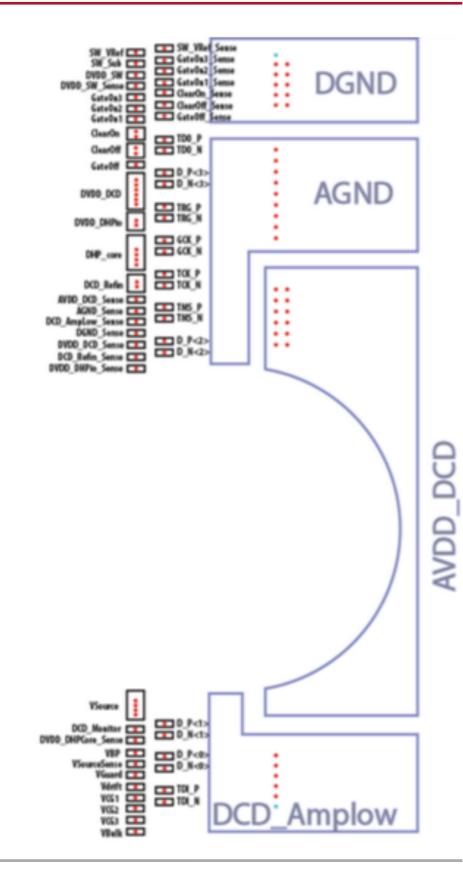

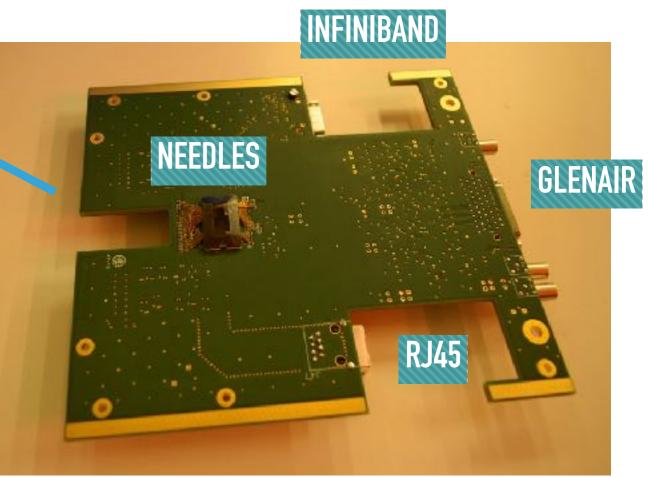

- The probe card directly interfaces the PXD9 modules to:

- RJ45 cable for the slow control signals.

- Glenair cable for power delivery.

- Infiniband cable for HSL data transmission.

- In ideal contact, the module can be fully operated (at the lowest frequency and half rate) through the probe card.

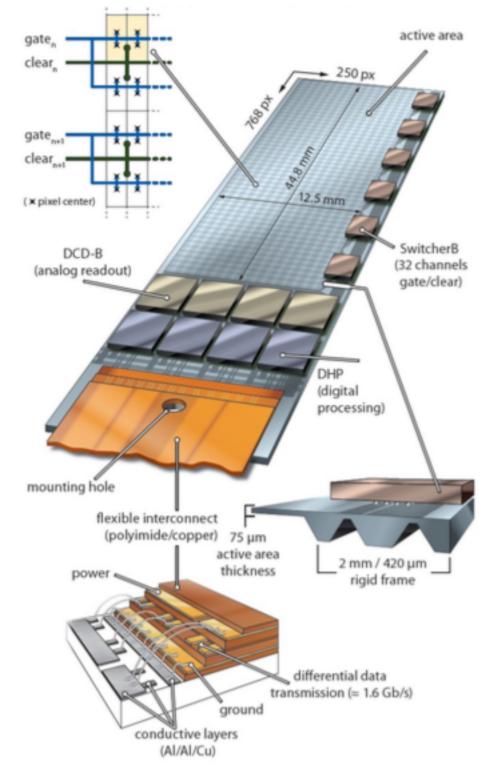

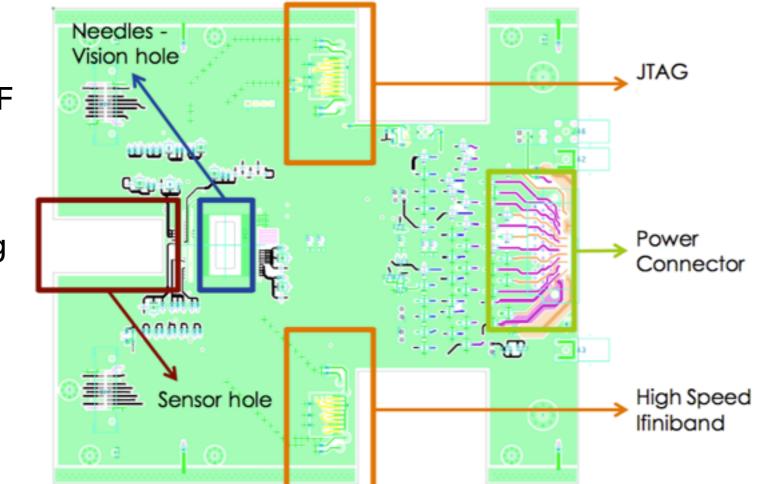

### PROBE CARD: DESIGN

- 2 different probe card designs for the 2 different layouts of PXD9: design A for IF/OB and B for IB/OF

- Pad distribution for PXD9:

- 59 small aluminium pads, 4 big copper pads.

- 8 pads for high speed differential lines.

- Design considerations:

- 114 needles (multiple needles for the big pads) are required.

- PCB size is limited by connectors for power supply and infiniband.

- Design priority: rather simple and passive PCB, minimizing the path length of the high speed signals.

- Many thanks to Daniel Esperante for the desing of the probe card.

#### **PROBE CARD: ACTUAL HARDWARE**

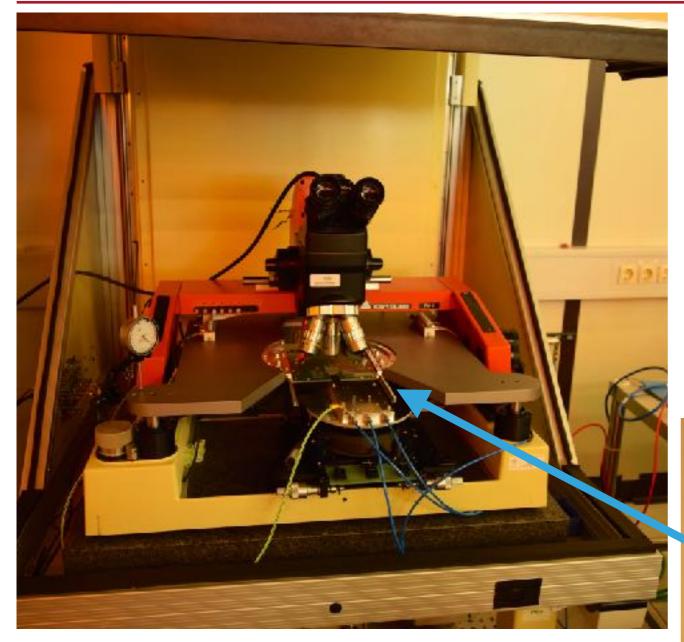

With the help of the micrometer on the left, we apply the desired overtravel (~60 microns).

- Modules are placed with their base jig on the cooling jig and secured with screws and vacuum under the probe card.

- Through the optical microscope we can align the needles with the module and calibrate at what point the touchdown is performed.

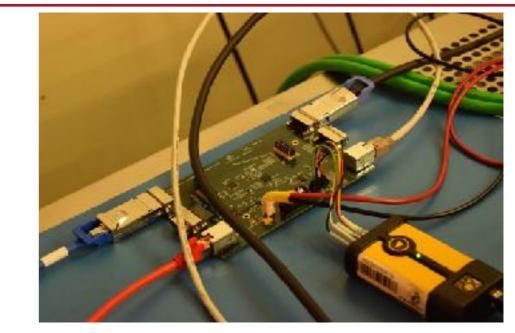

#### PXDTEST6 SETUP @HLL

- 2 probe card A (IF/OB compatible)

- 2 probe card B (IB/OF compatible)

- 1 Power breakout board (LMU\_BB-04)

- 1 LMU power supply (LMUPS-05)

- 1 DHH carrier card (DHHCCv0.03)

- 1 DHE (DHE S/N: 0081)

- 1 JTAG breakout board

- 1 XJLink2 controller

- 1 DAQ PC

- 1 Archiver PC (only PS archived)

- Cables and services

### TESTING PROTOCOL: INCREMENTAL STEPS

- 1. Visual inspection.

- 2. Check of voltages & currents for DHP, SW and DCD-digital.

- 3. Chip configuration: JTAG write & read. Retrieving the IDCODEs, uploading and reading SW sequence, ...

- **4**. Boundary scan.

- 5. Getting the HSL connections.

- 6. Retrieve the testpattern from the DCDB.

- 7. Enable DCD-analog and check voltage & currents.

- Enable and check of DEPFET voltages & currents.

- 9. Read DEPFET pedestals.

- **10.Illuminate the matrix with a laser source.**

#### **TESTS OUTPUT**

- One complete report of each of modules with all the details available at <u>http://elog.mpp.mpg.de/DEPFET/</u>

- A copy of the entry is available also at <u>https://elog.belle2.org/elog/PXD-Mass-Testing/</u>

- A check list section into each one of the modules listed at the HephyDB: <u>http://hephy.at/hephydb/hephydb/</u>

|   |   |                                                     |                                                                                                                                                                         |   | 10.26.12                   |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---|---|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ۲ | 3 | Probecard<br>digital tests                          | Basic health checks with a probecard. Used to decide if the module continues to kapton attachment.                                                                      | ۲ | 2017-<br>05-10<br>14:23:47 | gomis | action repeated 1 times. Second try after the reflow at I2M.                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 1 | 8.1 Check voltages<br>and currents                  | Tests if the connections between ASICs and power<br>supply work.                                                                                                        | ۲ | 2017-<br>05-10<br>14:22:52 | gomis |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 1 | <ol> <li>JTAG write and read</li> </ol>             | Configurate the chips, use automatic configuration<br>script. Change, write and read some parameters.<br>Tests the proper slow control connection and ASIC<br>response. | ۲ | 2017-<br>05-10<br>14:23:01 | gomis |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 1 | 3.3 Boundary scan                                   | Tests proper boundary scan structure, chip ID &<br>communication with JTAG controller, check of the<br>digital connections between boundary cells.                      | ۲ | 2017-<br>05-10<br>14:23:11 | gomis |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | : | 8.4 High speed<br>link stability                    | DHE software to establish the links, IBERT & Random<br>pattern to debug Tests quality of the data transfer<br>connection                                                | ٢ | 2017-<br>05-10<br>14:23:47 | gomis | Units were extremely stable with eye diagrams of ~30 for all DHPTs.                                                                                                                                                                                                                                                                                                                                                                                |

| ۲ | 4 | Probecard<br>analog bests                           | Basic health checks with a probecard. Used to decide if the module continues to kapton attachment.                                                                      | ٢ | 2017-<br>05-10<br>14:40:28 | gomis | action repeated 1 times. Repeating to change the fall in the voltages and currents to "skip". Fall doesn't let you continue with the steps.                                                                                                                                                                                                                                                                                                        |

|   |   | <ol> <li>Check voltages<br/>and currents</li> </ol> | Tests if the connections between sensor and power supply work.                                                                                                          | ٥ | 2017-<br>05-10<br>14:38:52 | gomis |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |   | 1.2 Read DCD<br>pedestals                           |                                                                                                                                                                         | ۲ | 2017-<br>05-10<br>14:39:02 | gomis |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |   | 1.3 Check matrix<br>voltages and<br>currents        |                                                                                                                                                                         | 8 | 2017-<br>05-10<br>14:39:21 | gomis | There seem to be some shorts in between DEPFET voltages: as soon as you power up clear on (12 V), gate off and clear off gain (2.5V) even though they should remain powered off. Also, as soon as you power up clear off (5V), gate on ramps up to 4.8 V (2.3 V on top of the previous 2.5V from the clear on), and gate-on2, gate-on3 also ramp up to 2.2 V. Even with this shorts, we could power all the DEPFET matrix and take some podestals. |

|   |   | 1.4 read matrix<br>pediestals                       |                                                                                                                                                                         | 8 | 2017-<br>05-10<br>14:40:28 | gomis | The matrix was illuminated with a flashlight and the pedestal showed response from all the matrix except the SW1 area.                                                                                                                                                                                                                                                                                                                             |

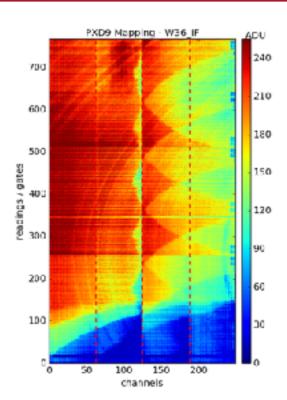

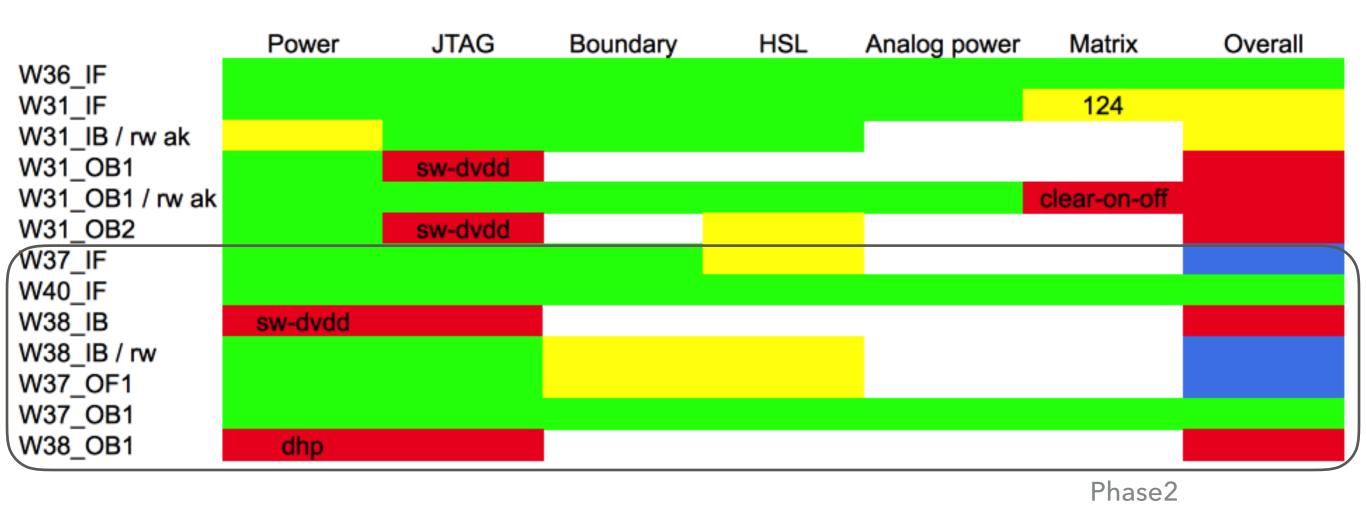

#### **RESULTS: PREPROD. AND PHASE2 MODULES**

10

TEST RESULTS COLOR CODE:

PERFECT

PASSED

MINUR ERRORS / PUSSEDLE TOUCHOUN PROBLEMS

SHOW STOPPER

VIELD (AFTER REWORKS):

IF: 4/4

IB: 2/2

OF: 1/1

OB: 1/4

TOTAL: 8/11 (72%)

TEST RESULTS COLOR CODE:

PERFECT

PASSED

MINOR ERRORS / POSSIBLE TOUCHDOWN PROBLEMS

SHOW STOPPER

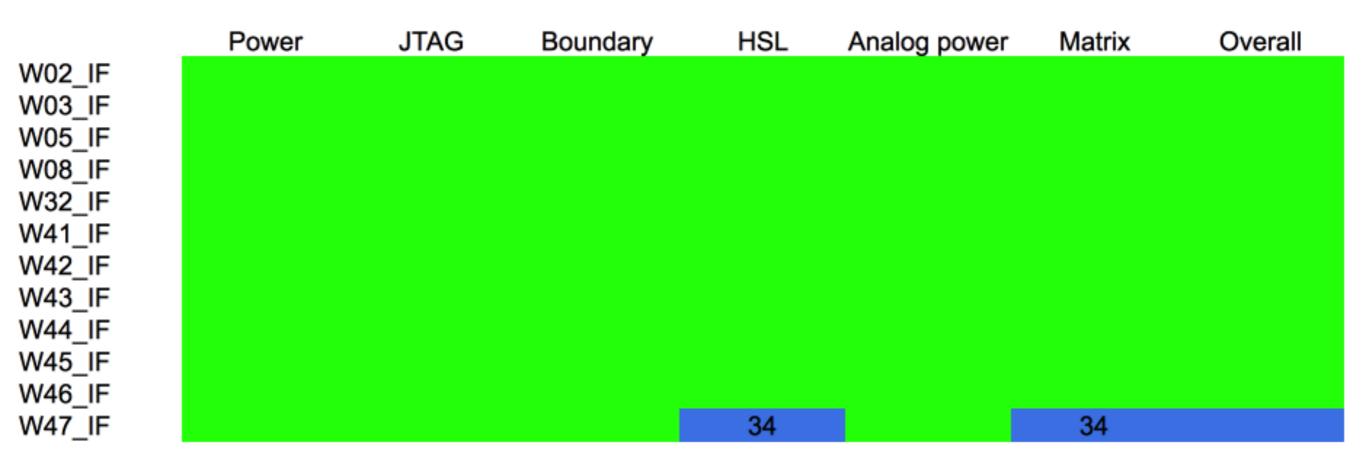

YIELD:

IF: 12/12 (100%)

M. Hensel (<u>mhe@hll.mpg.de</u>) @ Belle II PXD workshop - 22/01/2018

11

#### **RESULTS: PHASE3 OF MODULES**

|                                                                        | Power   | JTAG | Boundary | HSL | Analog power | Matrix | Overall |  |

|------------------------------------------------------------------------|---------|------|----------|-----|--------------|--------|---------|--|

| W08_OF2                                                                |         |      |          | 13  |              | 13     |         |  |

| W09_OF1                                                                |         |      |          | 13  |              | 13     |         |  |

| W09_OF2                                                                |         |      |          |     |              |        |         |  |

| W11_OF1                                                                |         |      |          |     |              |        |         |  |

| W11_OF2                                                                |         |      |          | 13  | dcd-avdd     |        |         |  |

| W12_OF1                                                                |         |      |          | 12  |              | 12     |         |  |

| W32_OF1                                                                |         |      |          | 123 |              | 12     |         |  |

| W32_OF2                                                                |         |      |          | 12  |              |        |         |  |

| W33_OF1                                                                |         |      |          |     |              | 124    |         |  |

| W33_OF2                                                                |         |      |          | 400 |              | 123    |         |  |

| W41_OF1                                                                |         |      |          | 123 |              | 123    |         |  |

| W43_OF1                                                                | sw-dvdd |      |          |     |              |        |         |  |

| W44_OF1                                                                | sw-dvdd |      |          |     |              |        |         |  |

| W44_OF2<br>W45_OF1                                                     | sw-dvdd |      |          |     |              | 124    |         |  |

| W45_OF2                                                                | dhp     |      |          |     |              | 124    |         |  |

| W45_0F1                                                                | unp     |      |          | 12  |              |        |         |  |

| W46_OF2                                                                |         |      |          | 12  |              |        |         |  |

| W40_012                                                                |         |      |          | . – | -            |        |         |  |

| TEST RESULTS COLOR CODE:                                               |         |      |          |     |              |        |         |  |

| PERFECT PASSED MINOR ERRORS / POSSIBLE TOUCHDOWN PROBLEMS SHOW STOPPER |         |      |          |     |              |        |         |  |

| YIELD:                                                                 |         |      |          |     |              |        |         |  |

| OF: 11/16 (69%)                                                        |         |      |          |     |              |        |         |  |

#### **RESULTS: PHASE3 OB MODULES**

|                          | Power         | JTAG        | Boundary         | HSL       | Analog power | Matrix    | Overall |  |

|--------------------------|---------------|-------------|------------------|-----------|--------------|-----------|---------|--|

| W03_OB1                  |               |             |                  |           |              |           |         |  |

| W05_OB1<br>W06_OB1       |               |             |                  |           |              |           |         |  |

| W08_OB1                  |               |             |                  |           |              |           |         |  |

| W08_OB2<br>W09_OB1       | sw-dvdd       |             |                  |           |              |           |         |  |

| W09_OB2                  |               |             |                  |           |              |           |         |  |

| W12_OB1                  |               |             |                  |           |              |           |         |  |

| W12_OB2<br>W32_OB2       |               |             |                  |           |              |           |         |  |

| W33_OB1                  |               |             |                  |           |              |           |         |  |

| W42_OB1<br>W42_OB2       |               |             |                  |           |              |           |         |  |

| W44_OB1                  |               |             |                  |           |              |           |         |  |

| W44_OB2                  |               |             |                  |           |              |           |         |  |

| W45_OB2<br>W46_OB1       |               |             |                  |           |              |           |         |  |

| W46_OB2                  |               |             |                  |           |              |           |         |  |

| TEST RESULTS COLOR CODE: |               |             |                  |           |              |           |         |  |

| PE                       | RFECT   PASSE | D   MINOR E | RRORS / POSSIB   | LE TOUCHD | OWN PROBLEMS | SHOW STOP | PER     |  |

|                          |               |             |                  |           |              |           |         |  |

|                          |               |             | YIEL<br>0B: 15/1 |           |              |           |         |  |

|                          |               |             |                  | 0 (74/0)  |              |           |         |  |

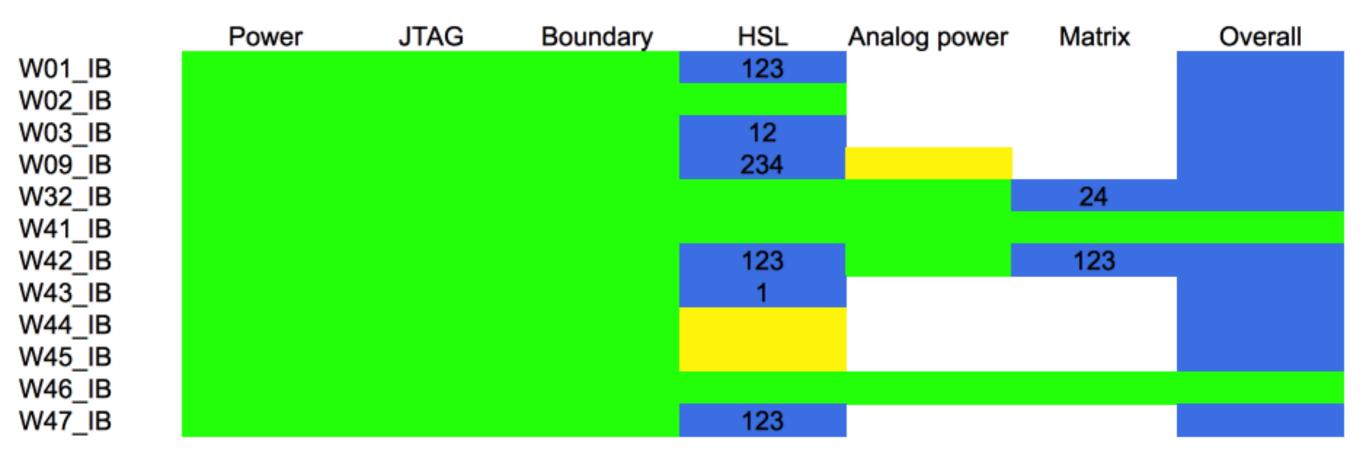

### **RESULTS: OVERVIEW**

The yield (modules without show stoppers, and including reworks) of all the probe card tests performed to the date is accounted in the following table:

|          | IF              | IB              | OF             | OB             |

|----------|-----------------|-----------------|----------------|----------------|

| Preprod. | 2/2             | 1/1             | 0              | 0/2            |

| Phase2   | 2/2             | 1/1             | 1/1            | 1/2            |

| Phase3   | 12/12           | 12/12           | 11/16          | 15/16          |

| Total    | 16/16<br>(100%) | 14/14<br>(100%) | 12/17<br>(71%) | 16/20<br>(80%) |

- A total of 67 modules were tested, with 9 of them showing errors which were catalogued as show stoppers. Out of this 9 errors: 6 are switcher related, 2 dhp related, 1 dcd related and 1 DEPFET matrix related.

- Modules like W38\_IB (the one with the rotated switcher) could be debugged with the probe card and repaired before kapton attachment.

#### COMMENTS AND LESSONS LEARNED

- In some of the modules the needles are able to make a really good contact, and a really stable connection is achieved (W31\_OB1 ran without losing any HSL for almost an hour). Whereas in others getting the HSL was really difficult (ie. W37\_IF).

- In most of the cases, testing an IF/OB module with the probe card A was straightforward, meanwhile IB/OF modules used to take more of an effort.

- For an optimal contact, planarity between the probe card and the module is crucial. In this sense, the jig used to house the module can really affect the measurement.

- Instead of using a unique jig for each of the modules (as it was intended), we found jigs that worked fairly for each type of modules and kept using those for all the measurements.

- To improve the contact between the needles and the pads, we perform consecutive touchdowns in the same spot in order to scratch a bit the surface on the pad and allow for better contact.

- Regularly cleaning and polishing the needles of the probe card also helped with their perfomance.

- Occasionally, when the performance was really deteriorated and cleaning didn't help, they were shipped to the manufacturer (PTSL) for a refurbishment.

#### SUMMARY

- Two probe card designs to test the PXD9 modules have been produced and are in operation.

- A testing protocol for the mass production was developed and tested with real modules.

- Ideally we can fully operate all the modules before kapton attachment.

- Unfortunately, not all the touchdowns are optimal, and sometimes we can't operate the module fully.

- In total we were able to test 67 modules, spotting show stopper errors in 9 of them. And allowing for the refurbishment of one of the modules.

## THANKS FOR YOUR ATTENTION

# BACKUP

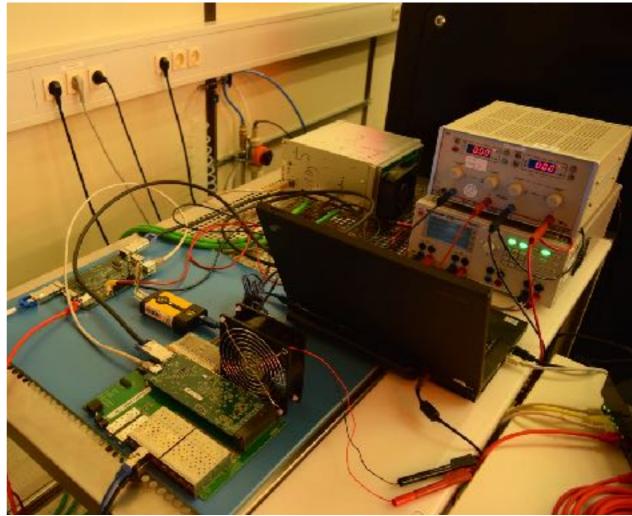

#### PXDTEST6 SETUP

- 2 probe card A (IF/OB compatible)

- 2 probe card B (IB/OF compatible)

- 1 Power breakout board (LMU\_BB-04)

- 1 LMU power supply (LMUPS-05)

- 1 DHH carrier card (DHHCCv0.03)

- 1 DHE (DHE S/N: 0081)

- 1 JTAG breakout board

- 1 XJLink2 controller

- 2 Bench power supplies

#### PXDTEST6 SETUP

- 2 Infiniband cables, 2 green power cables, a glenair cable, RJ45 cables and banana cables

- 2 SFP adaptors

- 2 Fans to cool the DHE and the LMU PS

- 1 Cooling block (water cooled) with a vacuum pipe

- 2 Network switchers

- pxdtest6 SL7 pc: using the latest software release available at mid november 2016 (for stability/feature reasons), steering the modules with ini files (no DB)

- pxdtest5 SL7 pc: up-to-date software release, compatible with the DB

- edet2 SL7 pc: set up as archiver