# 4<sup>th</sup> generation **Specialized Synchrotron Radiation Source** SSRS-4 project **Control and diagnostic systems**

**Timur Kulevoy**

The work is carried out under the support of Russian Ministry of Education and Science contract 14.616.21.0088 at 24\11\2017 (RFMEFI61617X0088)

-HAT

CREMLIN Closing Workshop, 5-6 June, 2018, DESY

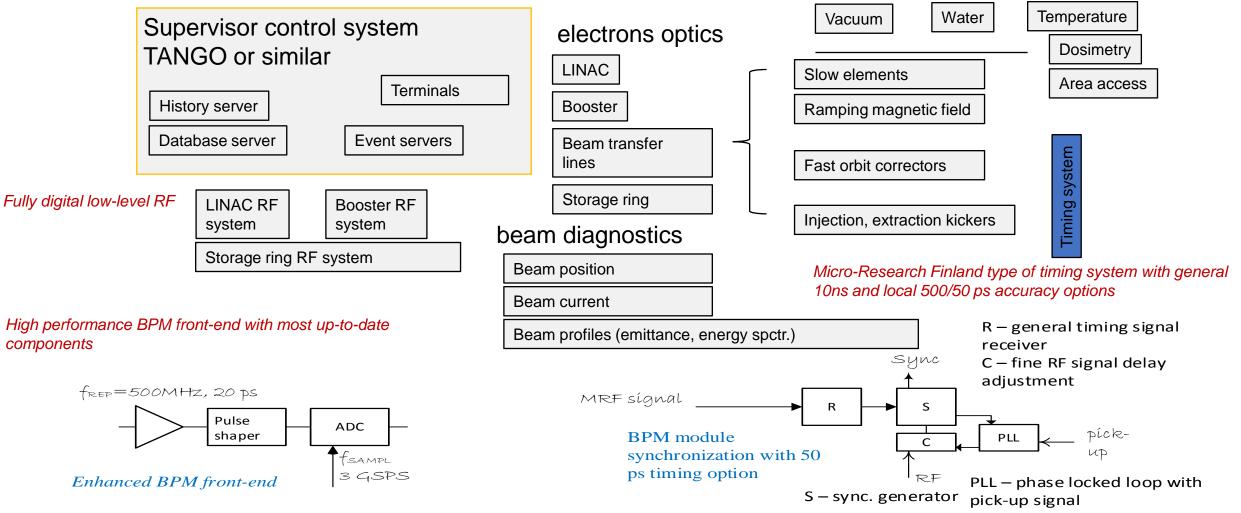

#### Bird's eye view at SSRS4 control and diagnostics

Engineering systems

- Classical SCADA architecture

- Uses mainly Ethernet network

- Dedicated network for BPMs

- Open source middleware solutions and so on

#### ACS Hardware infrastructure

#### **Control system**

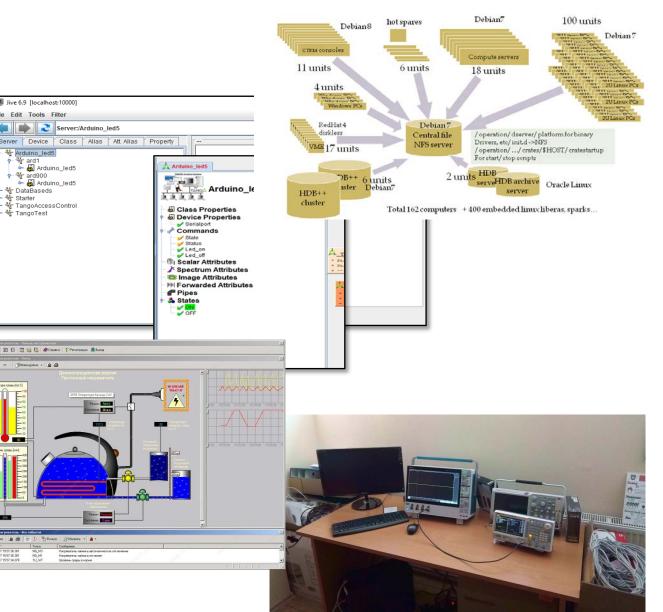

- We have carefully investigated documentation for some wellknown control systems such as TANGO and EPICS.

- To fill more familiar to TANGO a small plant of Arduino controllers and few applications under TANGO control had been developed.

- For the moment there is a intermediate decision to develop SSRS-4 control system and define overall design rules on the base of common SCADA standards and experience of numerous TANGO-based systems

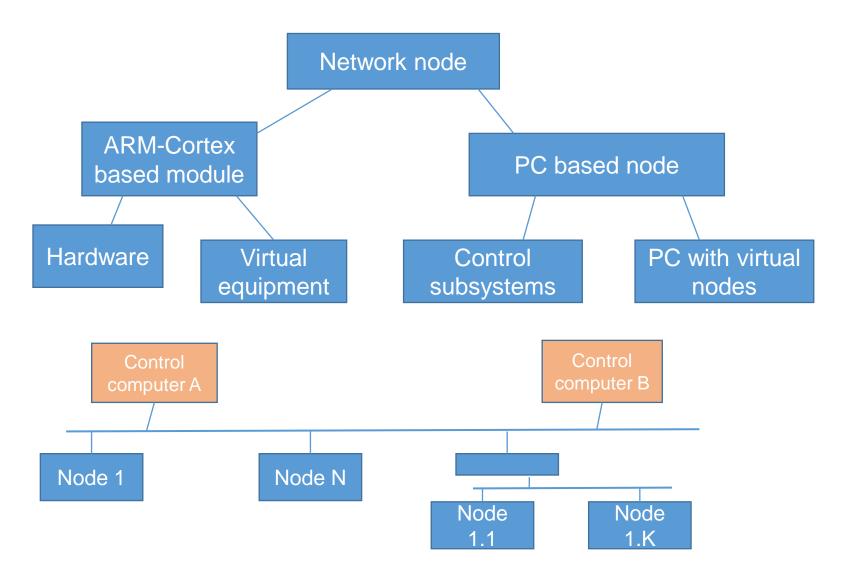

## **Distributed equipment**

- A network node model is under development

- The Ethernet and the correspondent protocols are considered as a main data transport

- We are developing templates, rules and code examples for desktop computers and ARM-based controllers

#### SSRS-4 Control System Databases Expected SSRS-4 SCADA implementation

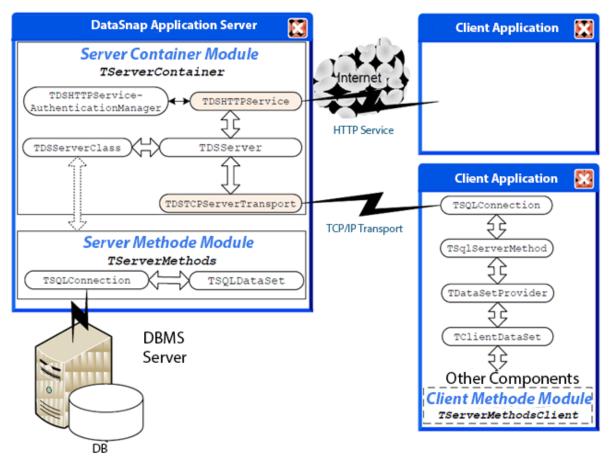

- It is supposed to use the architecture of a multitiered client/server application in which an additional middle tiers between the client application and database server is added. This middle tier is frequently named application server. This allows different client applications to use the same data, while ensuring consistent data logic. It also allows for smaller client applications, because much of the processing is off-loaded onto the middle tier.

- A standard tool for building multi-user applications in RAD Studio is the DataSnap package, which allows clients to remotely invoke server methods and is optimized for server operation with many clients.

- That tool use JSON form of messages. JSON is a text string with a hierarchical dataset of key / value.

### **BPM for 4-th generation accelerators**

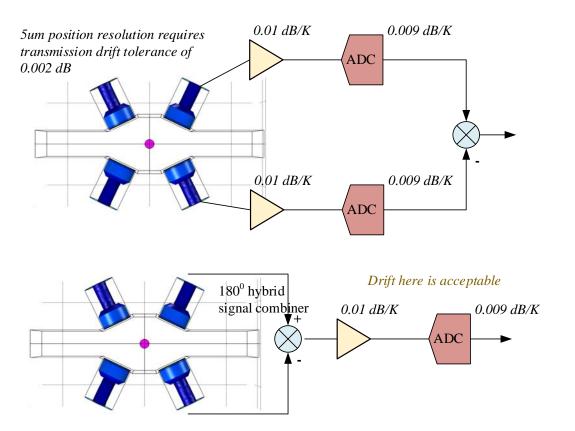

- Specific requirement for low-emittance accelerators is a long-term stability of the BPM measurements. The requirements are 5 um position accuracy in the axial region.

- We are not warrying too much about mechanical tolerances.

- The thermal drift and aging of amplifiers and ADCs lead unacceptable measurement errors.

- Signal to noise ratio allows signal manipulation before amplification stage.

- Therefore we are going to test a scheme with passive wide band signal combiner (see figure on the right)

#### **BPM electronics**

- **BPM** functionality depends on the budget!

- From functionality point of view an RF sampling (6GSPS) ADC embedded into FPGA package is able to solve most of **BPM** tasks.

- But such module as well as 14 bit, ullet**3GSPS ADCs probably make the** electronic too expensive.

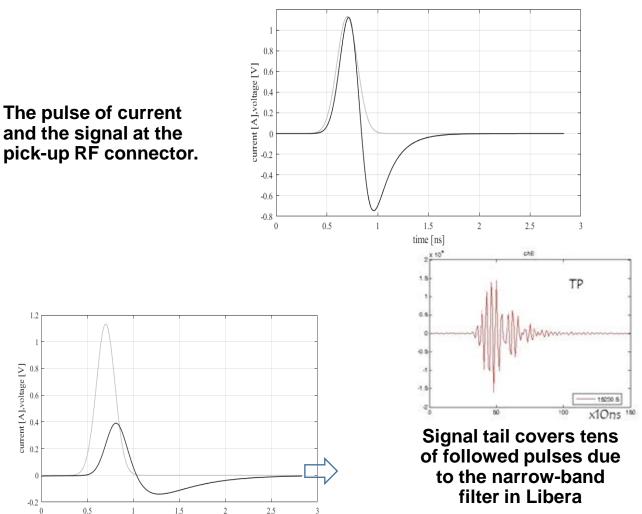

- We could formulate a minimal requirements for electronics. Bunch by bunch operation requires 500 MHz bandwidth to separate adjacent bunches from each other(see figure on the right). It also needs ADC with sampling rate 500 MSPS or higher.

- Affordable solution will be 1.5 GSPS ADC with 2 GHz analog bandwidth.

The same signal as at top but after a low-pass filter. Small portion of power of the signal leaks to the next bunch. Therefore we demand for processing a frequency band at least 500 MHz

1.5

time [ns]

## **BPM.** Prototyping of electronics

- As a first step we choose a semicommercial solutions for proving hardware and software solutions.

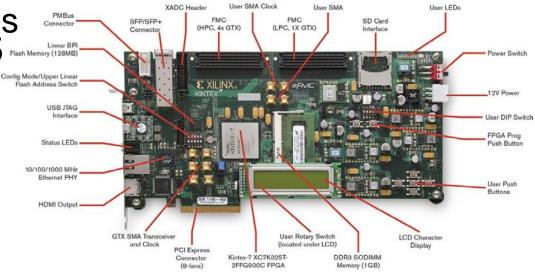

- There are numerous evaluation boards which allows combining high performance ADCs and FPGA. We chose Abaco systems ADC board as a companion of Xilinx KC705 refer Evaluation board.

- Analog electronics is under construction in the lab