Johannes Zink

# OUTLINE

- 1. State of the art Zone3 Connection in MTCA.4

- 2. High-frequency diagnostic applications

- 3. Direct-sampling digitizer boards (FMC/AMC)

- 4. New Zone3 classification for MTCA.4

# **Digitizing of RF Signals in MTCA.4**

- high-resolution digitizer (AMC)

- analog front-end (AFE) on RTM side

- down conversion of high frequency signals  $\rightarrow$  Zone3 differential

- Zone3  $\rightarrow$  sampling on the AMC-board

- IF sampling at 50 MHz

struck innovative

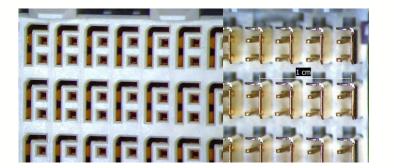

### **Zone3 Differential Connector**

- differential pair connections between AMC and RTM board

- digital and analog Zone3 classes

- J30 contains power, management, clock and digital data signals

- J31 contains analog differential inputs and outputs (AMC view)

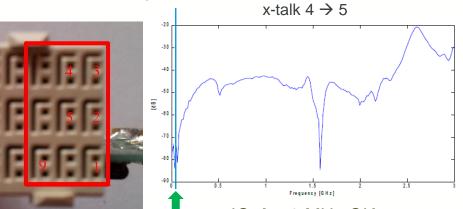

### DISADVANTAGE:

cross talk between differential pairs

### non-IQ $\rightarrow$ 50 MHz OK

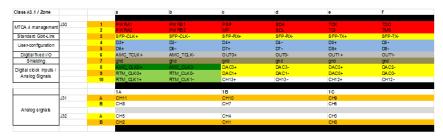

#### AMC ZONE 3 CONNECTOR PIN ASSIGNMENT RECOMMENDATION

| lass A1 / Zone           |     | a                 | b               | c             | d            | e             | f             |

|--------------------------|-----|-------------------|-----------------|---------------|--------------|---------------|---------------|

|                          |     |                   |                 |               |              |               |               |

| MTCA.4 management        | J30 | 1 PWRA1           | PWRB1           | PS#           | SDA          | TCK           | TDO           |

|                          |     | 2 PWRA2           | PWRB2           | MP            | SCL          | TDI           | TMS           |

| PGA / Standard Gbit-Link |     | 3 D0+ / SFP-CLK+  | D0- / SFP-CLK-  | D1+ / SFP-RX+ | D1- /SFP-RX- | D2+ / SFP-TX+ | D2- / SFP-TX- |

| PGA User-configuration   |     | 4 D3+             | D3-             | D4+           | D4-          | D5+           | D5-           |

|                          |     | 5 D6+             | D6-             | D7+           | D7-          | D8+           | D8-           |

| PGA / Digital fixed I/O  |     | 6 D9+ / AMC TCLK+ | D9- / AMC TCLK- | D10+ / OUT0+  | D10- / OUT0- | D11+ / OUT1+  | D11-/ OUT1-   |

| Shielding                |     | 7 gnd             | gnd             | gnd           | gnd          | gnd           | gnd           |

| Digital clock inputs     |     | 8 RTM_CLK4+       | RTM_CLK4-       | RTM_CLK2+     | RTM_CLK2-    | RTM_CLK5+     | RTM_CLK5+     |

|                          |     | 9 RTM CLK0+       | RTM CLK0-       | RTM CLK3+     | RTM CLK3-    | RTM CLK1+     | RTM CLK1-     |

| Shielding                |     | 10 gnd            | gnd             | and           | gnd          | gnd           | gnd           |

|                          |     |                   |                 |               |              |               |               |

| Analog signals           | J31 | 1 CH9_PA+         | CH9 PA-         | DAC0+         | DAC0-        | CH9 TF+       | CH9_TF-       |

|                          |     | 2 CH8 TF+         | CH8 TF-         | gnd           | gnd          | CH8 PA+       | CH8 PA-       |

|                          |     | 3 CH7 PA+         | CH7 PA-         | DAC1+         | DAC1-        | CH7 TF+       | CH7 TF-       |

|                          |     | 4 CH6_TF+         | CH6_TF-         | gnd           | gnd          | CH6_PA+       | CH6_PA-       |

|                          |     | 5 CH5 PA+         | CH5 PA-         | DAC2+         | DAC2-        | CH5 TF+       | CH5 TF-       |

|                          |     | 6 CH4 TF+         | CH4 TF-         | gnd           | gnd          | CH4 PA+       | CH4 PA-       |

|                          |     | 7 CH3 PA+         | CH3 PA-         | DAC3+         | DAC3-        | CH3 TF+       | CH3 TF-       |

|                          |     | 8 CH2_TF+         | CH2_TF-         | gnd           | gnd          | CH2_PA+       | CH2_PA-       |

|                          |     | 9 CH1 PA+         | CH1 PA-         | DAC4+         | DAC4-        | CH1 TF+       | CH1 TF-       |

|                          |     | 10 CH0 TF+        | CH0 TF-         | gnd           | and          | CH0 PA+       | CH0 PA-       |

Table 1 : Pin assignment of Class A1, AMC side view

#### 7<sup>th</sup> MicroTCA Workshop, Hamburg 2018

4

# **Solutions**

© ElectronicDesign

ERNI © ERNI

J.Zink, 2018-12-06, Hamburg

# **High Frequency Diagnostic Applications**

bunch passing a cavity, H.Padamsee

Klystron melt-down after arc, TV transmitter

#### **High-Order Modes**

- electron bunch excites HOM in cavity, signals from HOM couplers can provide informations about:

- beam position, beam charge, cavity alignment

- "Electronics for High-Order Modes Detection", Uros Mavric et al.

#### Klystron Lifetime Management

- detection of dangerous Klystron states:

- gun arcs, loss of beam, loss of RF signal

- Model Based Fast Protection System For High Power RF Tube Amplifiers Used At European XFEL Accelerator, Lukasz Butkowski

#### RF based Bunch Arrival Time Monitor

- direct sampling of pick-up signals

- reduction of bandwidth from 40 GHz to 2.4 GHz

- roughly estimate bunch arrival time

- adjust electro-optical BAM

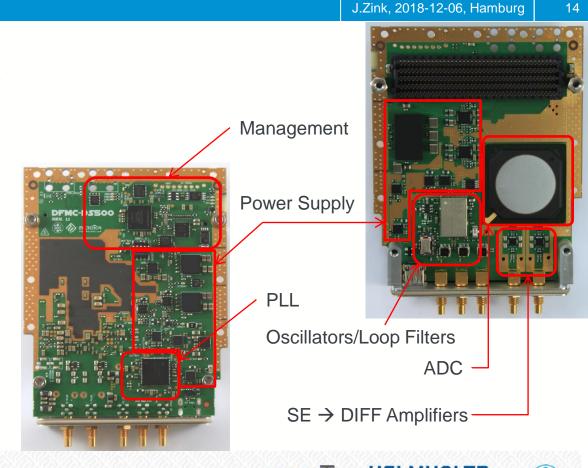

# DFMC-DS800

- to ANSI/VITA 57.1 standard

- 8.5 mm stacking height

- 12-Bit, 800 MSP/s Dual Ch., 1.6 GSP/s Single Ch.

- ADC input bandwidth: 2.7 GHz

- fully diff. amplifier LS bandwidth: 4.8 GHz

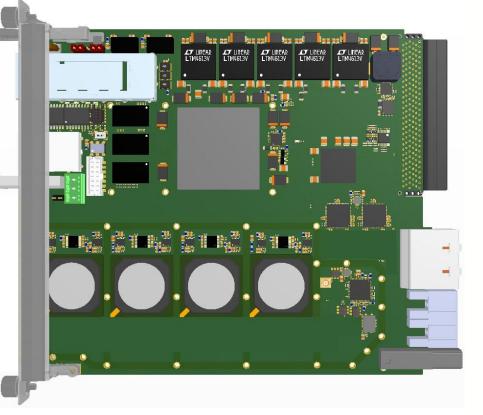

# DAMC-DS800

- 4x 12-Bit, 800 MSP/s Dual Ch., 1.6 GSP/s Single Ch. ADCs

- ADC input bandwidth: 2.7 GHz

- fully diff. amplifier LS bandwidth: 4.8 GHz

- XCZU7EG F1517 ZynQ MPSoC Dual/Quad-Core ARM Cortex-A53

- Mali-400 Based GPU

- Signal feed in via Zone3 and Front Panel

- Quad SFP, COAX IO, HARLINK LVDS at FP

- First Batch Q3/2019

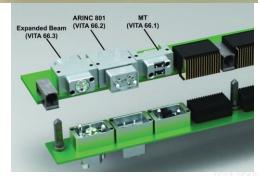

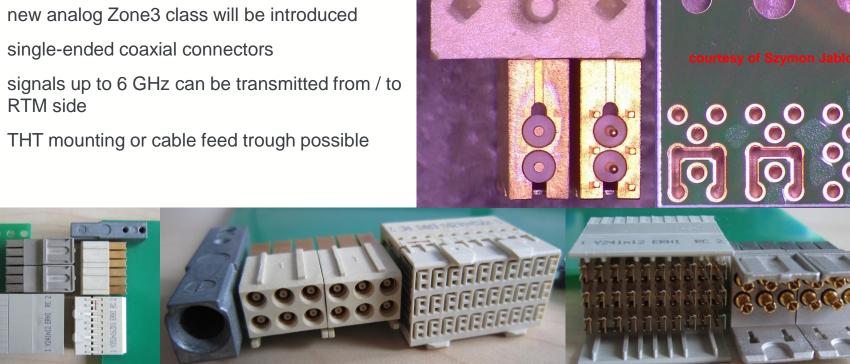

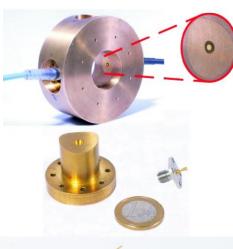

# **New Zone3 Class - Preliminary**

J.Zink, 2018-12-06, Hamburg

- new analog Zone3 class will be introduced •

- single-ended coaxial connectors •

- signals up to 6 GHz can be transmitted from / to ٠ RTM side

- •

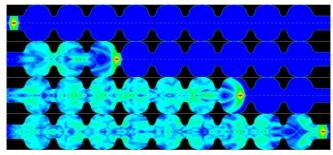

# **New Zone3 Class - Preliminary**

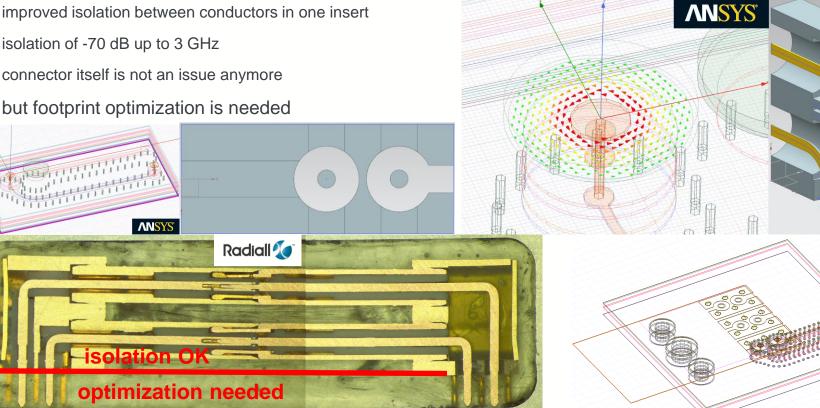

- improved isolation between conductors in one insert •

- •

- connector itself is not an issue anymore •

- but footprint optimization is needed •

special thanks to Stanislav Chystiakov

Images used courtesy of ANSYS, Inc.

#### 7<sup>th</sup> MicroTCA Workshop, Hamburg 2018

J.Zink, 2018-12-06, Hamburg

**ANSYS**<sup>®</sup>

DESY.

11

Zone 3 Connector Pin Assignment Recommendation for Analog Applications for AMC/ $\mu$ RTM Boards in the MTCA.4 standard

#### FEATURES

MTCA.4 management zone:

· Power, I<sup>2</sup>C, optional JTAG support

Analog signal transmission zone

12 channel DC-coupled single-ended IO (input) signals

Digital clock signal transmission zone:

- 2 AC-coupled differential inputs for low-jitter clock signals

- 1 LVDS output clock signal

User signal transmission zone:

- · 6 LVDS inputs / outputs for user-configuration

- 3 LVDS outputs with fixed output direction

- · Optional dual high-speed link

Zone shielding:

· Supports ground shielding between zones

#### APPLICATIONS

- AMC / µRTM board design in MTCA.4 standard

- · Multi-channel analog-to-digital converters

- Multi-channel signal shaper

- Multi-channel sensor readout and output

- Analog signal conditioning boards

- Low-jitter clock signal sampling and clock recovery

#### GENERAL DESCRIPTION

This Class A3.1 pin assignment definition of the Zone 3 connector in the MTCA.4 standard is a recommendation mainly for AMC and  $\mu$ RTM boards transferring up to 12 analog signals over the Zone 3 connector. This analog class is designed for a three row ADF and two six pin coaxial Zone 3 connectors. The main goal is to classify the undefined Zone 3 pin assignment for applications to achieve a high compatibility between AMC and  $\mu$ RTM boards.

This Class A3.1 pin assignment requires a common µRTM management implementation to make AMC and µRTM boards compatible. Appropriate management interface templates for this Class are available on http://mtca.desy.de.

#### AMC ZONE 3 CONNECTOR PIN ASSIGNMENT RECOMMENDATION

7<sup>th</sup> MicroTCA Workshop, Hamburg 2018

Table 1 : Pin assignment of Class A3.1, AMC side view

### Class A3.1

- J30 like A1 and A2 classes

- J31 / J32 Up to 12 single-ended RF signals

### OUTLOOK

- finishing simulation and research

- waiting for prototypes of improved CoaxiPack2

- finish Class A3.1 specification early next year

J.Zink, 2018-12-06, Hamburg

12

# ACKNOWLEDGEMENTS

M. Fenner, S. Jablonski, F. Ludwig, U.Mavric

Thank you for your attention.

J.Zink, 2018-12-06, Hamburg

13

DESY.

# **Diagnostic Applications**

# **Bunch Arrival Time Monitor**

- direct sampling of pick-up signals

- reduction of bandwidth from 40 GHz to 2.4 GHz

- roughly estimate bunch arrival time

- adjust electro-optical BAM

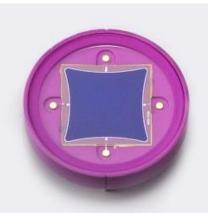

# Photodiode / PSD

- fast photo diode and PSD readout

- beam position measurments

- light intensity measurements

#### © HAMAMATSU

C HAMAMATSU

# DFMC-DS800

- ADC input bandwidth: 2.7 GHz

- fully diff. amplifier LS bandwidth: 4.8 GHz

- no anti-aliasing filter present

- variants with up to 3.2 GSP/s

DESY.

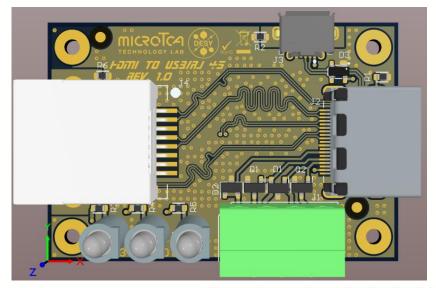

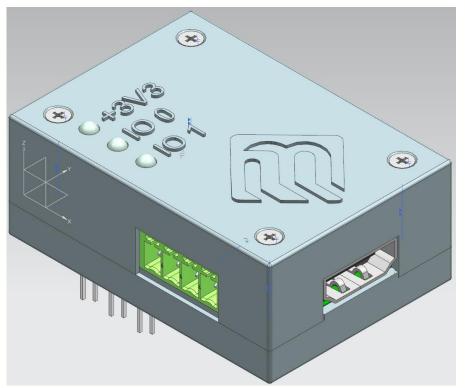

# **Break-Out board**

- 4 LVDS (differential) pairs → can act as input or output (trigger/control signals, 100 MHz)

- 2 single-ended bits input / ouput

- serial interface (debugging and testing)

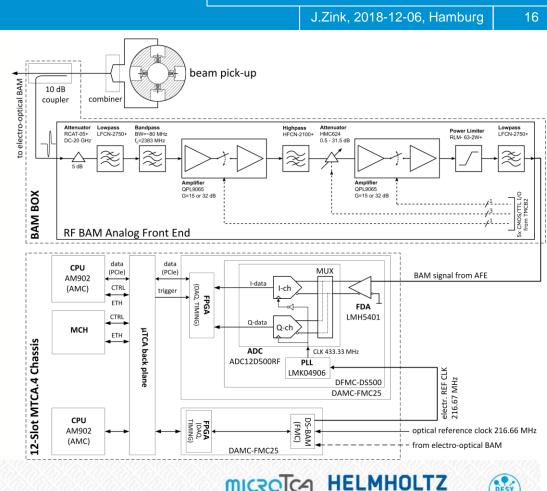

# **Coarse BAM Channel**

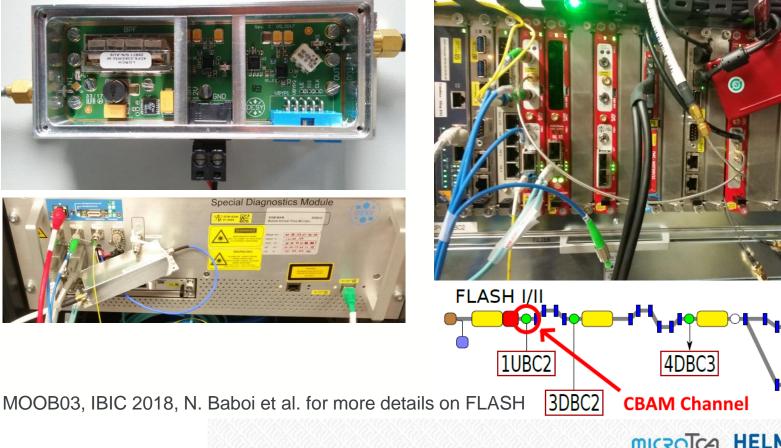

- coarse BAM Channel planned in FLASH

- coarse BAM channel in addition to electro-optical BAM [1,2] → automatically adjust optical delay lines

- uses same combined high-bandwidth pick up [3] signals (40 GHz)

- analog front end bandpass filters the pick up signal

- bunch charges can vary from 20 pC up to 1 nC, which requires a dynamic range of about 34 dB

- sampling (DFMC-DS500/DAMC-FMC25) and processing in MTCA.4 crate

### **CBAM Channel in FLASH**

J.Zink, 2018-12-06, Hamburg

17

J.Zink, 2018-12-06, Hamburg

12-Slot MTCA Crate

18

DESY.

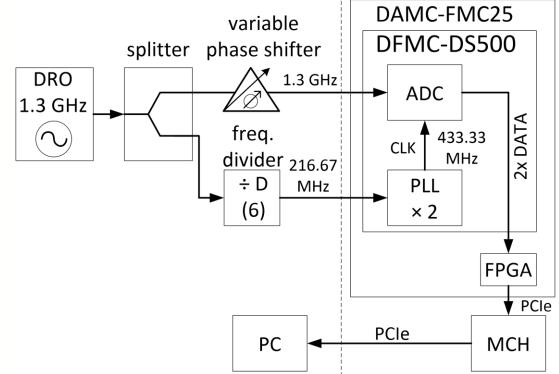

# CBAM DS500 Test Setup

complex high-bandwidth pick up signal

- testing ADC performance under ideal conditions with reduced signal bandwidth

- undersampling 1.3 GHz carrier with phase synchronous ADC clock → produces DC signal

- timing error converts into amplitude error

- roughly estimate the timing accuracy

# **Results**

J.Zink, 2018-12-06, Hamburg

19

- recorded 1.6M samples

- fitting normal distribution with:

- $\mu$  = -2.93117e-21s  $\sigma$  = 726.36 fs

- timing error (p2p): 7 ps

- timing error (rms): 726 fs

- results are not outstanding but also not bad

- meet the requirements of ~1 ps