# The Digital BPM development for HEPS project in IHEP

HuiZhou-Ma, ShuJun-Wei, Qiang-Ye, YanFeng-Sui, YaoYao-Du, Yufei-Ma, XingEr-Zhang, XiYang-Huang, YanHua-Lu, Jing-Yang, JunHui-Yue, JianShe-Cao

> On behalf of Beam Instrumentation Group of IHEP 7<sup>th</sup> MicroTCA Workshop 4-6 DEC 2018 DESY

- 1. Why we need to build the digital BPM electronics

- 2. The BPM requirement of HEPS project

- **3.** Digital BPM pre-research in HEPS-TF project

- 4. Summary and Acknowledgement

## 1. Why we need to build the digital BPM electronics

1, Beam orbit stability is key parameter of modern light sources, it can affect performances of accelerator and synchrotron light beam stations.

2 , Beam users always hope beam orbit changes within 5% to 10% of beam size. For HEPS, its typical beam size is 3µm, so we need to control beam orbit stability within 0.3µm, so the resolution of beam position measurement is need to meet the requirement of 0.1µm.

3, Commercial product is good as the beam position measurement, but the price is also "good", and its original code is not open to users, so further development based on machine requirement and study to them is impossible.

4, Home-made electronics can develop technologies and reduce the cost.

# 2. The BPM requirement of HEPS project

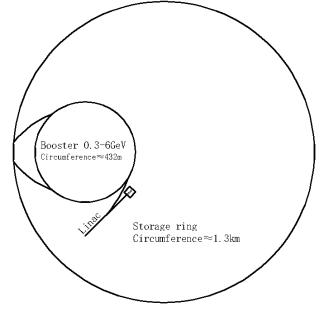

The High Energy Photon Source (HEPS) is designed as an ultra-low emittance ring-based synchrotron radiation light;

- About fourteen beamlines will be constructed in Phase I of the project;

- Storage ring circumference:

1296m, 48\*7BA

- Energy: 6GeV

- Emittance<60pm.rad

- Current: >200mA

- Construction:2019-2025

Schematic of HEPS Complex

## **The Digital BPM requirement of HEPS project**

#### HEPS BPM quantities

|               | <b>BPM Quantities</b> |

|---------------|-----------------------|

| Linac         | 7                     |

| Transfer Line | 3*10=30               |

| Booster       | 80                    |

| Storage Ring  | 48*12=576             |

| SUM           | 693                   |

#### **Storage ring BPM Parameters**

|                   | DBPM@HEPS            |

|-------------------|----------------------|

| Turn by Turn Data | <u>1μm @220kHz</u>   |

| FA data           | 0.3 <u>μm @22KHz</u> |

| COD data          | <u>0.1μm @10Hz</u>   |

# 3. Digital BPM pre-research in HEPS-TF(Test Facility) project

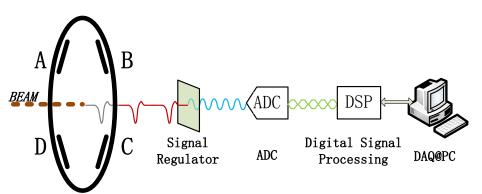

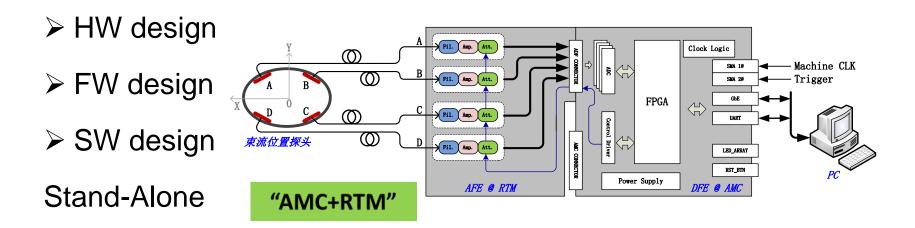

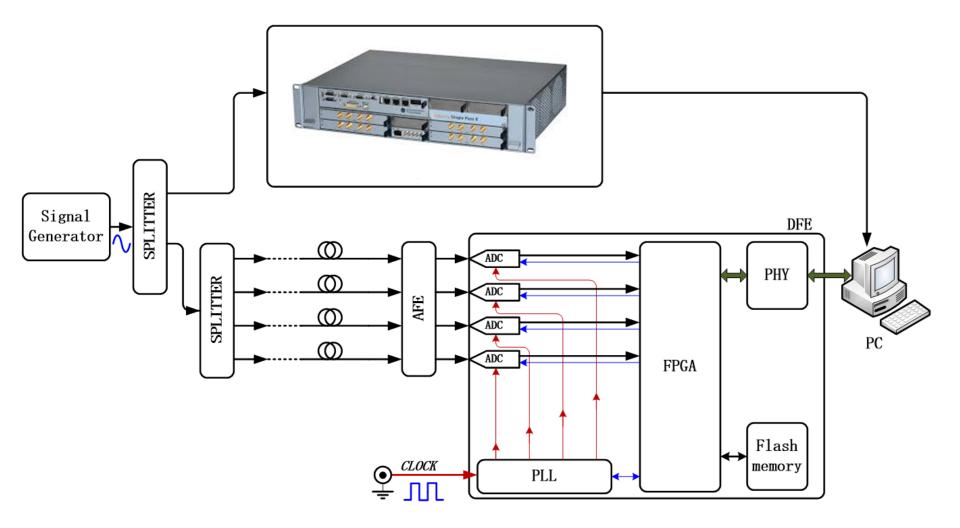

- System structure

- Hardware design

- Algorithm of Firmware

- Software design

- Digital BPM testing

For the HEPS will have been built several years later, so we develop the DPBM prototype with BEPCII parameters, and DBPM system is tested in BEPCII. And main work include 3 parts:

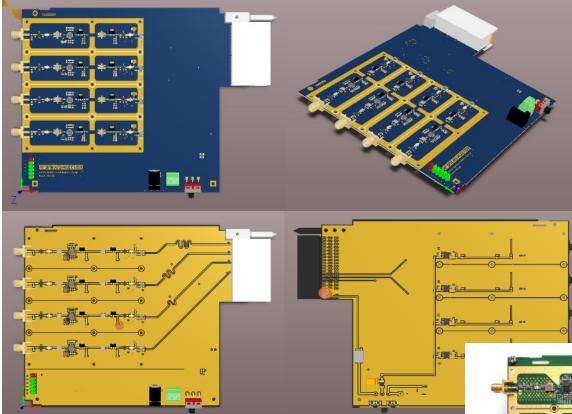

## RTM Module design(by Yaoyao Du)

Design objective:

✓ Low Noise design✓ Low power consumption

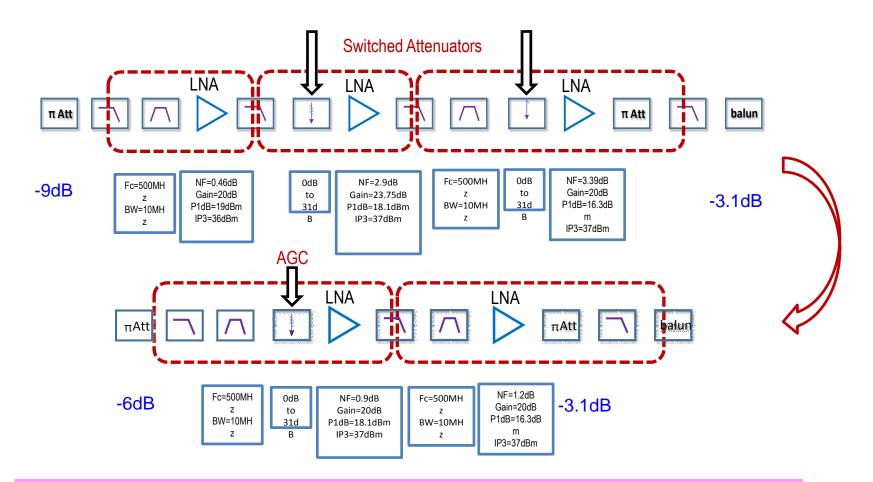

## **DBPM\_RTM function block**

- 1、Two LNAs are enough

- 2、 The place of Attenuator is designed carefully

- 3、 Attention to the Impedance matching & Noise

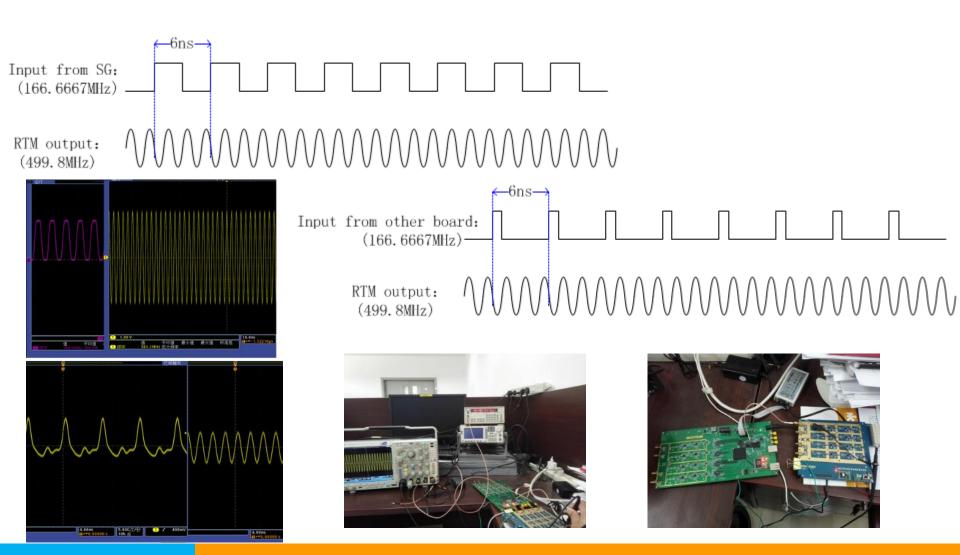

## **DBPM.RTM ADC clock commissioning**

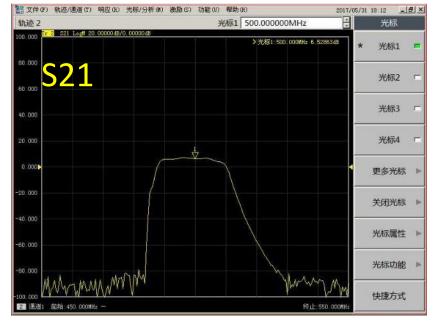

## **DBPM.RTM S-Parameter Characterization**

#### **Receiver S-Parameter Characterization**

#### **S21-Parameter Characterization**

The performance of band pass filter is good!

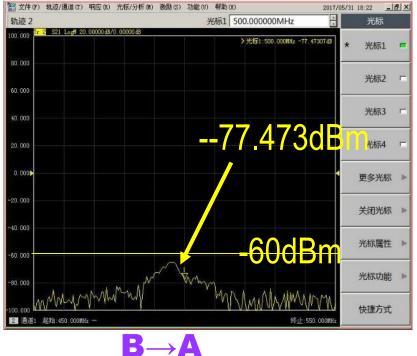

## **DBPM.RTM Channel to Channel Isolation**

6.5dBm→-78.8dBm

6.5dBm→-77.47dBm

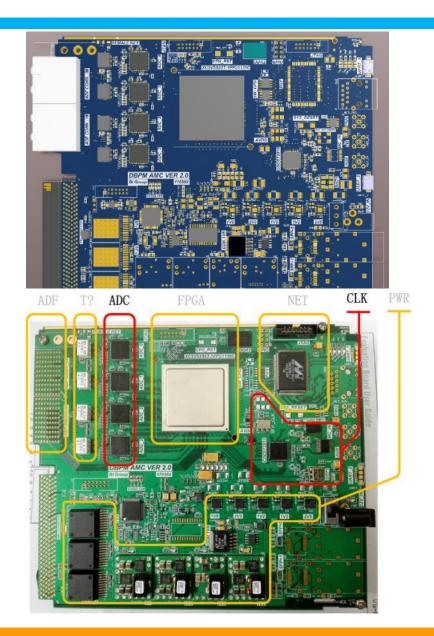

## AMC Hardware design(by Shujun Wei)

- Power Regulator

Clock Logic

FPGA Logic

- ADC Logic

- NET Logic

- Other Logic...

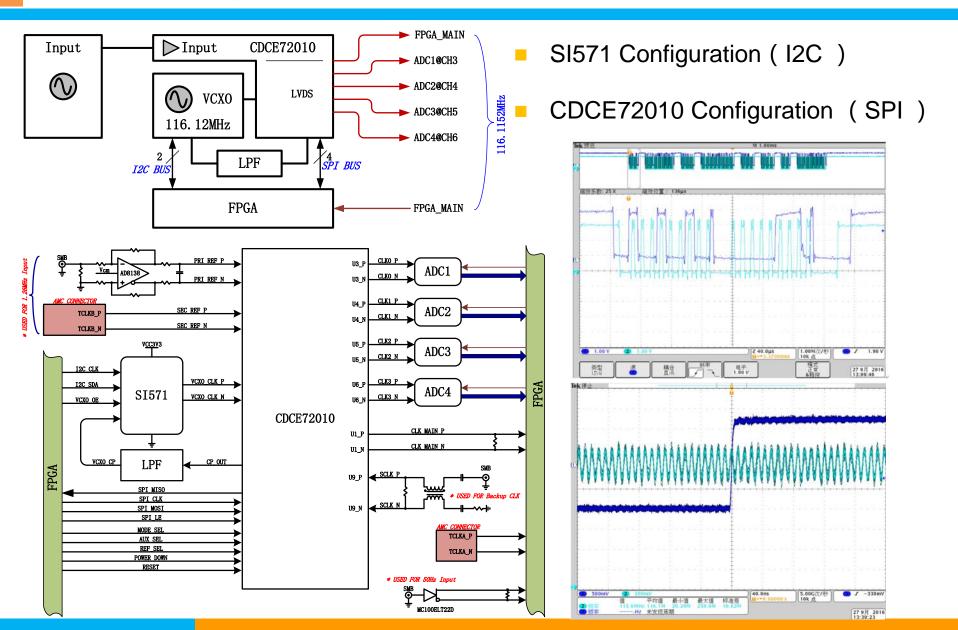

## **Clock logic Scheme**

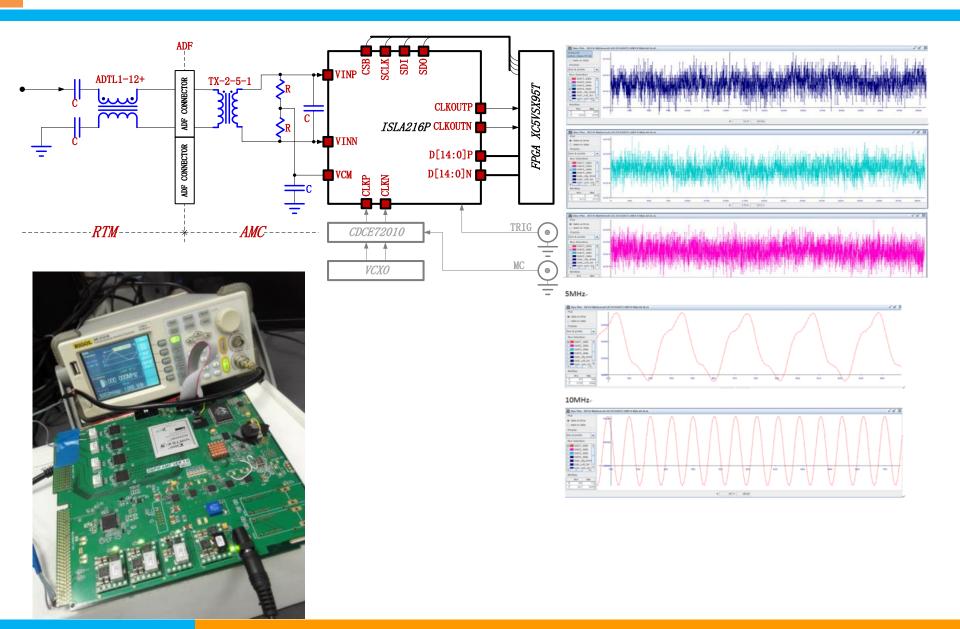

## **ADC Logic Scheme**

## **3.3 Algorithm of Firmware design**

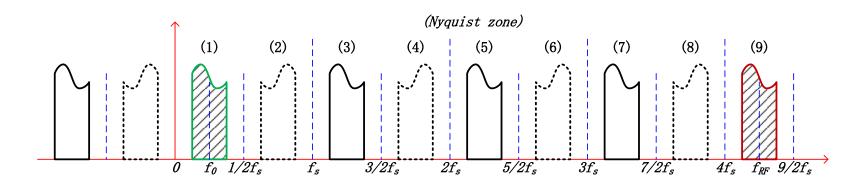

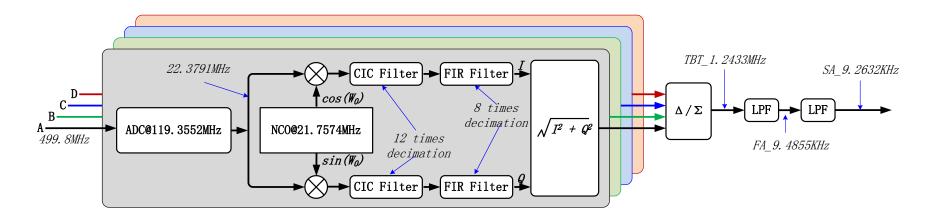

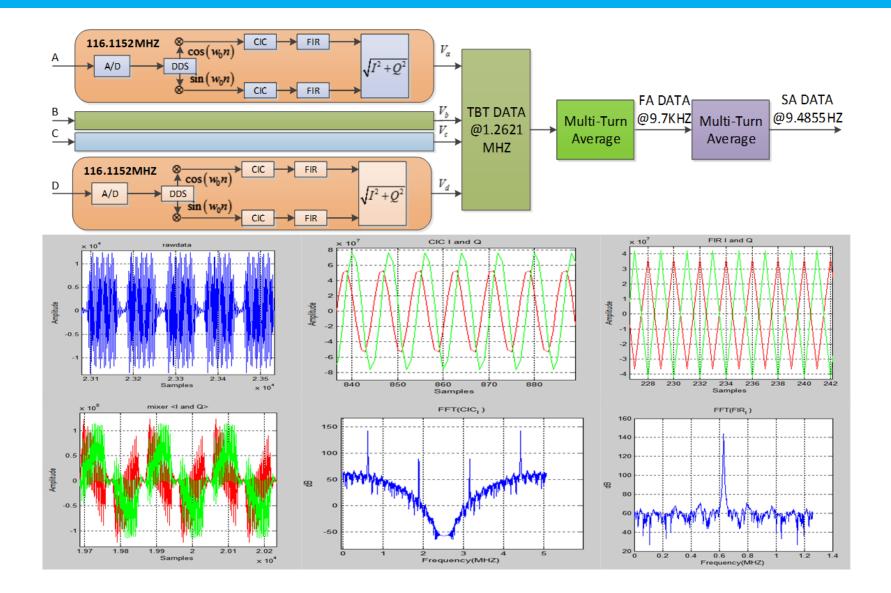

# MATLAB simulation (by YuFei Ma)HDL Implementation

## **MATLAB** simulation

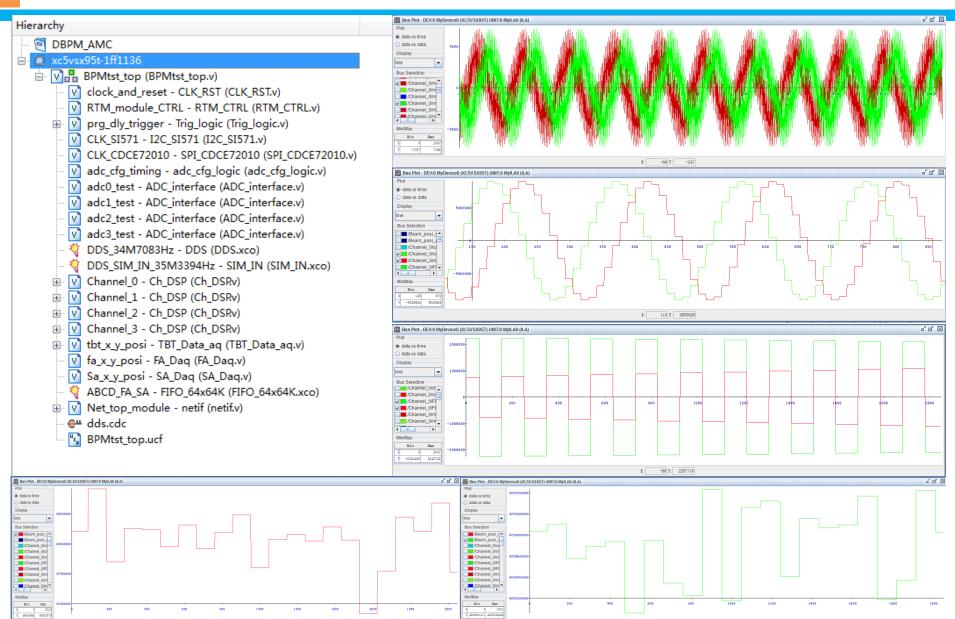

## **HDL Implementation**

## DFT Algorithm(Fang Liu)

Hilbert transformer method. (Qiang Ye)

Time domain dynamic window integrating method. (YuFei Ma)

## **3.4 DBPM Software design**

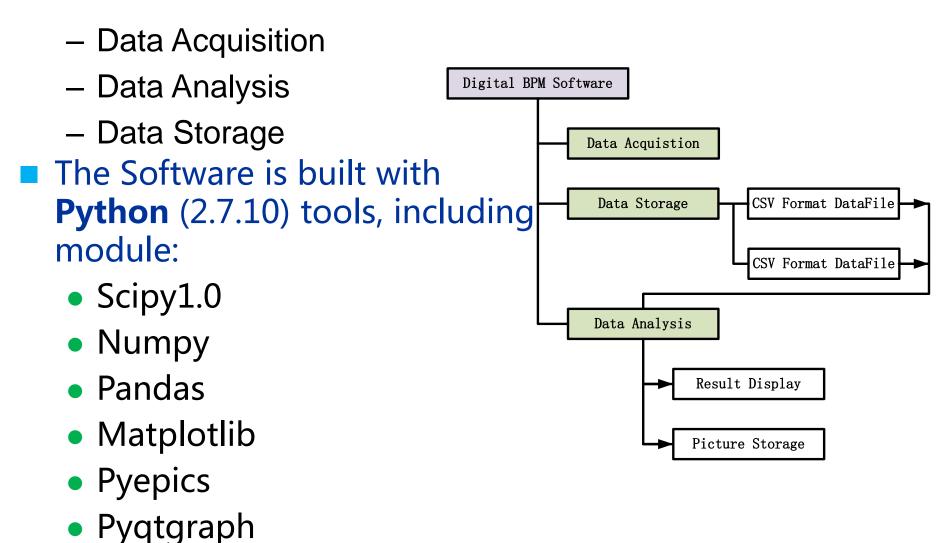

## Software framework include 3 main part:

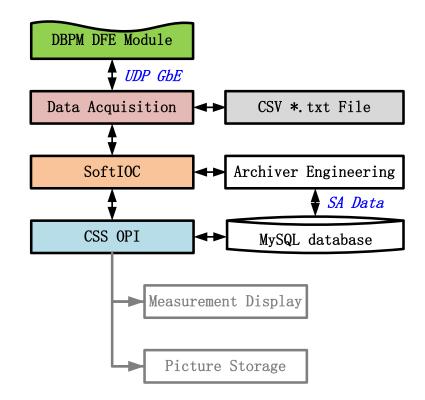

## **Data Acquisition Module**

## SA Data Acquisition function block.

- Data Acquisition control logic

- Write/Read CSV file logic

- EPICS IOC Logic

- Data base logic

- Graphical User Interface

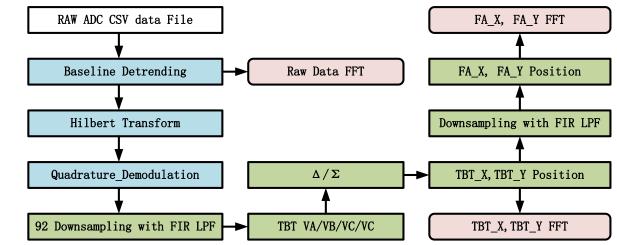

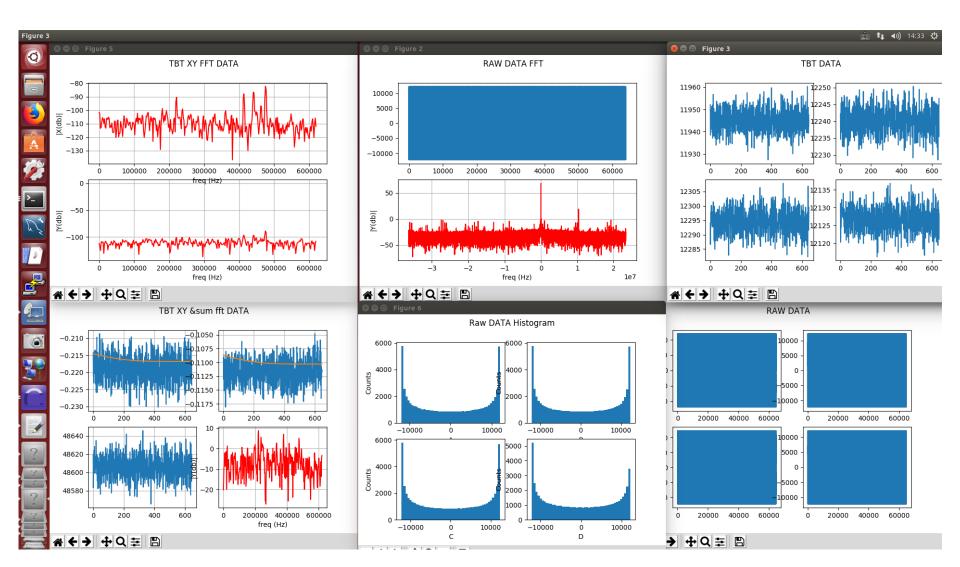

## **Data Analysis Module**

Data Analysis function block.

- Data Hilbert Transform and Quadrature Demodulation

- TBT and FA Position calculation

- FFT Analysis.

Note: The function is designed to verify the result processed in FPGA.

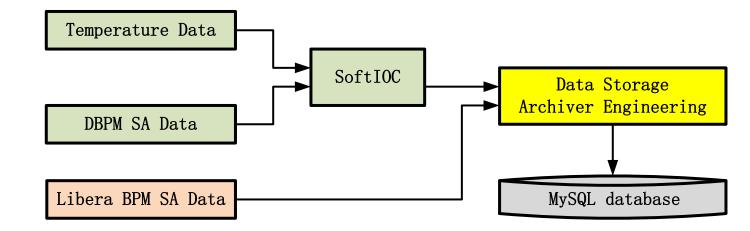

## **Data Storage Module**

Two Methods are used in Data Storage:

- CSV txt format file

- RDB Archiver Engineering MySQL database

## **3.5 Digital BPM testing**

# **RAW ADC data and Analysis**

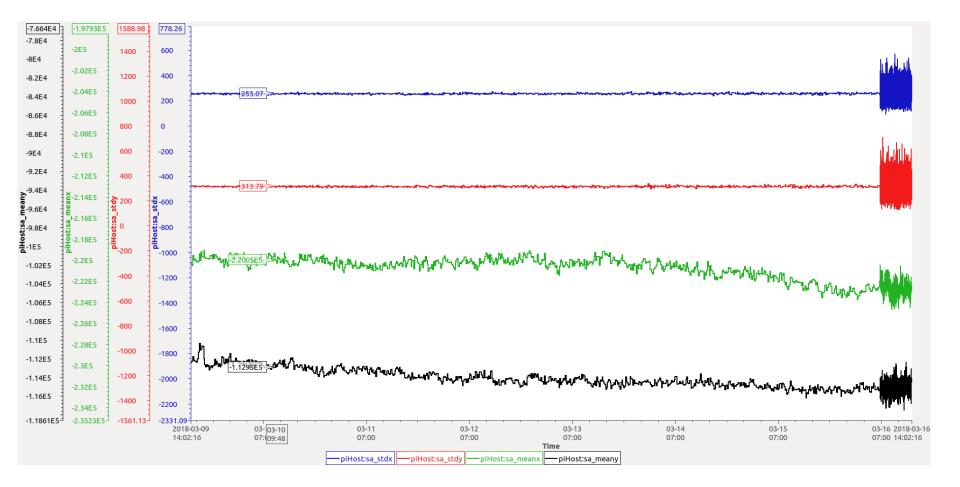

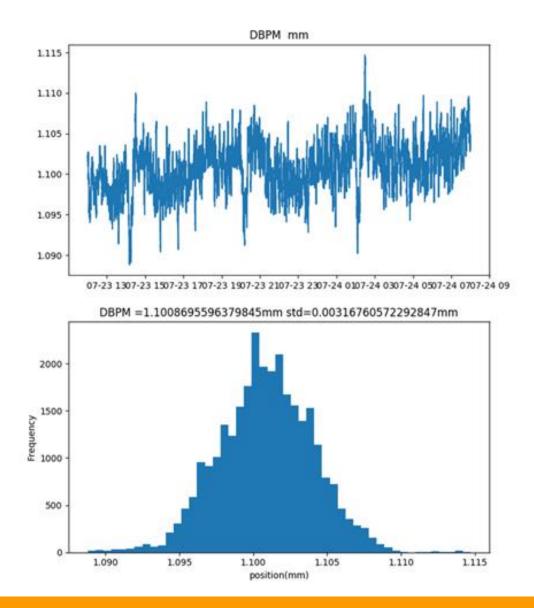

# Long term testing for 7 days

### **Have Passed the Final acceptance tests**

**# ← →** ⊕ Q 至 🖹

x=33.093 y=-12720.3

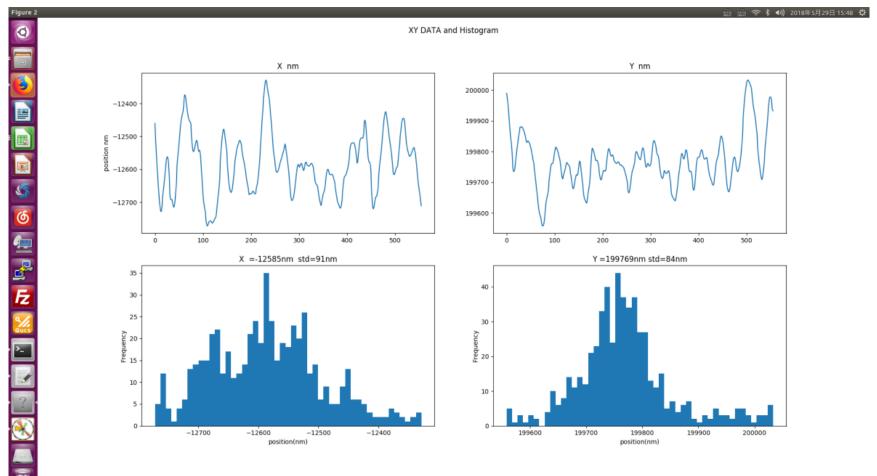

## **24 hours test with beam in BEPCII**

# 4. Summary and Acknowledgement

- Digital BPM Electronics hardware has been designed carefully and had been tested in laboratory;

- The algorithm of BPM based on storage-ring has been developed;

- The digital BPM electronics have been tested with the real beam on BEPCII.

- A lot of work is on the way:

- The HW, FW are to be optimized and improved;

- Single pass BPM, BXB BPM is on schedule;

- BPM's Calibrating and testing system are to be developed.

- MicroTCA platform for DBPM in future.

During our Digital BPM electronic development, we got many experts help, and we would like to take this opportunity to express our sincere appreciation to them:

- NSLSII

- SIRIUS

- SSRF

- HLS

- I-Tech

- ...

# Thanks for your attention