## **Microelectronics and ASIC developments**

**IHP** – Technology Department

Mehmet Kaynak & Roland Sorge

05.03.2019

"Matter and Technologies", Helmholtz Institute Jena

innovations for high performance microelectronics

# IHP – Innovation for High Performance Microelectronics

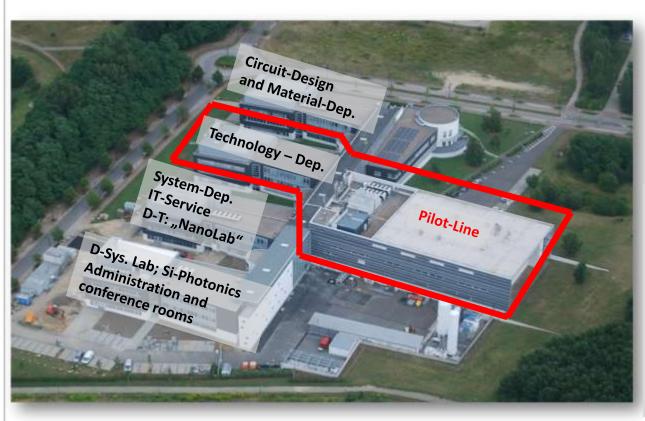

### Institute of the Leibniz Association

- 320 employees from 27 countries, including 134 scientists

- Founded in 1983 → R&D 8" pilot line since 2000

- Shareholder is the state of Brandenburg

- Member of the "Research Fab Microelectronics Germany" (FMD) → cooperation with Fraunhofer VµE & FBH

#### Financing 2017

- Basic funding from the German and local government: ~29 Mio. Euro (including basic invest)

- Third party funds: ~19 Mio. Euro (e.g. EU-Projects, MPW-LVP, FMD)

## IHP – Innovation for High Performance Microelectronics

### Research programs

- Material Research

- More than Moore technologies

- Analogue circuit design for mm-wave & THz

- System design for broadband communication

### **IHP SiGe BiCMOS Pilot Line**

### Cleanroom area

1000m<sup>2</sup> class 1 for 100wspw

### Technology & operation

RF SiGe BiCMOS @ 24/7 mode

### Technology level

8" @ 0.25μm and 0.13μm

### **IHP Wafer Bonding Pilot Line**

- Temporary & permanent wafer bonding

- Metal bonding (wafer-level)

- Ultra-thin silicon BiCMOS technologies

- Wafer-level integration of microfluidics

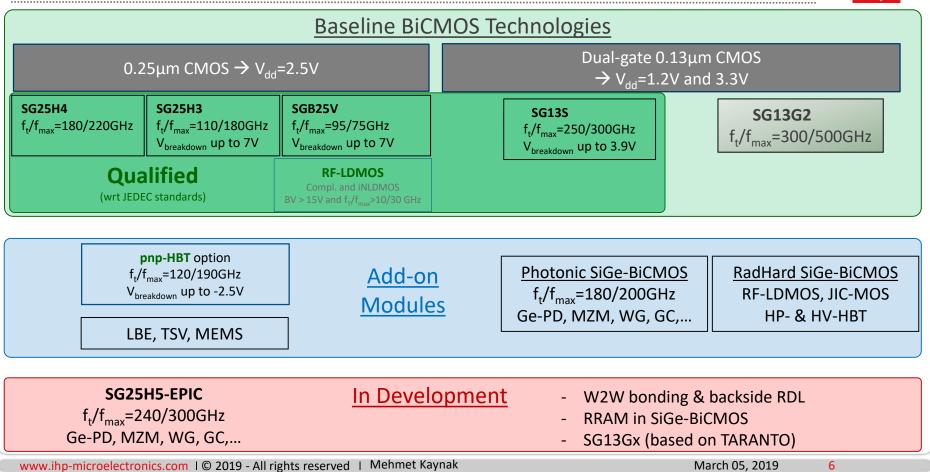

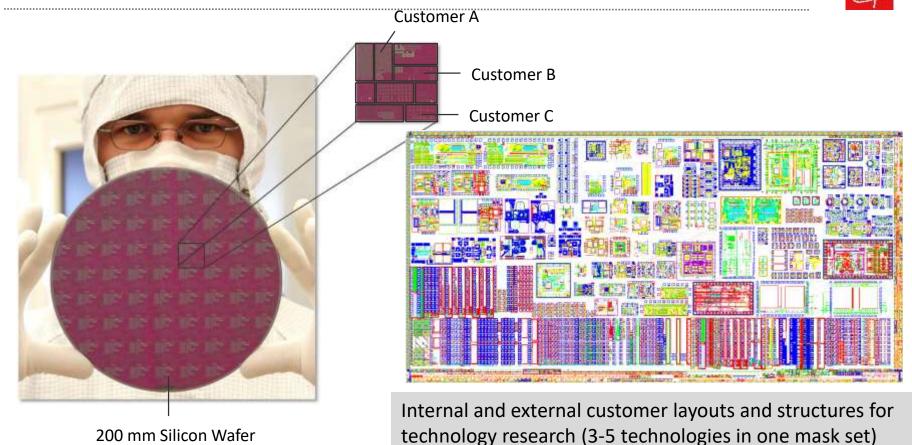

## IHP SiGe-BiCMOS Technologies for MPW and LVP

## Service Approach → Multi Project Wafer & Prototyping & LVP

www.ihp-microelectronics.com | © 2019 - All rights reserved | Mehmet Kaynak

## IHP as a Bridge between Universities and Industry

### **Academic cooperation**

- Virtual laboratories between universities and IHP for exchanging scientist & know-how

- Enable access to R&D infrastructure

- · Bradam . Sabancı Currently 9 runnig JointLabs (national & international) 100 Universities IHP Industry Joint Labs Joint Projects System Design Joint Research Contract Research **Circuit Design** Pilot Line Research Education MPW & Small Series Basic Technology Joint Professorships Spin Offs Settlements Materials Research

www.ihp-microelectronics.com | © 2019 - All rights reserved | Mehmet Kaynak

echnische

Hochschule Wildau Technical University

of Applied Sciences

POZNAN UNIVERSITY OF TECHNOLOGY

Iniversitesi

b-tu

Brandenburgische

Technische Universit:

Cottbus - Senftenberg

miversita

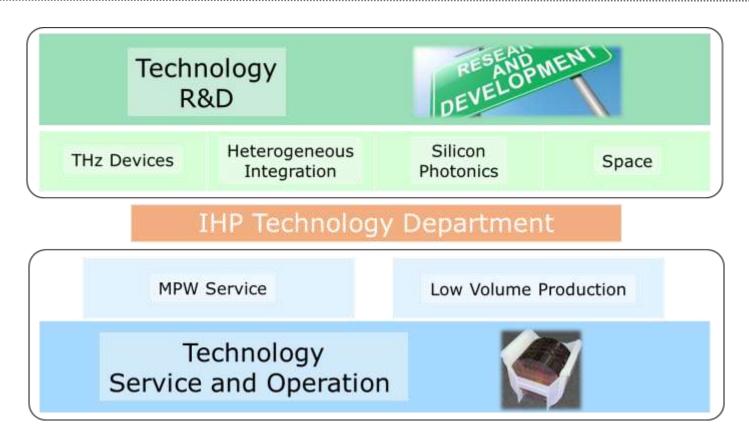

# Summary of R&D Activities under Technology Department

www.ihp-microelectronics.com | © 2019 - All rights reserved | Mehmet Kaynak

......

March 05, 2019

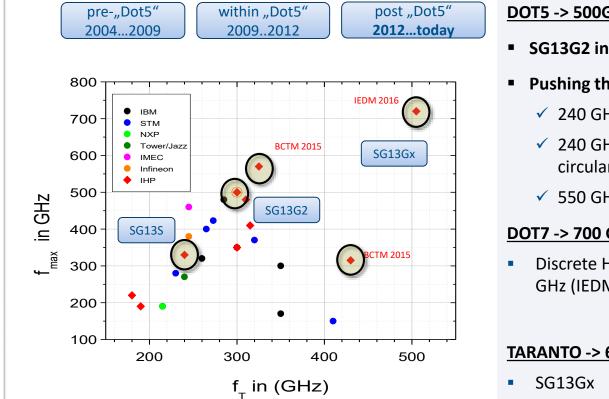

## SiGe-HBT & BiCMOS Performance Evolution

### DOT5 -> 500GHz Fmax

- SG13G2 in production today

- Pushing the limit designs:

- ✓ 240 GHz RF chip-set + package (EuMW ,16)

- ✓ 240 GHz radar transceiver + package + circular polarization (EuMC '15)

- ✓ 550 GHz full Si CT scanner (IRMMW-THz '16)

### DOT7 -> 700 GHz Fmax

Discrete HBT with  $f_T > 505$  GHz and  $f_{max} \approx 720$ GHz (IEDM 2016)

### TARANTO -> 600 GHz Fmax BiCMOS

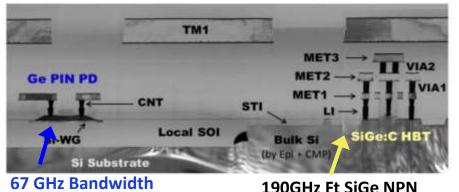

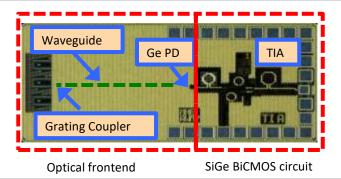

## SG25 SiGe BiCMOS + Photonics

Germanium Photo Diode

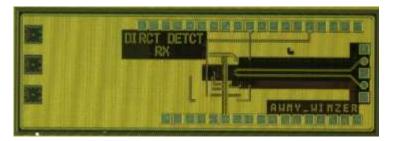

56Gbps Data rate receiver for 400Gbit Ethernet *M.Kroh et al. ECOC 2016*

Localized SOI areas for photonics

Bulk like areas for BiCMOS

**Monolithic Photonic-Electronic**

Full feature set BiCMOS

Same Silicon wafer

- Common BEOL and modular process flow

- Silicon Proven PDKs

54Gb/s silicon photonics receiver, M.H.Eissa et al. ESSCIRC 2016

www.ihp-microelectronics.com | © 2019 - All rights reserved | Mehmet Kaynak

#### www.ihp-microelectronics.com | © 2019 - All rights reserved | Mehmet Kaynak

Electrode

Signal Line

Encapsulation during wafer process

## SG13 SiGe BiCMOS + RF-MEMS

- BEOL embedded RF-MEMS technology for mm-wave switches / varactors

- Low insertion loss (~0.7 dB) and high isolation from 30 GHz to above 150 GHz

BICMOS (C

RF-MEMS packaging based on wafer-level encapsulation

### RF-MEMS Switch Technology

**Application Examples**

90 GHz Passive Imaging

- Tx/Rx Switches

- Phase Shifters

- Tunable Filters

.....

### 30 GHz SatCom

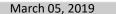

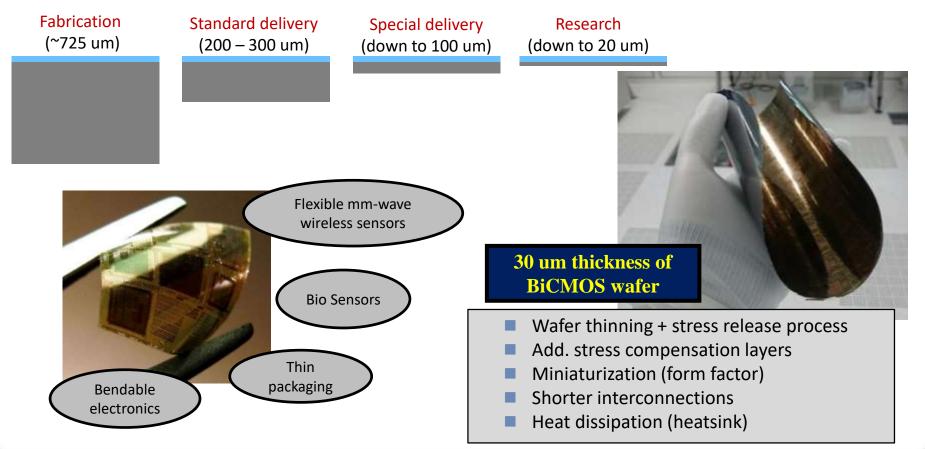

## Ultra-Thin Silicon BiCMOS Technology

www.ihp-microelectronics.com | © 2019 - All rights reserved | Mehmet Kaynak

# Remove GND bond wires for chip-2-package interface

- Simplify packaging/assembly process

- Minimize parasitic inductance and resistance

**BSM**

www.ihp-microelectronics.com | © 2019 - All rights reserved | Mehmet Kaynak

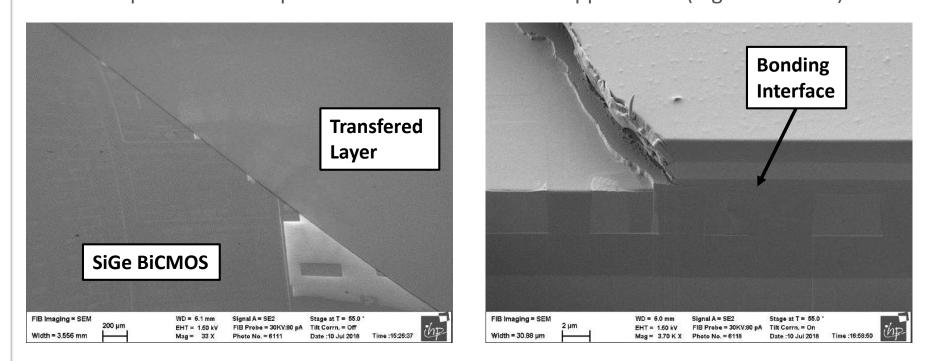

## Layer Transfer Technology

Layer transfer technology based on SiO<sub>2</sub>-SiO<sub>2</sub> fusion bonding + backgrinding

Development of basic process module for different applications (e.g. bolometer)

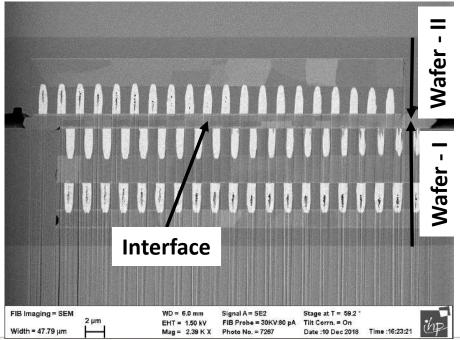

## **Al-Al Bonding Results - I**

- Interconnections between wafers with very low ohmic contacts (specific contact resistance ~1.3e-7 Ohm\*cm<sup>2</sup>)

- Initial process evaluation with yield ~85%

www.ihp-microelectronics.com | © 2019 - All rights reserved | Mehmet Kaynak

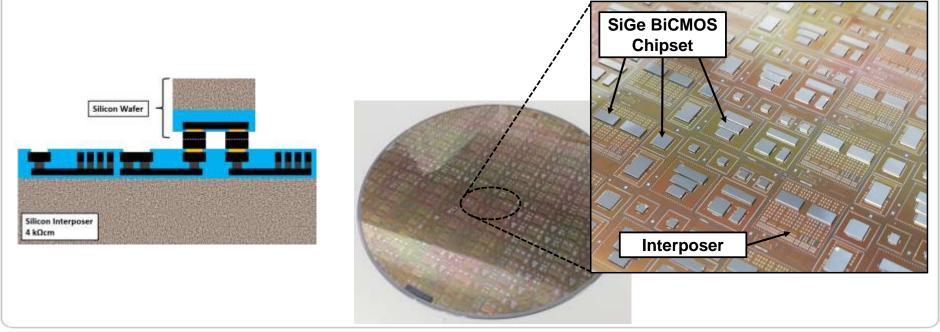

## **Wafer-Level Packaging Platform**

- Fan-out wafer level packaging platform based on Al-Al bonding

- Fan-out wafer-level packaging & Heterogeneous integration

- General proof of concept already done during Al-Al wafer bonding evaluation

www.ihp-microelectronics.com | © 2019 - All rights reserved | Mehmet Kaynak

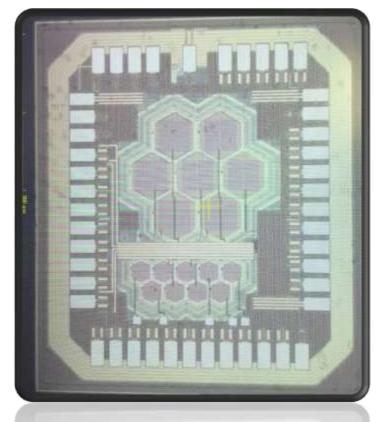

# **Cooperation Example**

A 3-year project started in march 2016 financed by the Swiss National Fund to produce a PET Scanner for small animals **based on silicon detector technology,** insertable in an MRI machine and with **30ps RMS time resolution**.

Sensor ASIC design. Scanner assembly. Image reconstruction.

Read Out design and production. Flex design and production.

Image reconstruction. Scanner test.

### Participating institutes:

- University of Geneva

- University of Bern

- Hôpitaux Universitaires Genève

### In collaboration with:

- IHP microelectronics, INFN of Roma Tor Vergata, CERN Ideasquare

- Milestone 1: A monolithic pixel detector with 100 ps time resolution for MIPs and large pixel size to be used for TOF-PET applications.

- Milestone 2: A monolithic pixel detector with sub-100 ps time resolution for MIPs and fine pixel size to be used for high-energy and applied physics research.

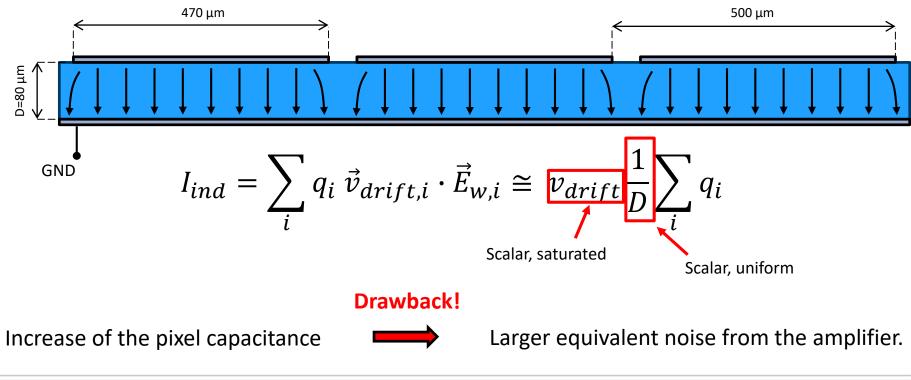

The condition of "parallel plate" read out is fundamental to guarantee the uniformity of the weighting and the electric field.

**Read out geometry**

www.ihp-microelectronics.com | © 2019 - All rights reserved | Mehmet Kaynak

March 05, 2019

$$ENC^{2} \propto \left(2q_{e}I_{C} + \frac{4kT}{R_{P}} + i_{na}^{2}\right) \cdot \tau + \left(4kTR_{S} + e_{na}^{2}\right) \cdot \frac{C_{in}^{2}}{\tau} + 4A_{f}C_{in}^{2}$$

Fast integrator

Dominating term: series noise ( $\tau < 10 \text{ ns}$ )

Low input impedance of the transistor

**BJT technology**

Maximize the current gain (at high frequencies!) while keeping a low base resistance

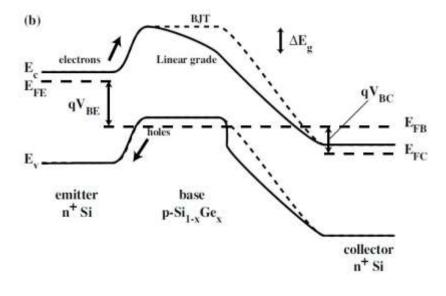

## SiGe technology for low noise, fast amplifiers

A possible approach: changing the charge transport mechanisms in the base from diffusion to drift.

Introducing a drift in the base.

SiGe heterojunction bipolar transistor technology.

Our technology choice:

**SG13S from IHP microelectronics**  $\beta = 900$  $f_t = 250 \ GHz$

## **Target ASIC specifications**

| ASIC length                           | 24 mm                      |

|---------------------------------------|----------------------------|

| ASIC width                            | 7, 9, 11 mm                |

| Pixel Size                            | $500 \times 500 \ \mu m^2$ |

| Pixel Capacitance (comprised routing) | 750 <i>fF</i>              |

| Preamplifier power consumption        | $< 0.8 \ mW/mm^{2}$        |

| Preamplifier E.N.C.                   | 600 e <sup>-</sup> RMS     |

| Preamplifier Rise time (10% - 90%)    | 800 ps                     |

| Time resolution for MIPs              | 100 ps RMS                 |

| TDC time binning                      | 20 <i>ps</i>               |

| TDC power consumption                 | < 1  mW/ch                 |

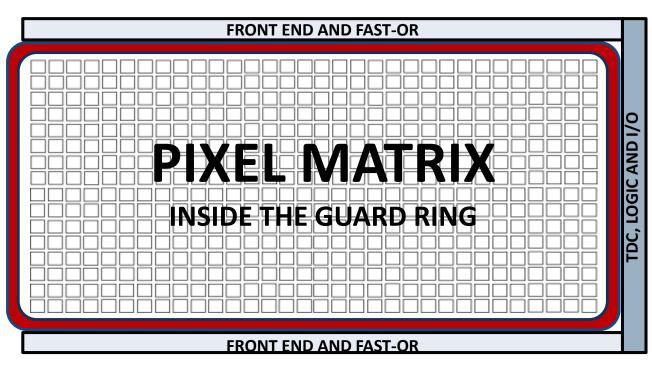

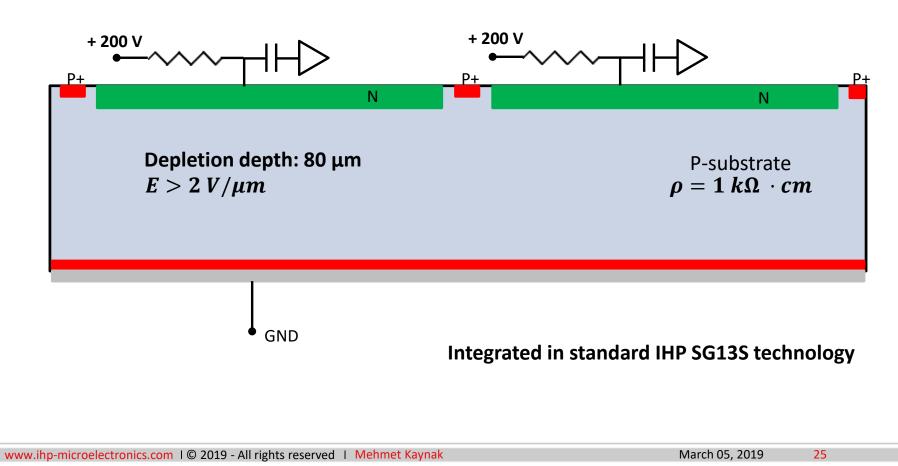

## Sensor design

### Simplified architecture for **large pixel size**.

- SG13S technology from IHP Microelectronics.

- N-on-P pixels.

- Substrate to ground.

- Positive high voltage to pixels.

- Signal routed to the frontend on the chip periphery.

## Sensor design

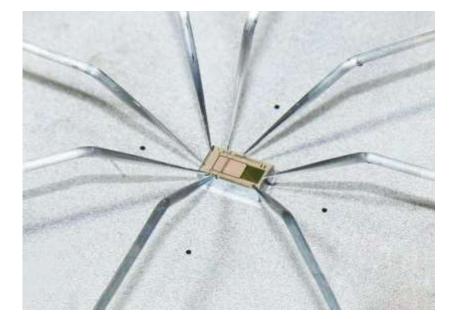

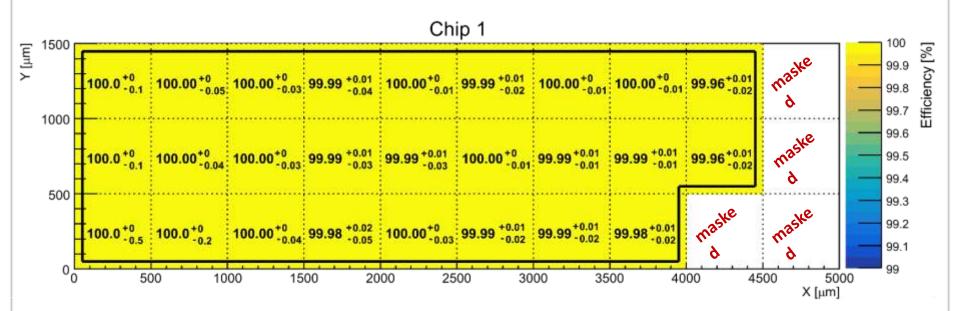

## **Concept prototype**

### December 2017

Monolithic chip: sensor + front-end.

- High wafer resistivity (1  $k\Omega cm$ ).

- Breakdown voltage: above 160 V.

- Pixel size: 900  $\times$  900  $\mu m^2$  and 900  $\times$  450  $\mu m^2$ .

- No thinning, no backplane metallization.

Beam Test with MIPs:

- Time resolution: 200 ps.

- Efficiency 99.8%.

- Power consumption: 0.8 mW/mm<sup>2</sup>.

For more information: L. Paolozzi *et al* 2018 *JINST* **13** P04015 doi: <u>https://doi.org/10.1088/1748-0221/13/04/P04015</u>

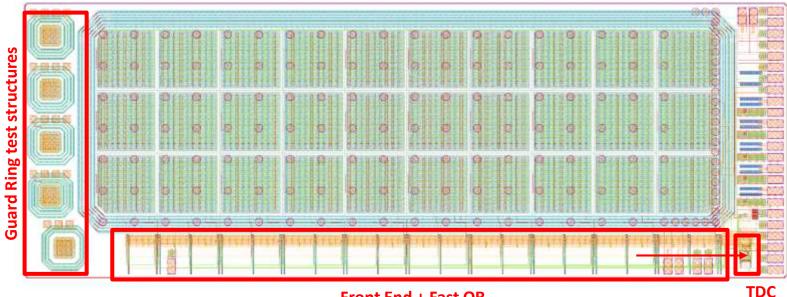

## **Demonstrator layout**

### Front End + Fast OR

- 3 × 10 matrix, 500 × 500  $\mu m^2$  pixels.

- Preamplifier, discriminator, 50 ps binning TDC, logic, serializer integrated in chip.

- Thinned to 100  $\mu m.$  Depletion depth 80  $\mu m.$

- Full backside processing.

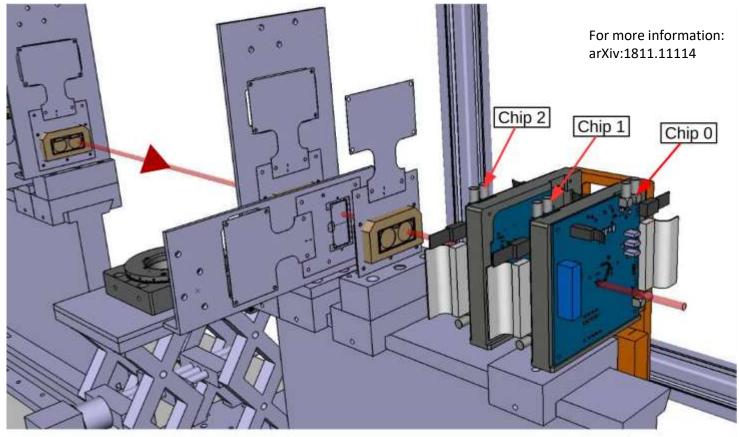

# Beam test with MIPs at CERN SPS OF DE GENÈVE

.....

## Target: sub-100ps resolution

Test prototype – IHP SG13G2 technology:

- Insulated HBT designed with IHP microelectronics and characterized in foundry.

- High voltage: breakdown at -200 V.

- Electronics fully functional.

- Data taking in progress.

# JICG CMOS and JIC LDMOS – A Radiation Hardening by Design ASIC Approach for Applications in Extreme Environments

# Outline

- Introduction

- Goals

- JICG CMOS

- TID Reduction

- SEU Reduction

- TID and SEUTest

- Performance Test

- 250 nm JIC LDMOS

- 130 nm JICG CMOS

- Summary and Conclusions

# Introduction

- Commercial processor circuits today fabricated in 14-nm technologies

- CMOS technologies for radiation-hard applications are always several generations behind most advanced CMOS technologies

- Advanced SOI FinFET technologies being discussed as most promising candidates for radiation hardness in terms of SEU and TID

- Very small amount of collected charge after a particle impact improves SEU hardness ,small backside TID effects, high speed, low power, but in aero space applications and high energy physics experiments (HEP) only small volume of devices is required → not affordable for civil applications

- In HEP experiments 250nm bulk CMOS technologies replaced by 130 nm CMOS, 65 nm technologies are currently under evaluation (TID issues !?)

- 130 nm bulk CMOS stays further in the game, mature, robust, low cost

- Improve the radiation tolerance of CMOS transistors in IHP's 250nm and 130nm SiGeC BiCMOS technologies to meet requirements in HEP experiments as a worst case scenario

- Find a radiation hardening by design (RHBD) approach taking into account both total ionizing dose (TID) effects <u>and</u> single event upsets (SEU)

- Evaluation of JICG CMOS and JIC LDMOS test circuits in IHP's 250 nm SiGeC BiCMOS technology

- Verification of TID and SEU radiation hardness

- Evaluation of device performance

- Transfer of results into 130nm technology

- Evaluation of extra effort for forming of S/D extension and halo implants and slicide blocked areas

# **JICG CMOS**

- Suppress TID induced source drain leakage by junction isolated (JI) of source drain regions, form silicide blocked well regions

- Avoid SEU induced malfunctions of digital cells suppressed by a redundancy on transistor level, each MOS transistor is replaced by a stack of two locally separated single transistors which share a common gate (CG)

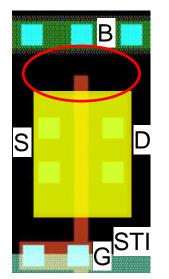

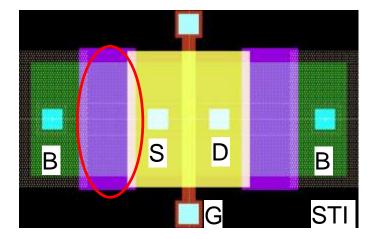

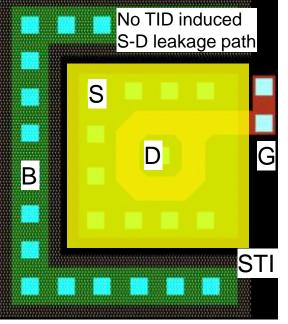

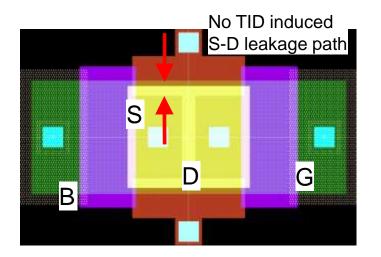

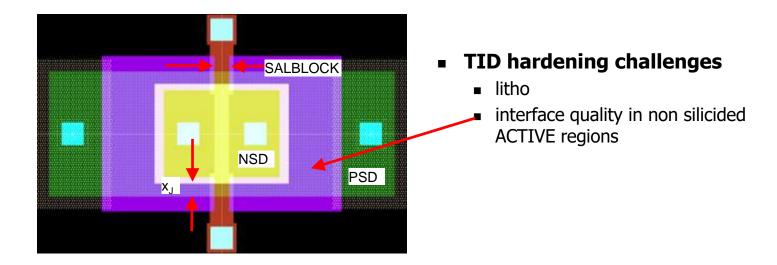

# **JICG CMOS - TID Reduction**

- Efficient draw off of majority excess charge carriers to the body contact

- Well sheet resistance near and in source region determines turn on behavior of parasitic bipolar transistor

Source/drain-body isolation from body via STI, well sheet resistance high

Source/drain-body isolation from body via silicide blocked region in ACTVE, well sheet resistance low

**TID:** Complete junction isolation of source/drain regions

R. Sorge, 5.Annual MT Meeting, Helmholtz Institute Jena, March 5th 2019

37

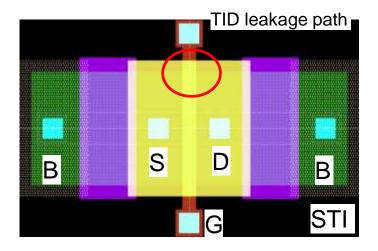

No TID leakage path

Additional lateral junction prevents TID related source drain leakage due to positive fixed charges generated in the STI region of the MOS inversion channel

TID related source drain leakage due to positive fixed charges generated in the STI region of the MOS inversion channel

#### duced

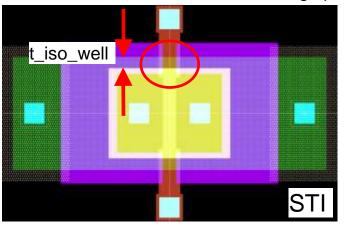

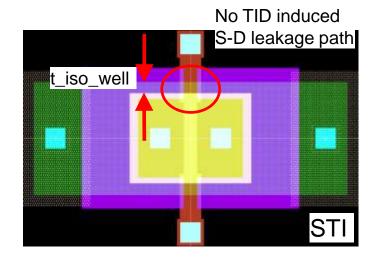

TID: JI MOS transistor vs enclosed layout transistor (ELT)

Commonly used ELT to suppress TID related source drain leakage JI MOS as a symmetrical device enabling a minimum gate width. But also with additional gate body capacitance.

t\_iso\_well

## JICG CMOS - TID Reduction

ST

No TID induced

S-D leakage path

#### **JICG CMOS - TID Reduction**

TID: JI MOS transistor vs MOS transistor with dog bone gate

Dog bone gate MOS transistor with a large additional gate body capacitance drastically reduces CMOS switching speed.

JI MOS transistor also with additional gate body capacitance. Challenge for SALBLOCK litho !

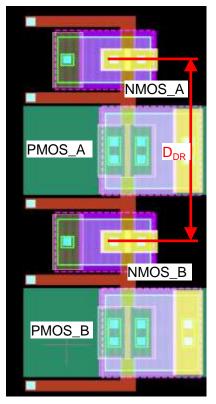

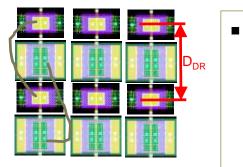

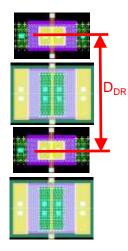

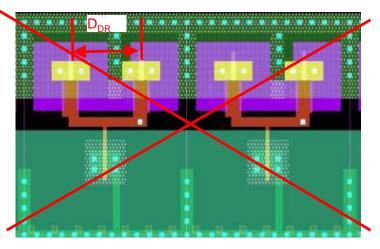

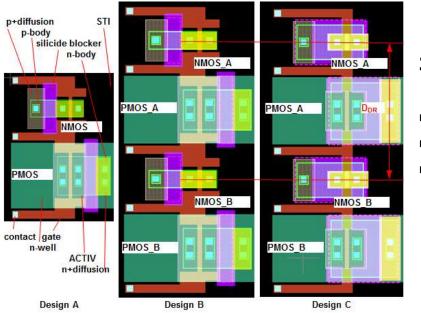

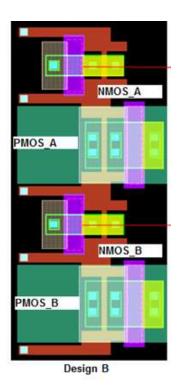

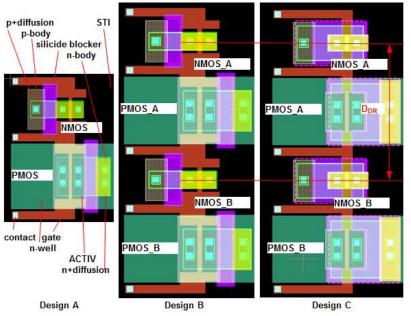

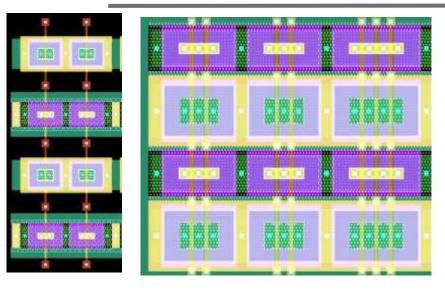

#### **JICG CMOS - SEE Reduction**

#### SEU: Avoiding SEUs by redundancy on transistor level

- Stack of two locally separated MOS transistors A and B which share a common gate maintain the blocking capability of any NMOS and PMOS branch in a CMOS circuit after an impact of a high energetic particle

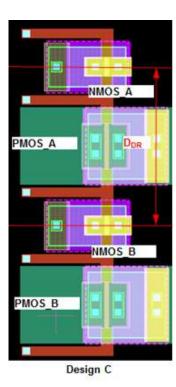

- Critical design value in the layout is the geometrical distance of the drain regions of the two MOS transistors D<sub>DR</sub>,

- D<sub>DR</sub> must be great enough so that the generated electron hole pairs along the impact trajectory in one transistor does not affect the blocking capability of the second transistor

- Alternating arrangement of NMOS\_A/PMOS\_A/NMOS\_B/PMOS\_B in vertical direction gives a sufficiently great distance D<sub>DR</sub> between the stacked transistor pairs.

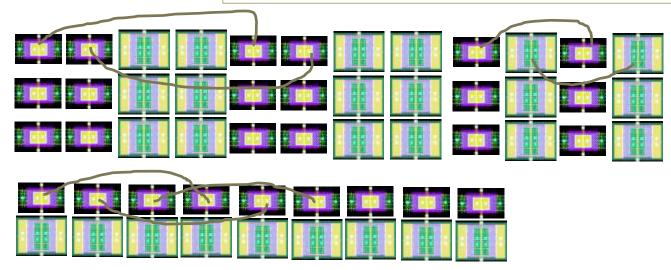

#### **JICG CMOS - SEE Reduction**

- SEU hardening challenges at arrangement of MOS transistor pairs with common gates

- Requirements for the layout :

Minimum area consumption for arrangement of transistors and their wiring

Ensure sufficient minimum distance  $d_{DR}$

#### **JICG CMOS - SEE Reduction**

No events detected for LET> 120 MeV cm2/mg

Events detected @ LET< 62 MeV cm2/mg

Ensure sufficient minimum distance of source drain regions D<sub>DR</sub>

#### **JICG CMOS -TID Reduction**

- Challenging overlay and CD requirements for NSD, PSD and SAL masks

- For 0.13µm and below, special effort for halo and LDD mask sequence

- TID hardening approach via silicide blocker mask verified in IHP's 0.13µm SG13S technology, feasible up to 65 nm technology node

- But there are new radiation damage issues in 65 nm technologies with trapped charges in spacers which cause depletion of LDD regions ...

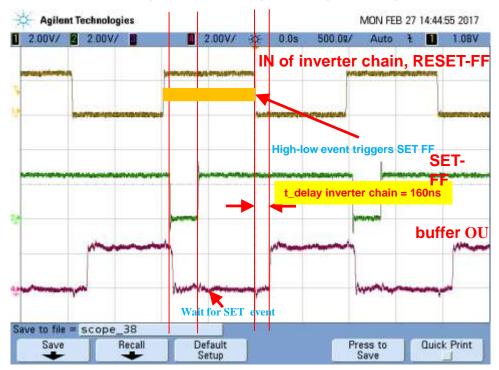

# Long inverter chain with 720 single inverters as simple test device for TID, SEU and performance tests

NMOS transistor gate width 1 μm, PMOS gate width 2.3 μm

#### TID testing

■ devices were irradiated using a Co-60 source for all inverters  $V_{DD} = 2.5V$  was applied, inverter chain input was set to  $0V \rightarrow$  the gates of one half of all inverters are biased with 0 V, where the gates of the other half are biased with  $V_{DD}=2.5V$  (gives maximum of trapped positive charge at STI/silicon interface).

# Long inverter chain with 720 single inverters as simple test device for TID, SEU and performance tests

NMOS transistor gate width 1 μm, PMOS gate width 2.3 μm

#### SEU testing

- last stage of inverter chain is connected to the RESET input of a RS latch

- output of the RS latch drives an output buffer to drive a 50 Ohm output impedance

- RS latch catches any propagated SET event during the irradiation with high energetic particles

- Convenient counting of events in separated counter

- Once one event is detected the test setup sets again the RS latch, so the setup is ready for counting the next propagated SET event

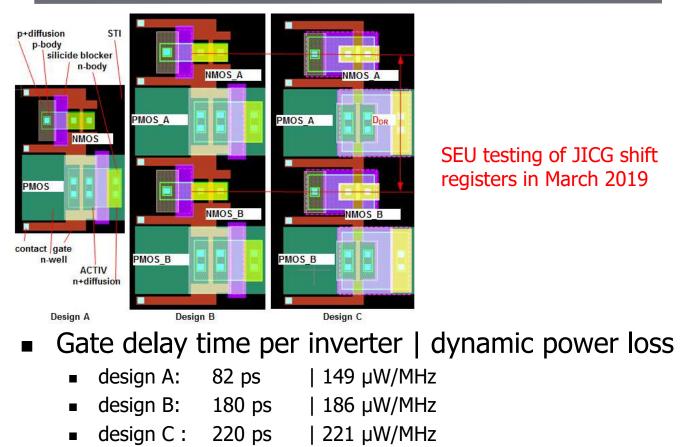

#### **JICG CMOS– Switching Performance**

#### Switching performance test

Determination of gate RC delay and dynamic power loss

#### **JICG CMOS - Designs**

- TID induced S/D leakage

- Propagated SEU events

- Switching performance

Design A:standard CMOS inverter without improved radiation hardness

**Design B**:standard CMOS inverter with improved SEU radiation hardness by redundancy on transistor level.

**Design C**: improved TID and SEU radiation hardness by junction isolated NMOS and PMOS transistors and redundancy on transistor level.

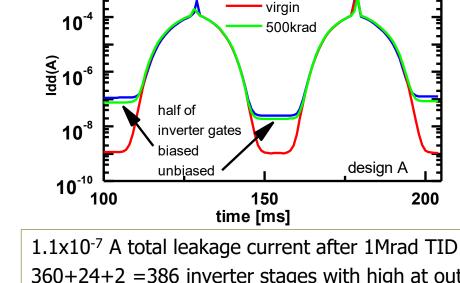

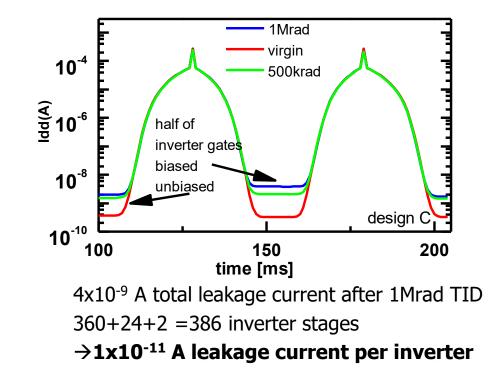

## **JICG CMOS - TID Test**

- Standard CMOS Inverter as reference

- Different bias for each half of inverters

Design A

360+24+2 = 386 inverter stages with high at output  $\rightarrow$  **2.8x10-10 A leakage current per inverter**

1Mrad

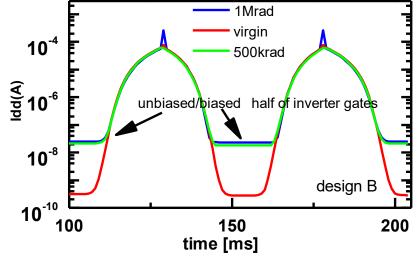

### **JICG CMOS - TID Test**

Inverter with SEU protection elements only

2.5x10<sup>-8</sup> A total leakage current after 1Mrad TID

360+24+2 = 386 inverter stages with high at output  $\rightarrow$  **6.5x10**<sup>-11</sup> **A leakage current per inverter**

#### **JICG CMOS - TID Test**

Inverter with TID and SEU protection construction elements

## 6p

## **JICG CMOS - SEU Test**

- SEU tests with high energy heavy ions 124Xe35+ ions (E=995MeV)

- three tilt angles 0°, 45° and 60° corresponding to LET values of 62.5, 88.3 and 125 MeV cm<sup>2</sup> mg<sup>-1</sup>

- particle fluence 6.4 10<sup>6</sup> cm-2.

- Standard inverter design A,

- 13 events at LET=62.6 MeV cm2 mg-1

- 40 events at LET=88.3 MeV cm2 mg-1

- 65 events at LET=125 MeV cm2 mg-1

- Designs B and C

- no events at all up to the maximum available LET value of 125 MeV cm<sup>2</sup> mg<sup>-1</sup>

- no SEL events for all designs A,B and C

## 6p

#### **JICG CMOS Performance**

#### **JIC LDMOS**

Supression of TID induced leakage

- Additional lateral junction prevents TID related source drain leakage due to positive fixed charges generated in the STI region of the MOS inversion channel

- Cascode arrangement (MOS/NLDMOS or IMOS/NLDMOS) effectively increases SEB onset volatage from 14 V to 4 V

- Common gate arrangement shows significant decrease of RF performance in terms of f<sub>t</sub> and f<sub>max</sub>

Supression of TID induced leakage and SEB

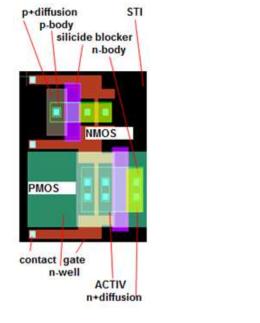

#### 130 nm JICG CMOS

- 130 nm JICG Inverter chain SEU test shows no events for LET > 120 MeV cm2/mg

- 130 nm JICG Shift register for SEU testing currently in preparation

Supression of TID induced leakage and SEU

- Redundancy on transistor level, stack of two locally separated MOS transistors which share a common gate maintain the blocking capability of any NMOS and PMOS branch in a CMOS circuit after an impact of a high energetic particle

- Alternating arrangement of isolated NMOS and PMOS transistors in vertical direction gives a sufficiently great distance between the stacked transistor pairs

- Each transistor with dedicated guard ring

- Highly effective conduction of well currents to body contacts inhibits turn on of parasitic bipolar transistors

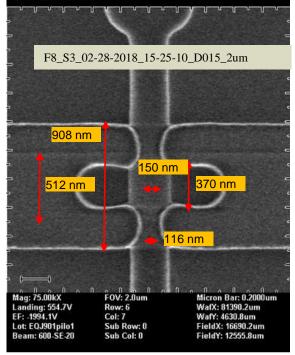

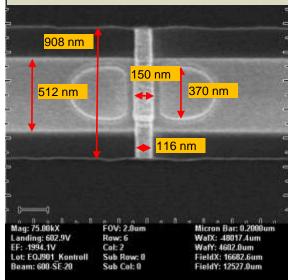

#### 130nm JICG CMOS – SAL

#### T380, EQJ901 SAL mask wo Si3N4 source drain spacer

#### Recipe: TECHNOLOGIE013\T380\SAL\SAL\_D015.ADI Site: I\_SAL\_D015\_ADI

#### T380, EQJ901 NPH mask wo Si3N4 source drain spacer

Recipe: TECHNOLOGIE013/T380/NPH/NPH\_V2\_UV1100\_ADI Site: IM\_NPH\_REAL\_UV1100\_ADI

\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_

#### F8\_S3\_02-28-2018\_15-25-10\_D015\_2um

## **Summary & Conclusions**

- A novel RHBD design approach suitable for applications in harsh radiation environment based on bulk CMOS technologies has been verified in 250 nm technology node

- JICG CMOS inverter test circuits fabricated in a 0.25µm SiGeC BiCMOS technology show excellent radiation hardness in terms of TID and SEU

- The new bulk CMOS RHBD approach is capable to significantly suppress TID and SEU induced malfunctions for <u>combinational</u> and sequential digital circuits

- In comparison with standard CMOS inverters JICG CMOS inverters require a doubled chip area and show a decrease of switching speed by a factor of 0.37 and an increase of dynamic power loss by a factor of 1.48

- Extra litho effort for TID hardness in 130 nm CMOS technology

- SG13RE technology module of SG13S technology will include JICG CMOS and JIC LDMOS devices

- JICG SRAM in preparation

## Thank you for your attention!

Mehmet Kaynak & Roland Sorge

IHP – Innovations for High Performance Microelectronics Im Technologiepark 25 15236 Frankfurt (Oder) Germany Phone: +49 (0) 335 5625 707 Fax: +49 (0) 335 5625 327 Email: kaynak@ihp-microelectronics.com

www.ihp-microelectronics.com 🔳 🗩 🖻

innovations for high performance microelectronics