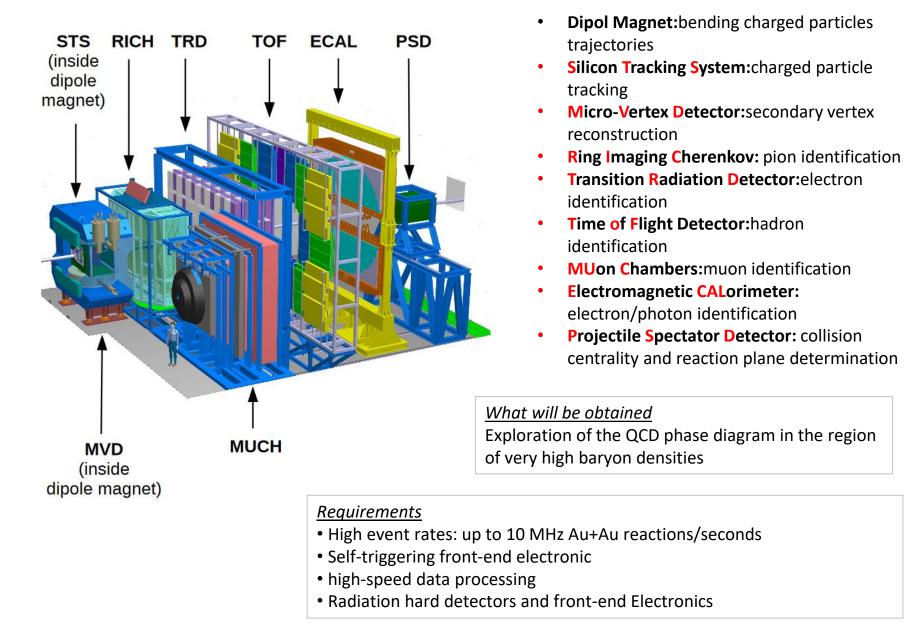

# Quality Assurance Tests of The STS Read-out Electronics for The CBM Experiment

Merve Dogan, Adrian Rodrigues Rodriguez, Christian J. Schmidt 5th Matter and Technology Meeting, Jena 2019

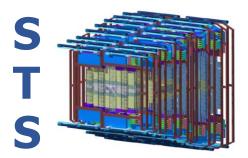

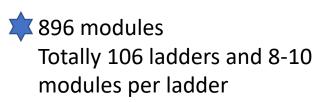

# Silicon Tracking System

♦8 tracking station between the angle 2.5° ≤ Θ ≤ 25°

♦Self-triggering electronics

♦double-sided silicon microstrip sensors

♦hit spatial resolution ≈ 25 µm

♦Δp/p ≈ 1.8%

♦Inside 1 Tm dipole magnet

♦hit reconstruction eciency > 98%

# **Read-Out Electronics**

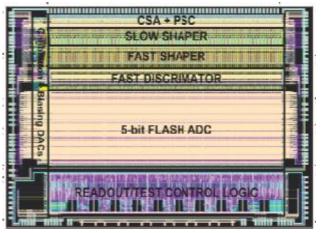

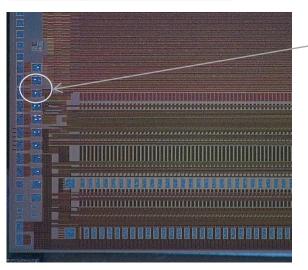

#### STS-XYTERv2.0 (STS X,Y coordinate + Time and Energy Resolution)

- 128 channels+2 test channels

- Chip size: approximately 10 mm x 6.7 mm

- Radiation-hardened design

- Energy and time measurement

- Time resolution < 5ns</li>

- 5 bit flash ADC/channel dynamic range: 14fC

- Digital back-end compatible with the CERN-GBTx data concentrator

#### MOTIVATION:

Test and QA of STS-XYTER v2 and prototype FEBB for module production and FEB assembly

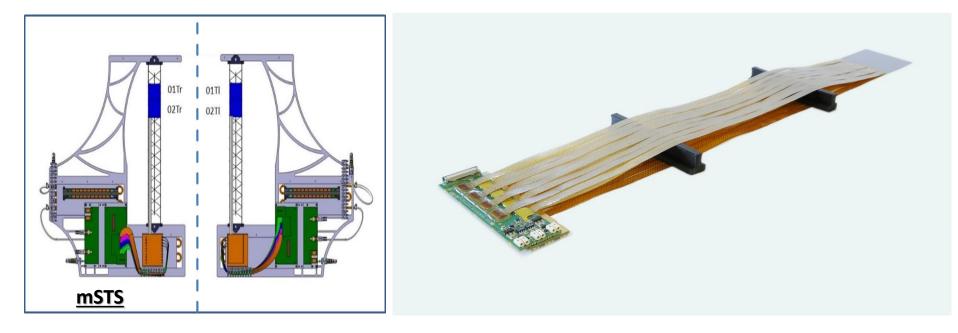

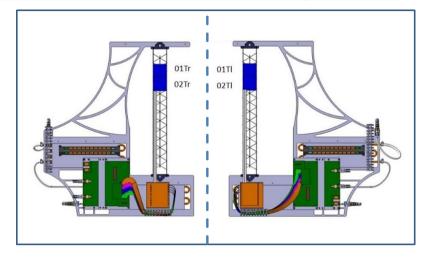

# FAIR Phase 0: mCBM and mSTS

- mCBM: A CBM full system test-setup for high-rate nucleus-nucleus collisions at GSI/FAIR

- mSTS: demonstrator of STS intergration and operation aspects

- Two mechanical half-units for the first of total two mSTS tracking stations

- It will allow to test the detector and electronics components developed for the CBM experiment

- Module installation has finished

- First run was on December 2018, upcoming run in 2019

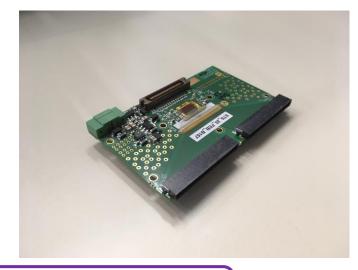

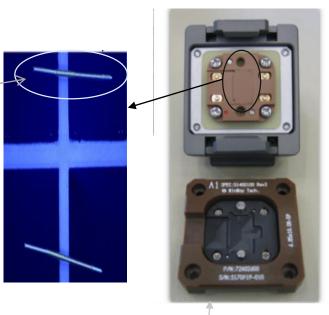

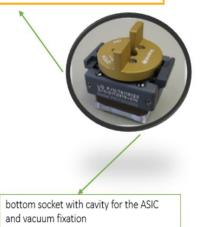

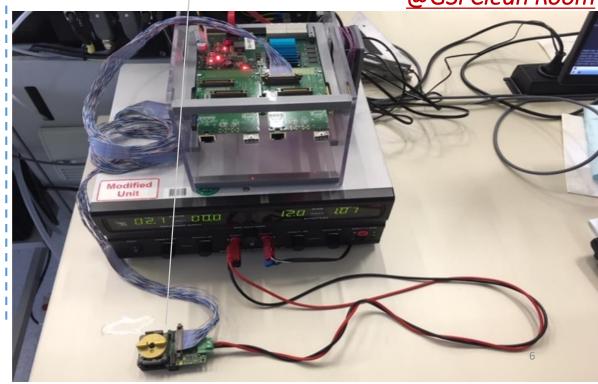

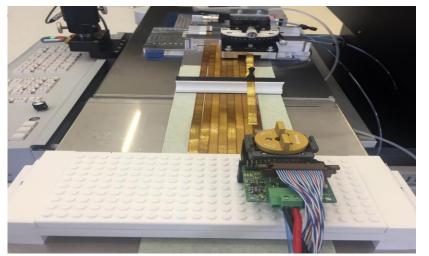

#### Test System@GSI

Top socket with latches and knob

#### Hardware:

- Pogo pin station designed at GSI with close collaboration from Cracow team.

- The pogo- socket has 53 pogo needles, each one has a diameter of ~100 μm.

- Pogo station

- AFCK board with STS-XYTER tester

firmware.

- gDPB\_FMC interface card.

software basen on python

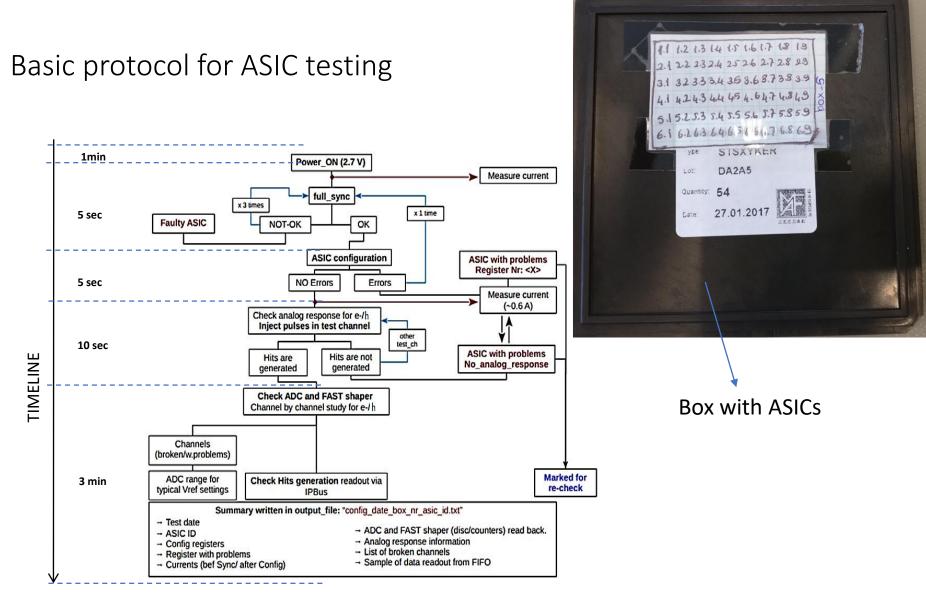

#### Which values are tested?

Current values, reference voltages values, analog responses, the dynamic range for the electrons and holes before calibration

### @GSI Clean Room

-In the version 2.1, possible to fuse a uniq ID in the chip at the pogo-pin test level

-this information can be requisted later on as a way to track the full test of the chip from basic tests until the final system

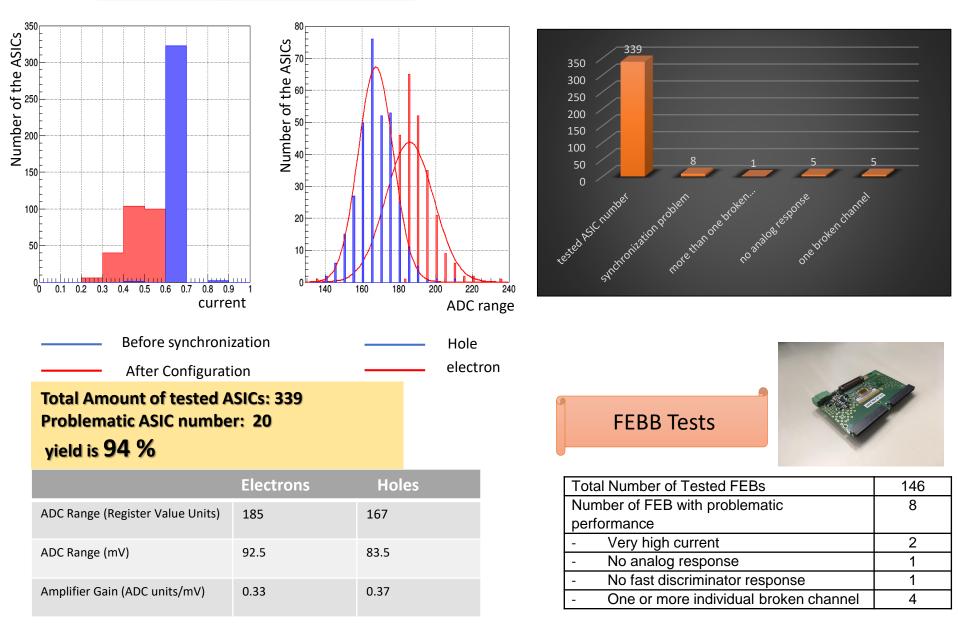

#### ASIC acceptance results

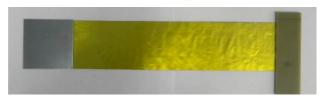

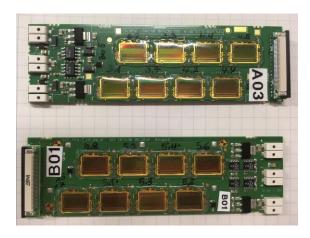

## **Functional tests during assembly**

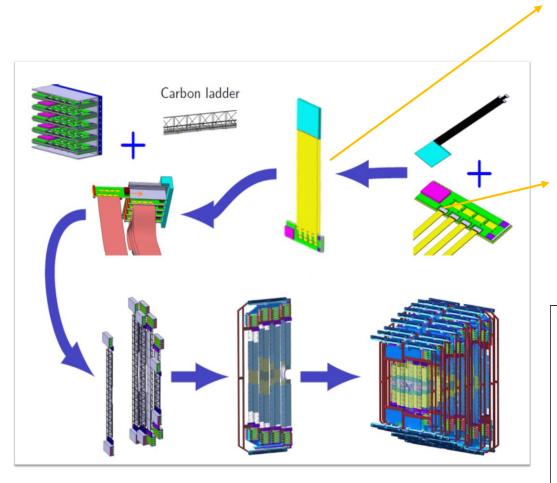

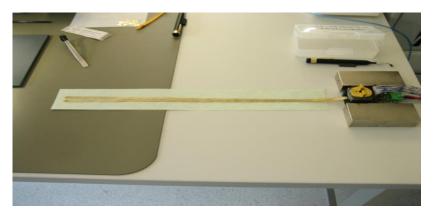

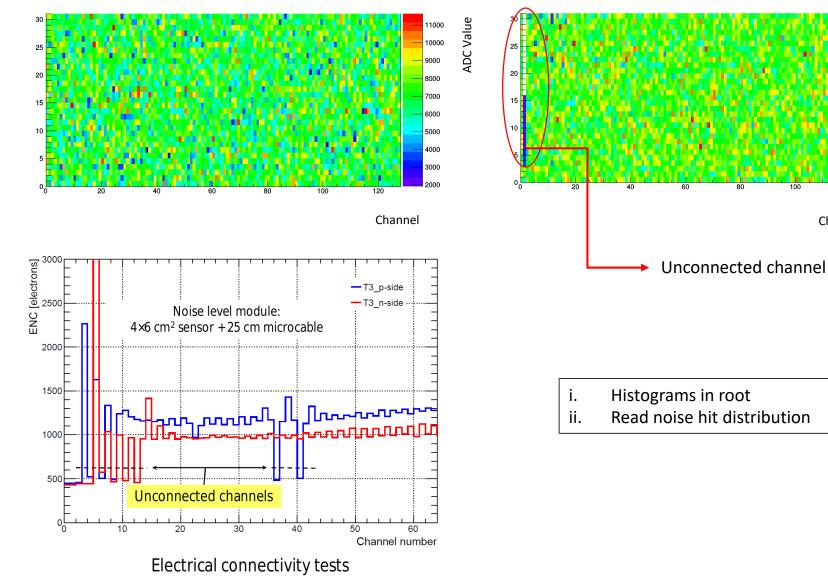

### TEST 2: ASIC+Microcable

- The goal is to check electrical connectivity between microcable and ASIC (tab-bonding quality)

- Measure the noise level and see the connection of channels

- Possible to re-bond the microcable again on ASIC side

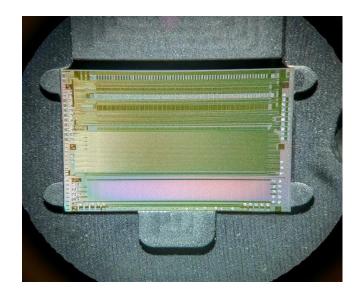

#### TEST 3: ASIC+Microcable+Sensor

- The goal is to check electrical connectivity between microcable, Sensor and ASIC (tab-bonding quality)

- Measure the noise level and see the connection of channels

- Possible to re-bond the microcable again on the sensor side

#### Channel hit maps reveal unconnected channels

Channel

### mCBM Module Assembly Status

| ASSEMBLY STAGE | Number of tested<br>Asıcs      | SETUP<br>REQUIREMENT | TEST PURPOSE                    | TIME/per<br>ASIC | Number of Bad<br>ASICs | Unconnected<br>Channels |

|----------------|--------------------------------|----------------------|---------------------------------|------------------|------------------------|-------------------------|

| ASIC test      | 98                             | Pogo pin station     | Fully calibration & test        | 12 min           | 10                     |                         |

| Module 01T-r   | 16                             | Pogo pin station     | Check electrical<br>connections | 5 min            |                        | 3                       |

| Module 01T-l   | 8 (p-side)                     | Pogo pin station     | Check electrical connections    | 5 min            |                        | -                       |

| Module 02T-r   | 16 (only test with microcable) | Pogo pin station     | Check electrical connections    | 5 min            |                        | 2                       |

| Module 02T-l   | 16                             | Pogo pin station     | Check electrical connections    | 5 min            |                        | -                       |

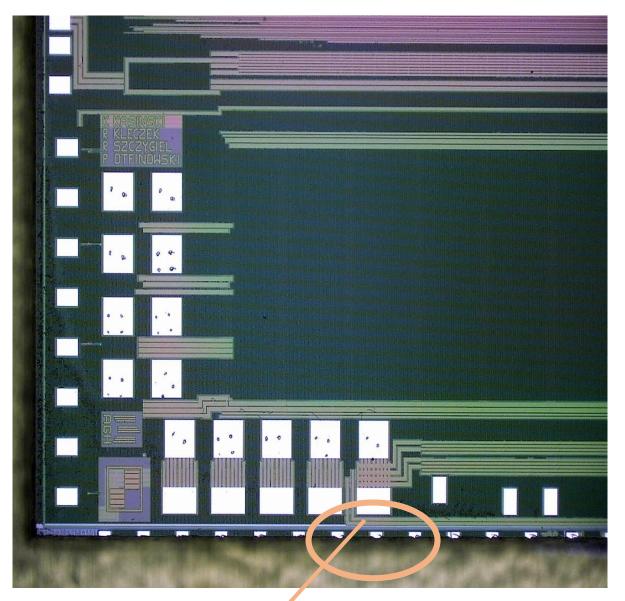

#### STS-XYTER2.0—critical design detail

ASICs showed different behaviours during the module test after assembly

forthcoming module productions will be done with one ASIC test stage only.

#### Critical lines for wire bonding

Many thanks to my colleagues...