# TERASCALE WORKSHOP 2019 SERIAL POWERING IN PIXEL DETECTORS

Matthias Hamer, University of Bonn

- why serial powering?

- key ingredients for a serially powered silicon pixel detector

- challenges in serial powering

- why serial powering?

- of the ATLAS Pixel Detector as an mole - most of what will be shown applies to the CNIS upgrade in a very - key ingredients for a serially powered silicon pixel detector

- challenges in serial powering

Il mostly use the planned upgrade

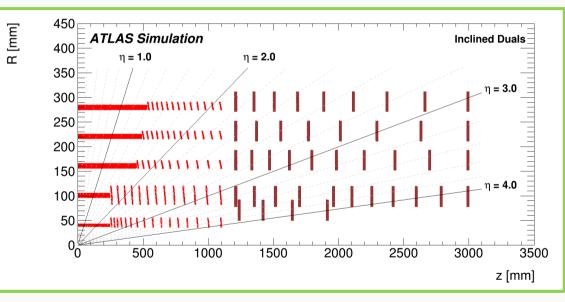

## ATLAS INNER TRACKER PIXEL DETECTOR

#### - 5 barrel layers:

- flat section up to z = 500mm

- inclined section up to z = 1200mm

- endcap rings up to z = 3000mmm

- coverage of tracks with  $|\eta| < 4$

- about 10.000 hybrid pixel modules

- ightarrow about 40.000 FE chips

- 50x50  $\mu m^2$  or 25x100  $\mu m^2$  pixels

- 2 innermost layers will be replaceable after collecting 2000 fb<sup>-1</sup>

#### Candidate Layout for the ATLAS Pixel Upgrade

- general reference: CERN-LHCC-2017-21; ATLAS-TDR-030

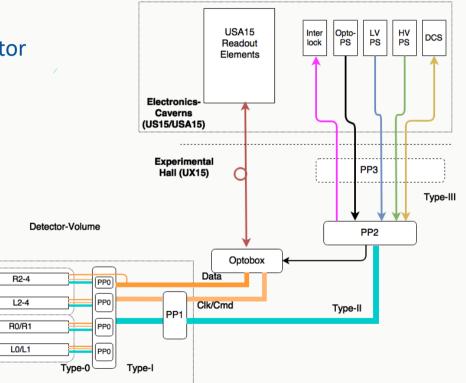

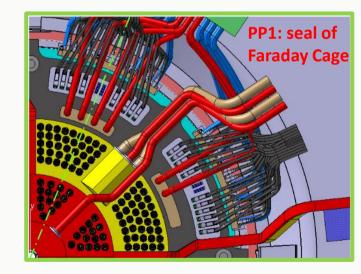

## SERVICES OVERVIEW

- services overview of the ATLAS ITk Pixel Detector

- off-detector services

- power supplies, readout electronics

- Type-3 cables, about 60m-80m long

- Type-2 cables, about 12m long

- on-detector services

- Type-1 cables, about 6m long

- Type-0 services, about 1m long

- → typical current path for a power line: about 200m

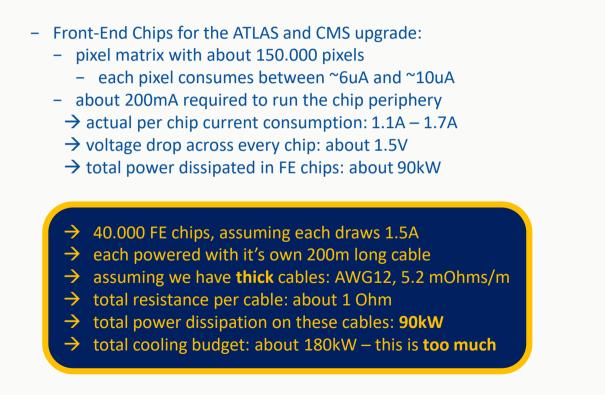

### PARALLEL POWERING?

### SERIAL POWERING

- recycle the current on-detector

- average serial powering modularity: 8 modules

- assuming single chip modules: losses on cables go down to 11kW

- the number of cable we require also goes down by a factor of 8

- $\rightarrow$  less material in the detector

- the number of required power supplies goes down by a factor of 8

- ightarrow less space required in services caverns

- advantages come at a cost

- actual current consumption per FE depends on instantaneous hit-rate

- $\rightarrow$  different instantaneous current consumption for all FE chips in a chain

- voltage drop from one module to the next

- ightarrow need AC coupled data transmission

- $\rightarrow$  with 3D modules: length of serial powering chain limited!

- ightarrow biasing of sensors can get a little tricky

- $\rightarrow \dots$

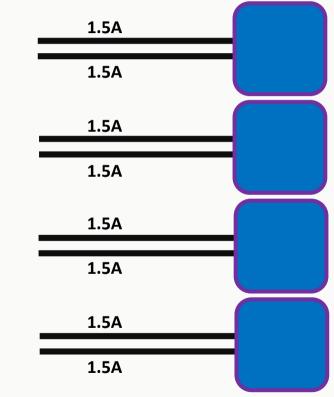

| 1.5A |  |

|------|--|

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

| 1.5A |  |

|      |  |

# HOW TO POWER A SERIAL POWERING CHAIN

- provide as much current to the full chain at all times as we expect at peak hit-rate

→ constant current source

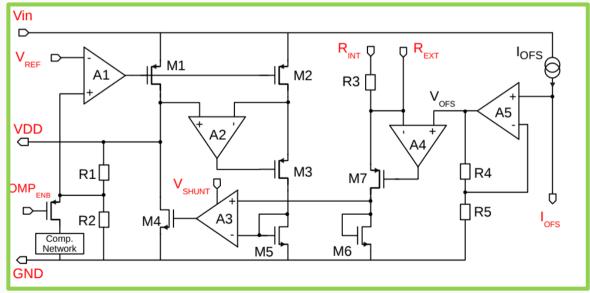

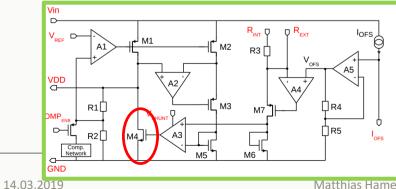

- each chip requires a local voltage regulator and a shunt to draw any surplus current

→ Shunt-LDO regulator

# HOW TO POWER A SERIAL POWERING CHAIN

- provide as much current to the full chain at all times as we expect at peak hit-rate

→ constant current source

- each chip requires a local voltage regulator and a shunt to draw any surplus current

→ Shunt-LDO regulator

from the outside, this looks like a voltage source (Voffset) connected in series to a resistor (R3/k)

$\rightarrow$  constant voltage drop at constant current independent of actual chip current consumption

# HOW TO POWER A SERIAL POWERING CHAIN

- provide as much current to the full chain at all times as we expect at peak hit-rate

→ constant current source

- each chip requires a local voltage regulator and a shunt to draw any surplus current

→ Shunt-LDO regulator

from the outside, this looks like a voltage source (Voffset) connected in series to a resistor (R3/k)

$\rightarrow$  constant voltage drop at constant current independent of actual chip current consumption

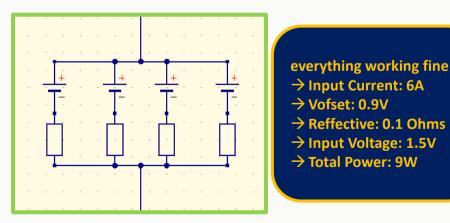

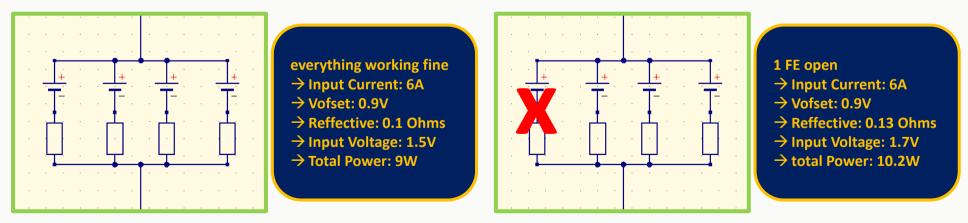

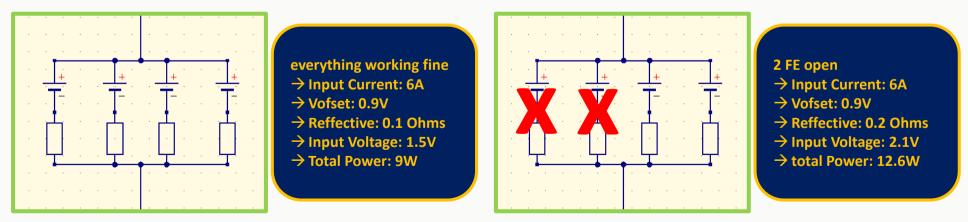

WHAT IF?

- a chip in the chain becomes high-ohmic?

- the rest of the chain would be disabled

- mitigate problem by connecting chips in parallel

- $\rightarrow$  SLDO regulators need to be able to shunt the extra current

- ightarrow total voltage drop over the module must not exceed limits for safe operation

- ightarrow thermal management of the module must be able to handle the extra power

WHAT IF?

- a chip in the chain becomes high-ohmic?

- the rest of the chain would be disabled

- mitigate problem by connecting chips in parallel

- $\rightarrow$  SLDO regulators need to be able to shunt the extra current

- $\rightarrow$  total voltage drop over the module must not exceed limits for safe operation

- ightarrow thermal management of the module must be able to handle the extra power

WHAT IF?

- a chip in the chain becomes high-ohmic?

- the rest of the chain would be disabled

- mitigate problem by connecting chips in parallel

- $\rightarrow$  SLDO regulators need to be able to shunt the extra current

- $\rightarrow$  total voltage drop over the module must not exceed limits for safe operation

- ightarrow thermal management of the module must be able to handle the extra power

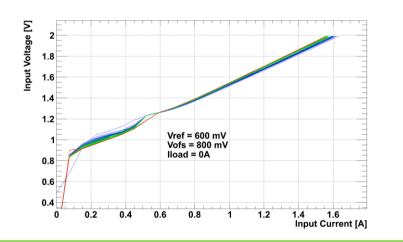

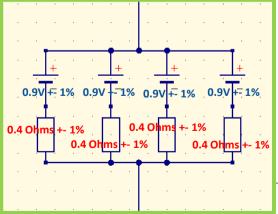

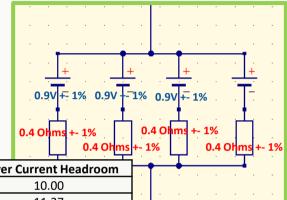

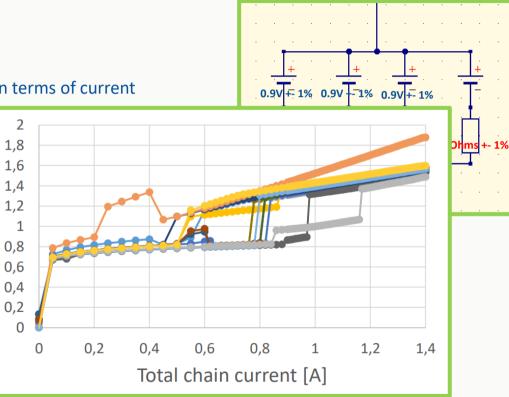

## OPERATING CHIP IN PARALLEL AGAIN...

- the FE chips on a module are operated in parallel:

- ightarrow single sensor tile, DC coupled: same ground potential required

- $\rightarrow$  current distribution becomes a challenge

- ightarrow voltage drop on all regulators is the same

- $\rightarrow$  offset voltage and slope determined by external resistors: small differences O(1%) expected

- ightarrow not every FE gets exactly 25% of the total current

- ightarrow hit-rate can spike significantly: increase load current in single regulators

- ightarrow compensate by supplying more current than nominally required: shunt current overhead

- $\rightarrow$  how much?

higher offset: lower current through resistor higher resistor: lower current through resistor

#### worst case:

→ downwards fluctuation for both offset and slope in all other chips (Chips 1, 2, 3)

→ upwards fluctuation for both offset and slope in one chip (Chip 4)

→ Chip 4 gets significantly smaller current

- worst case scenario for a quad chip module:

- 10% shunt current headroom supplied

- 1% variation in offset and slope: 5% difference in terms of current

- half of the safety we have

|        | Slope [Ohms] | Offset resistor [kOhms] | Offset [V] | Serial Current [A] | Voltage Drop [V] | <b>Required Current</b> | Leftover Current Headroom |  |

|--------|--------------|-------------------------|------------|--------------------|------------------|-------------------------|---------------------------|--|

| Module | 0.10         |                         | 0.90       | 6.00               | 1.49             | 5.45                    | 10.00                     |  |

| FE 1   | 0.39         | 445.50                  | 0.88       | 1.52               | 1.49             | 1.36                    | 11.37                     |  |

| FE 2   | 0.39         | 445.50                  | 0.88       | 1.52               | 1.49             | 1.36                    | 11.37                     |  |

| FE 3   | 0.39         | 445.50                  | 0.88       | 1.52               | 1.49             | 1.36                    | 11.37                     |  |

| FE 4   | 0.41         | 454.50                  | 0.92       | 1.44               | 1.49             | 1.36                    | 5.90                      |  |

| Target | 0.40         | 450.00                  |            | 0.05               |                  |                         |                           |  |

required current depends on hit-rate

- hit-rate can only be roughly estimated from simulation

- variations of up to 10% seen between simulation and measurement in current detector

1% variation in offset and slope in combination with a 10% variation in hit-rate leaves almost no headroom

### AN EXAMPLE

- worst case scenario for a quad chip module:

- 10% shunt current headroom supplied

- 1% variation in offset and slope: 5% difference in terms of current

- half of the safety we have

|        | Slope [Ohms] | Offset resistor [kOhms] | Offset [V] | Serial Currer |

|--------|--------------|-------------------------|------------|---------------|

| Module | 0.10         |                         | 0.90       | 6.00          |

| FE 1   | 0.40         | 445.50                  | 0.89       | 1.52          |

| FE 2   | 0.40         | 445.50                  | 0.89       | 1.52          |

| FE 3   | 0.40         | 445.50                  | 0.89       | 1.52          |

| FE 4   | 0.40         | 454.50                  | 0.91       | 1.44          |

| Target | 0.40         | 450.00                  |            | 0.05          |

required current depends on hit-rate

hit-rate can only be roughly estimated from sim

variations of up to 10% seen between simulatic

1% variation in offset and slope in combination

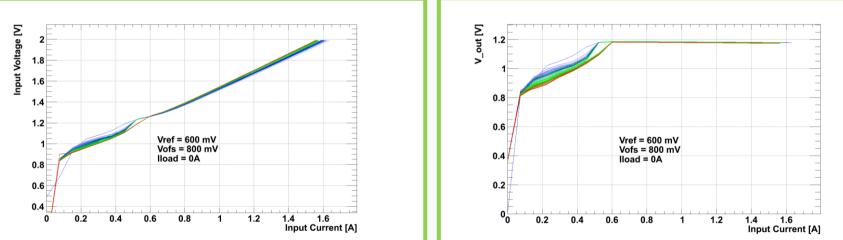

VIN [V]

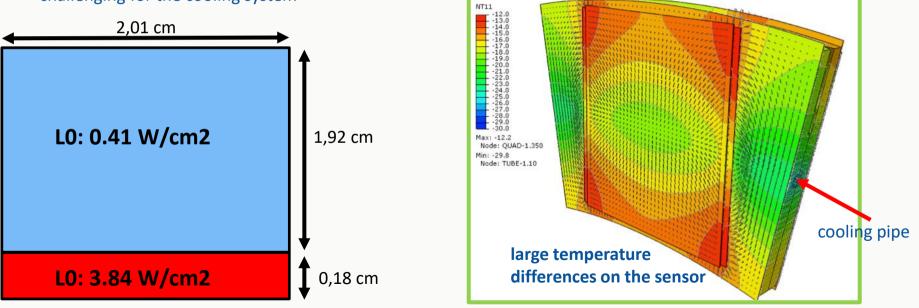

- significant fraction of total module power is dissipated on the chip periphery

- almost 40% of the total power dissipated in less than 10% of the chip area

- challenging for the cooling system

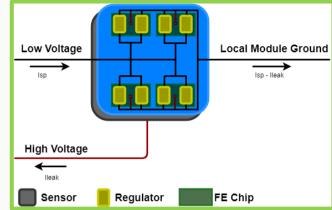

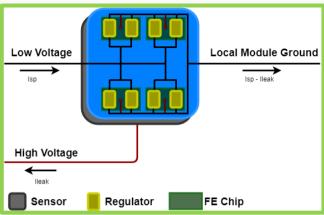

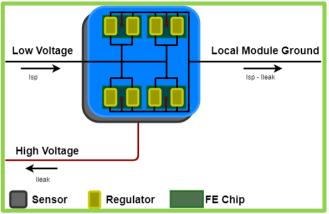

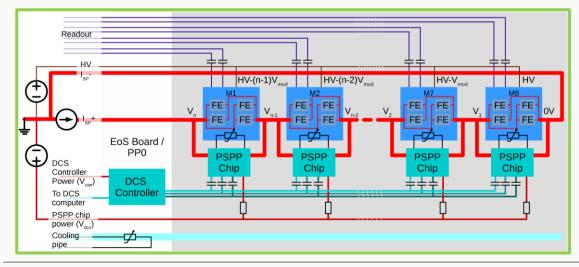

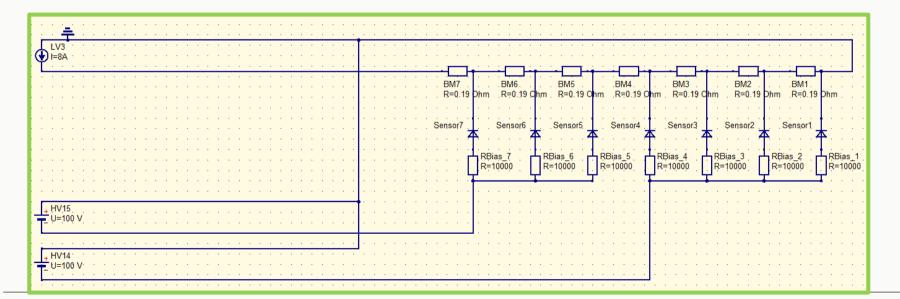

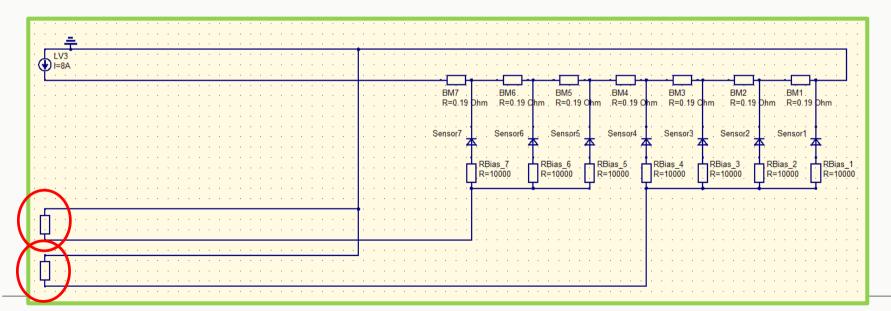

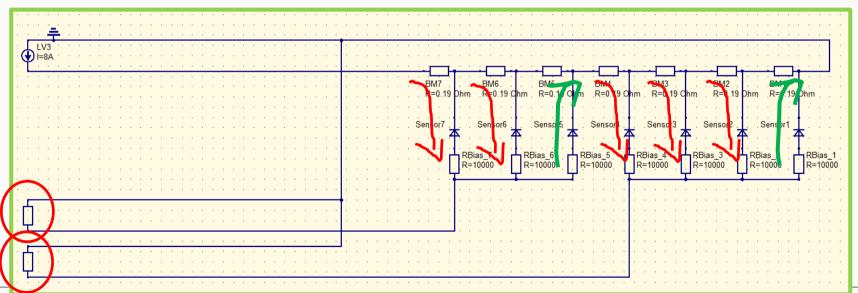

# HIGH VOLTAGE DISTRIBUTION ISSUES

- we can not put enough cables into the detector to provide an individual HV line for each sensor

- parallel distribution of sensor bias voltage to a subset or all modules in a serial powering chain

- HV referenced to local module ground different effective bias voltage on every single sensor

- long chains with 3D sensors not desirable

$\rightarrow$  depletion voltage as high as 10 V, breakdown voltage as low as 20V

- our grounding and shielding rules require us to tie the return lines of all power supplies to each other in the detector

- in combination with our current power supplies, this generates a potential problem

- HV power supplies act as high-ohmic resistors when switched off

- our grounding and shielding rules require us to tie the return lines of all power supplies to each other in the detector

- in combination with our current power supplies, this generates a potential problem

- HV power supplies act as high-ohmic resistors when switched off

- our grounding and shielding rules require us to tie the return lines of all power supplies to each other in the detector

- in combination with our current power supplies, this generates a potential problem

- HV power supplies act as high-ohmic resistors when switched off

- LV on  $\rightarrow$  small effective bias on each sensor  $\rightarrow$  return path through modules has lower resistance than HV PSU

# **OTHER SYSTEM ASPECTS**

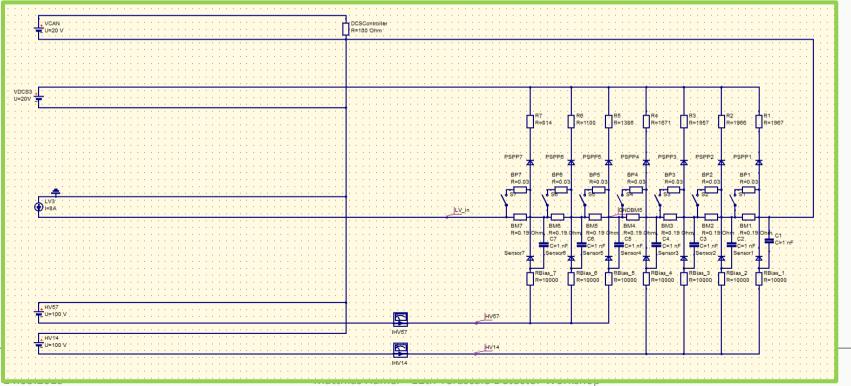

- a similar effect with the PSPP chips

- our current LV power supplies are shorted when switched off; VDCS generates a negative voltage drop on FE chips

22 22

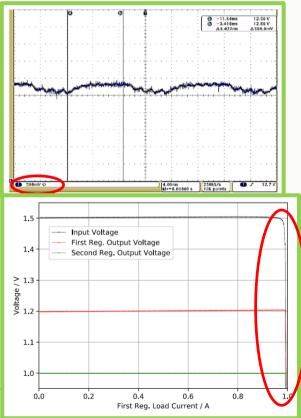

## SERIAL POWERING IN ACTION

- several prototypes have been built by now

- proof of principle at Bonn some time ago

- prototype with realistic services, power supplies, local supports at CERN

- long serial powering chain (13 modules) in Liverpool

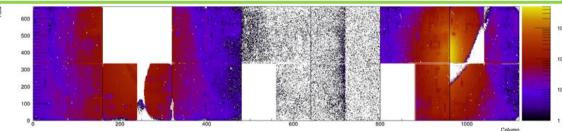

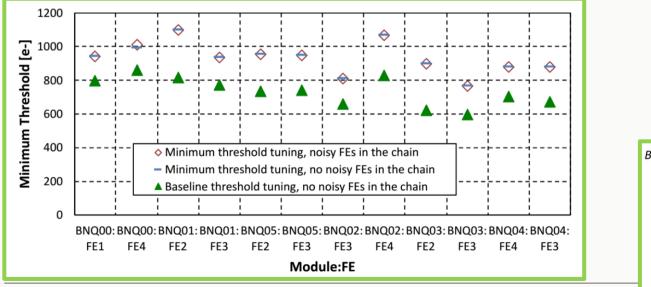

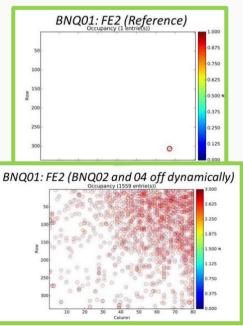

simultaneous source scan with full prototype

- effects of transients in the LV line

- noise pickup

- with FE-I4 modules, oscillations can be triggered by overloading the SLDO regulator (noisy module)

- effect on remaining modules was tested: low to no effect

24

## UPGRADES FOR SERIAL POWERING

- protection mechanisms for front-ends required:

- large transients can be dangerous for modules

- FE chips for ATLAS and CMS upgrades will have two protection mechanisms:

- overvoltage protection

- $\rightarrow$  simply voltage clamp (2V) in parallel to regulator

- under-shunt-current protection

- → shunt current is sensed and output voltage of regulator is lowered if this shunt current is too small

- Serial Powering is Standard Solution for the ATLAS and CMS Pixel Detector Upgrades

- lower losses on powering cables

- less material in the detector

- not DC-DC converters in the detector

- Serial Powering comes with several challenges:

- parallel powering of front-end chips on modules

- distribution of high voltage to sensors

- safe operation of chain in case of noisy front-ends

- thermal management of the modules

- right choice of power supplies