# Working with the USB Stick

- contains all needed programs, vhdl code and documentation

- copy terascale-DWS folder into home (all future paths are relative to this folder)

- open terminal and type df

- /media/fpga/12345... should be displayed

- copy string after ...fpga/

- open terascale-DWS/setup.py

- paste string between // at TS\_INSTALL\_DIR

- export TS\_INSTALL\_DIR=/media/fpga/12345.../ubuntu\_16

- go into terascale-DWS folder and type source setup.py

# **VHDL WORKSHOP**

Philipp Horn

#### Structure

- Introduction

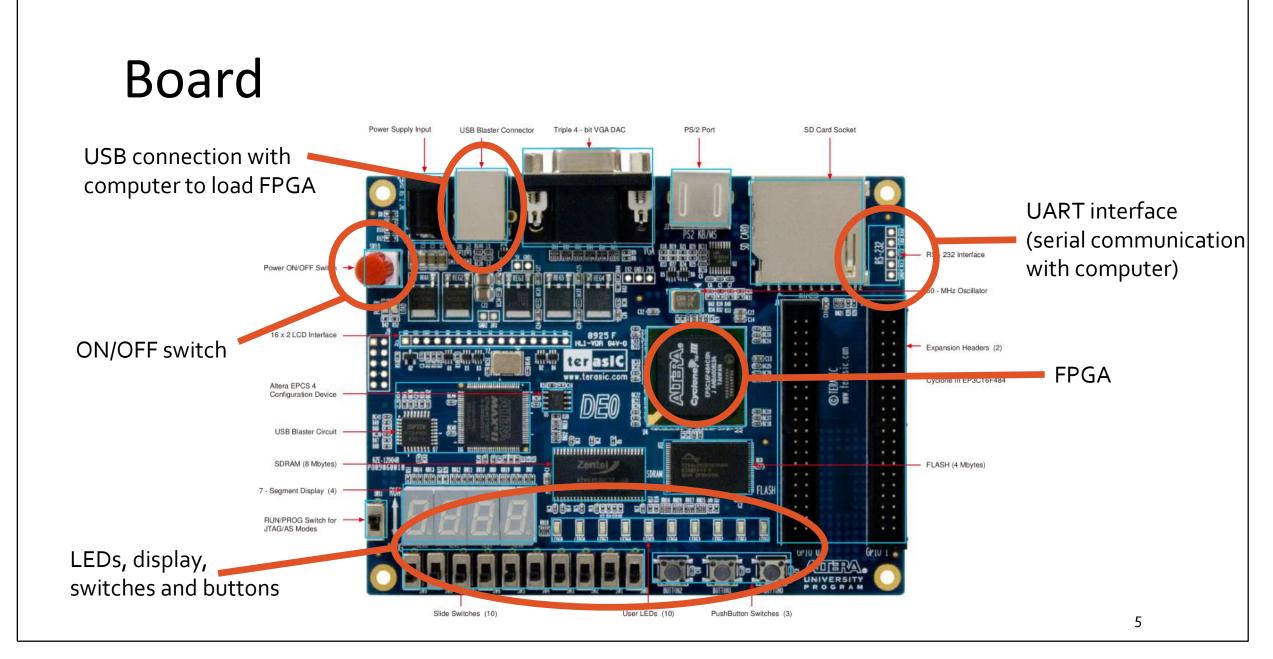

- Board

- Setup of every .vhd File

- First Example

- Starting a Simulation

- First Exercise

- Applying Design to Hardware

- Designing a Project

#### Introduction

- VHDL

- Very High Speed Integrated Circuit Hardware Description Language

- describes the operation of a logical circuit (e.g. FPGA)

- concurrent system (unlike procedural computing languages such as C)

- one .vhd text file = one module/entity (piece of hardware) containing

- interface to outer world (e.g. LEDs, switches, ...)

- functionality (how input is handled and connected to output)

- simulation program is used to test the logic design (modelsim)

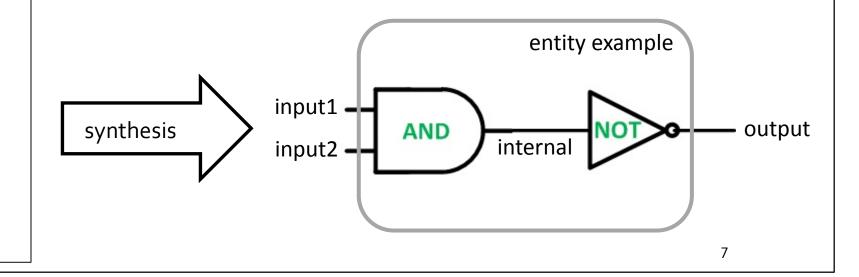

- synthesis program translates text files to "gates and wires" that are mapped on the FPGA

- Quartus provides these programs, a complicated GUI and a lot more

- we will use hdlmake, a powerful tool to manage HDL code and write synthesis and simulation Makefiles

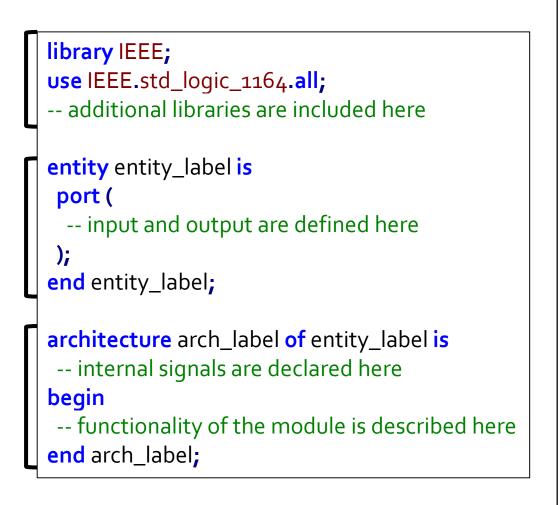

# Setup of every .vhd File

- green: comments started with --

- **blue**: keywords for VHDL syntax

- black: arbitrary identifiers

- red: library

- Implementing data type std\_logic

- has 9 possible values (most important: '0', '1',)

- single quotation mark is important

- Port:

- Definition of interface

- Architecture:

- Implementation of functionality

### First Example – NAND Gate

#### **library** IEEE;

use IEEE.std\_logic\_1164.all;

#### entity example is port (

```

input1 : in std_logic;

input2 : in std_logic;

output : out std_logic := '0';

);

end entity;

```

```

architecture arch of example is

signal internal : std_logic := '0';

begin

internal <= input1 and input2;

output <= not internal;

end arch;</pre>

```

#### • Ports:

- define two input and one output signals

- possible to give default value

#### • Architecture:

- declare one internal signal

- Assigning values to signals and output ports

- order is not important

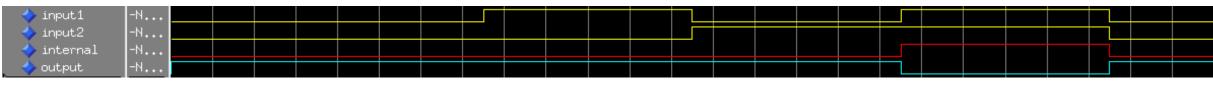

# Starting a Simulation

- test logic design using simulation models (test bench)

- they control input ports and can check output ports

- test benches are provided for this workshop

- procedure for every simulation:

- go to firmware/sim/modelsim/example

- type hdlmake (uses Manifest.py files to collect necessary files to setup simulation and writes a Makefile)

- type make

```

library IEEE;

use IEEE.std logic 1164.all;

entity example is

port (

input1: in std logic;

input2 : in std_logic;

output : out std logic := '0'

);

end entity;

architecture arch of example is

signal internal : std logic := '0';

begin

internal <= input1 and input2;</pre>

output <= not internal;</pre>

end arch;

```

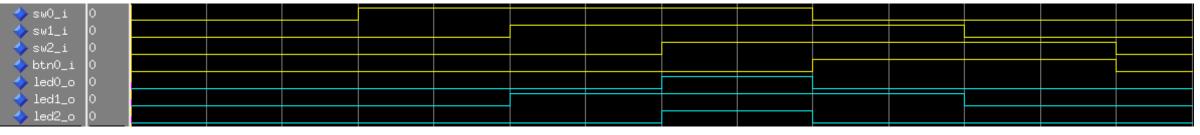

#### 1. Exercise – Logic Gates

- open firmware/modules/gates/gates.vhd with a text editor

- implement following functionality:

- switch 0, 1 and 2 are on  $\rightarrow$  LED 0 is on

- at least two of the switches 0, 1 and 2 are on  $\rightarrow$  LED 1 is on

- switch 2 is on and button 0 is not pressed  $\rightarrow$  LED 2 is on

- simulation in firmware/sim/modelsim/gates

- use parenthesis to control priority: -

not, and, or, nand

• possible logic gates:

nor, xor, xnor

architecture arch of example is

begin

output <= not (input1 or input2);

end arch;</pre>

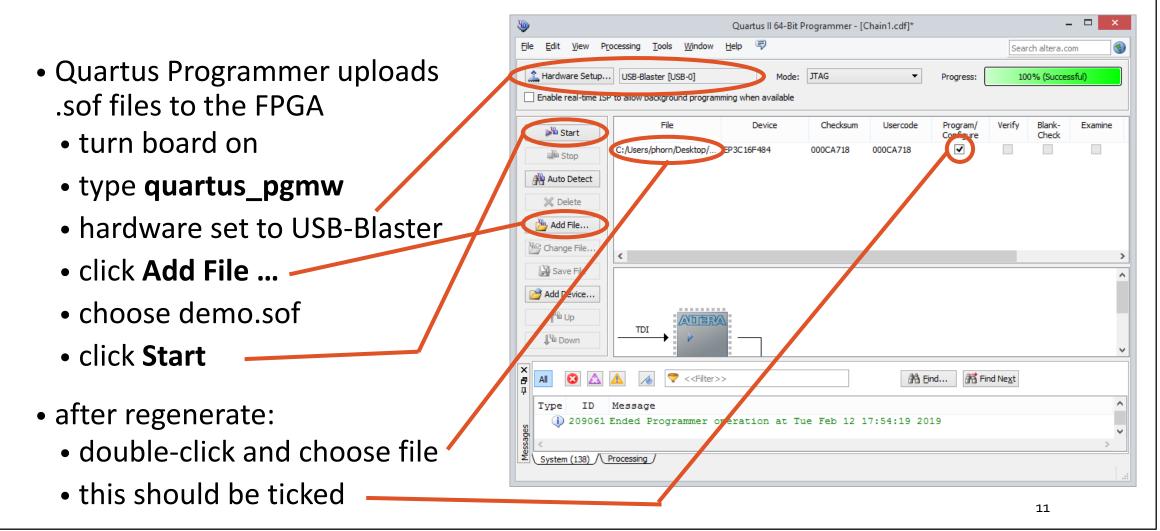

# Applying the Design to Hardware

- go to firmware/syn/de0\_quartus\_gates

- pinout.tcl

- script, which maps ports to pins of FPGA

- these pins are connected to other components of the board

- type hdlmake (writes Makefile)

- type make

- demo.sof is generated

- regenerate file:

- type make clean

- type make

set\_location\_assignment PIN\_H2 -to btn0\_i set\_location\_assignment PIN\_J6 -to sw0\_i set\_location\_assignment PIN\_H5 -to sw1\_i set\_location\_assignment PIN\_H6 -to sw2\_i

# Applying the Design to Hardware

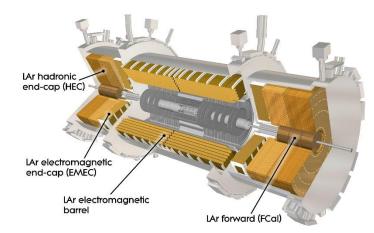

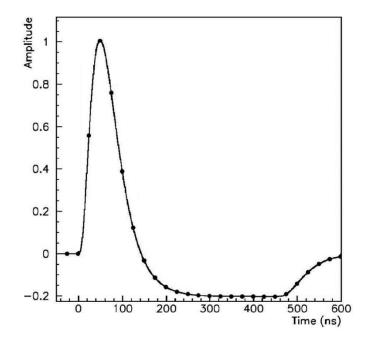

#### **Data Processing**

- ATLAS calorimeter at CERN measures energy of particles

- interaction between particle and calorimeter generates electric pulse with a amplitude corresponding to energy

- analog pulse is digitized

- ADC samples are filtered to reduce noise

- identify maximum to calculate energy of particle

- 40 MHz data rate on 182,468 readout channels

- $\rightarrow$  fast concurrent system needed

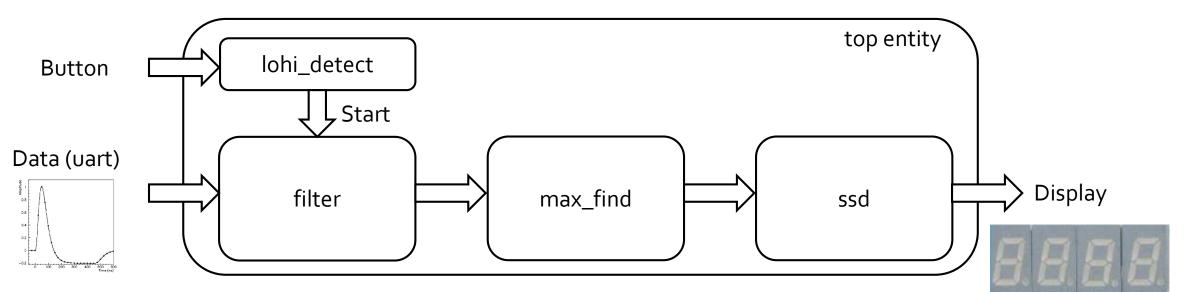

# Designing a Project – Data Processing

- project is divided in several entities/modules inside the "top" entity

- each module will be developed and simulated separately

- lohi\_detect: detects rising edge of button and generates start signal

- filter: process data stream upon receiving start signal

- max\_find: detect maximum value

- ssd: prepare value for seven segment display

#### Process

process\_label: process(sensitivity list)

begin

-- sequential statements

end process process\_label;

- operates procedural and are preceded by event control

- process is executed every time a signal in **sensitivity list** changes

- multiple assignments of same signal possible

- signal adopts value of final assignment

- if condition similar to procedural computing languages

process\_label: process(clk)

begin

if rising\_edge(clk) then

-- sequential statements

end if;

end process process\_label;

- usually process is used with a clock (clk)

- signal, which alternates between '0' and '1' with a fixed frequency

- sequential statements of the left process are always executes, when the clock switches from '0' to '1'

if cond1 then

-- sequential statements

elsif cond2 then

-- sequential statements

else

-- sequential statements

end if;

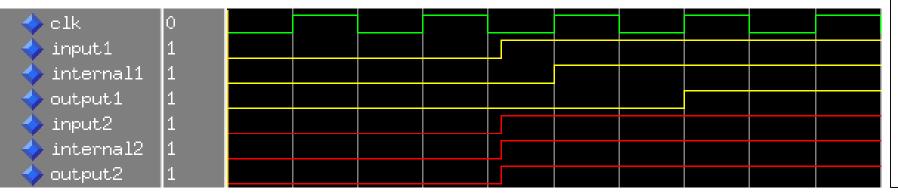

#### Process - Example

- value of signal inside a process is adopted at the end of the process

- inside of process:

- internal1 is asserted one clock cycles after input1

- output1 is asserted two clock cycles after input1

- outside of process:

- internal2 and output2 are asserted at the same time as input2

entity example2 is

port (

clk : in std\_logic;

input1 : in std\_logic;

input2 : in std\_logic;

output1 : out std\_logic := '0';

output2 : out std\_logic := '0'

);

end entity;

architecture arch of example2 is

signal internal1 : std\_logic := '0';

signal internal2 : std\_logic := '0';

begin

process\_label: process(clk)

begin

if rising\_edge(clk) then

internal1 <= input1;

output1 <= internal1;

end if;

end process process\_label;</pre>

internal2 <= input2; output2 <= internal2;</pre>

end arch;

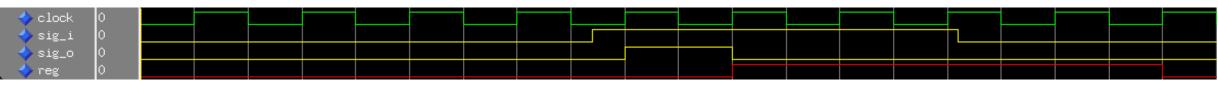

# 1. Module LoHi Detect

- open firmware/modules/lohi\_detect/lohi\_detect.vhd

- implement following functionality:

- synchronize input sig\_i

- sig\_o asserts for a single clock cycle after a rising edge of sig\_i

- simulation in firmware/sim/modelsim/lohi\_detect

- hint: internal signal reg is needed

- process statement with clock:

architecture arch of lohi\_detect is

signal reg : std\_logic := '0';

-- declare additional signals

begin

process\_label: process(clk) begin if rising\_edge(clk) then

-- write your code here end if;

end process process\_label;

-- and here

end arch;

# Additional Data Types

- std\_logic\_vector:

- array of std\_logics

- default value with others to be length independent

- unsigned / signed:

- similar to std\_logic\_vector

- mathematical operations are possible + \* / \*\*

- needs additional library IEEE.numeric\_std

- integer / natural / positive:

- natural contains zero

- use range to limit number of bits (default = 32)

#### boolean

- possible values: true and false

- used with any of the relational operators < > <= >= = /=

signal D1 : boolean := false;

signal B1 : unsigned(2 downto 0) := "110"; -- equals 6 = 4 + 2

signal B2 : signed(2 downto 0) := "110"; -- equals -2 = -4 + 2

signal A1 : std\_logic\_vector(6 downto 0) := (others => '0');

signal C1 : integer := -2; signal C2 : natural := 0; signal C3 : integer range 5 to 100 := 7;

> if A1 = "0100110" then if C1 <= B2 then

#### Generics

- optional possibility to passes specific information to the entity

- common usage: define number of bits for port vectors

- change default value of bit\_width to change length of data\_i and data\_o

- vector with 16 bit has range (15 downto 0)

| • $\rightarrow$ bit width-1 | and the many final in                 |

|-----------------------------|---------------------------------------|

|                             | entity max_find is                    |

|                             | generic (                             |

|                             | <pre>bit_width : positive := 16</pre> |

|                             | );                                    |

|                             | port (                                |

|                             | data i <b>jin</b> uncignod(bit width  |

```

data_i : in unsigned(bit_width-1 downto 0);

data_o : out unsigned(bit_width-1 downto 0) := (others => '0')

);

```

```

end max_find;

```

### 2. Module "Max Find"

- open firmware/modules/max\_find/max\_find.vhd

- implement following functionality:

- data\_o is maximum value of all previous data\_i

- start\_i resets this maximum (has priority)

- simulation in firmware/sim/modelsim/max\_find

• if condition:

if cond1 then

-- sequential statements

elsif cond2 then

-- sequential statements

else

-- sequential statements

end if;

• internal signal declaration necessary, because reading of output not possible:

signal B : unsigned(bit\_width-1 downto 0) := (others => '0');

### Data Type Conversion

- Between unsigned/signed and std\_logic\_vector:

- signals need to have the same width

A\_std <= std\_logic\_vector(B\_sig);

A\_std <= std\_logic\_vector(C\_uns);</pre>

B\_sig <= signed(A\_std); C\_uns <= unsigned(A\_std);</pre>

- Between unsigned/signed and integer:

- specification of the intended bit width from integer required

D\_int <= to\_integer(B\_sig);

D\_int <= to\_integer(C\_uns);</pre>

B\_sig <= to\_signed(D\_int,bit\_width); C\_uns <= to\_unsigned(D\_int,bit\_width);</pre>

- not possible to convert directly between integer and std\_logic\_vector

- first convert to signed or unsigned

# Type Declaration

type boolean is (false, true);

• examples of predefined types:

type std\_logic\_vector is array (natural range <>) of std\_logic;

- Boolean is an enumerate of length two

- std\_logic\_vector is array of std\_logic with undefined length

- define a matrix:

- written between architecture and begin

- type matrix\_t is array of std\_logic\_vectors with undefined length

- signal matrix\_s is array of std\_logic\_vectors with length 4

```

architecture arch of entity_label is

type matrix_t is array (natural range <>) of std_logic_vector(6 downto 0);

signal matrix_s : matrix_t(3 downto 0);

begin

```

• type conversion:

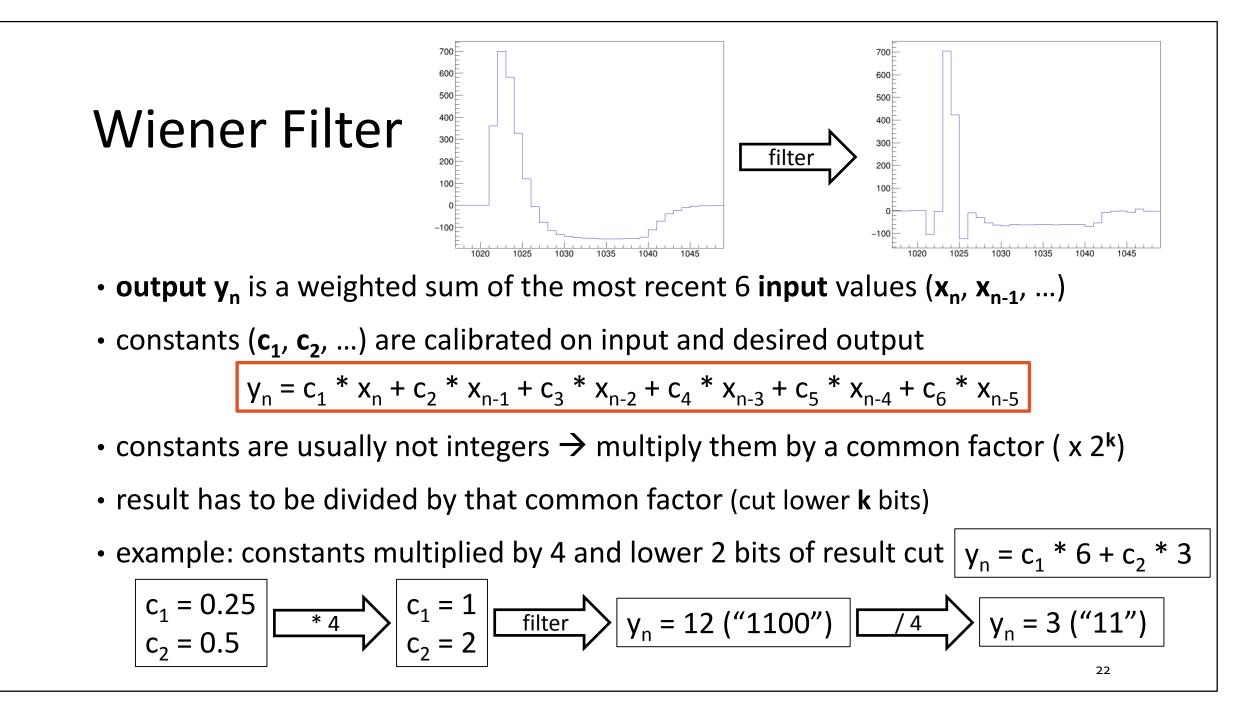

# 3. Module "filter"

D\_int <= to\_integer(C\_uns); C\_uns <= to\_unsigned(D\_int,bit\_width);</pre>

open firmware/modules/filter/filter.vhd with a text editor

$$y_n = c_1 * x_n + c_2 * x_{n-1} + c_3 * x_{n-2} + c_4 * x_{n-3} + c_5 * x_{n-4} + c_6 * x_{n-5}$$

- implement following functionality:

- data\_o ( $y_n$ ) is a weighted sum of the most recent 6 data\_i values ( $x_n, x_{n-1}, ...$ )

- use process to buffer  $\mathbf{x}_{n-1}$ ,  $\mathbf{x}_{n-2}$ , ...

- convert input to integer and result to unsigned data\_uns

- simulation in firmware/sim/modelsim/filter

- usage of type definition and loop possible

# **Conditional Signal Assignment**

- outside of processes

- when / else:

- value is assigned to **output1** based on conditions

- more general method (any boolean expression possible)

- counterpart to "if condition" in process

- input1/2/3 can be signals or values

- cond1 and cond2 are bools

- with / select:

- value is assigned to output2 based on value of internal

- rather specific method (equality checking)

- A, B, C, choise1 and choice2 can be signals or values

- value is assigned to output2 based on possible values of selection

output1 <= input1 when cond1 else

input2 when cond2 else

input3;</pre>

with internal select

# "single disp"

- **firmware/modules/ssd/single\_disp.vhd** shown on the right

- example for conditional signal assignment

- converts the single digit number\_i (0-9) to the seven segment display vector seg\_o

- if number\_i = 8 → all bits of seg\_o needs to be active

- number\_i > 9 results only in the assertion of the middle segment

- hardware might require active low signals

- '0' means light is on

- boolean decides if the signal is inverted

```

entity single disp is

generic(

invert : boolean := false

);

port(

number i : in unsigned(3 downto 0);

seg o : out std logic vector(6 downto 0)

);

end entity:

architecture arch of single disp is

signal seg s : std logic vector(6 downto 0);

begin

with number_i select

seg s <= "0111111" when "0000", -- 0

"0000110" when "0001", -- 1

"1011011" when "0010", -- 2

"1001111" when "0011", -- 3

"1100110" when "0100", -- 4

"1101101" when "0101", -- 5

"1111101" when "0110", -- 6

"0000111" when "0111", -- 7

"1111111" when "1000", -- 8

"1101111" when "1001", -- 9

"1000000" when others;

seg o <= not seg s when invert else

seg s;

end arch;

25

```

# Mapping of entities

• reuse an entity as a module in a different entity

architecture arch of seconds is

signal internal : std\_logic\_vector(7 downto 0);

begin

```

map_label: entity work.single_disp

generic map(

invert => true

```

#### port map(

```

number_i => "1000",

seg_o => internal(6 downto 0)

);

```

end arch;

```

entity single_disp is

generic(

invert : boolean := false

);

port(

number_i : in unsigned(3 downto 0);

seg_o : out std_logic_vector(6 downto 0)

);

end entity;

```

- single\_disp entity (generic and ports on the top) will be needed for next module seconds (architecture on the left)

- work denotes the current working library

- generics and ports from the entity on the left

- connected values and signals on the right

- generics can be omitted (the default value would be used)

- widths need to align (shorten internal)

# 2. Exercise – Second Counter

- open firmware/modules/ssd/seconds.vhd with a text editor

- implement following functionality:

- **counter** is increased with every rising edge of clock **clk**

- when counter reaches counter\_max one second passed

- for simulation **counter\_max** is set to 5

- output seconds sec to seven segment display ss\_d1\_o

- after nine seconds: start again at zero

- simulation in firmware/sim/modelsim/seconds

- synthesis in firmware/syn/de0\_quartus\_seconds

```

architecture arch of seconds is

begin

map label: entity work.single disp

generic map(

invert => invert

port map(

number i => B,

seg_o => C

);

end arch;

```

| -        | <b>)</b> clock | 0       |         |       | Ŀпп    |       |         |       |        |       |        |           |           |           |           |           |          |

|----------|----------------|---------|---------|-------|--------|-------|---------|-------|--------|-------|--------|-----------|-----------|-----------|-----------|-----------|----------|

|          | > counter      | 1       | 23      | 4 5 1 | 23     | 4 5 ( | 123     | 4 5 1 | 23     | 4 5 1 | 23     | 4 5 1 2 3 | 4 5 1 2 3 | 4 5 1 2 3 | 4 5 1 2 3 | 4 5 1 2 3 | 4 5 1    |

|          | > sec          | 0       | 0       | 1     |        | 2     | 2       | 3     |        | 4     |        | 5         | 6         | 7         | 8         | 9         | 0        |

| <b>+</b> | 🔈 ss_d1_o 🛛    | 1000000 | 1000000 | 1     | 111001 |       | 0100100 | 0     | 110000 | 0     | 011001 | 0010010   | 0000010   | 1111000   | 0000000   | 0010000   | <u> </u> |

<sup>•</sup> mapping:

#### Generate

• if generate: conditional creating of components

generate\_label: if cond1 generate

output <= input;

end generate;</pre>

- for generate: repeating a group of identical components

- example: assign first 5 bits of every std\_logic\_vector of matrix\_s

```

architecture arch of entity_label is

signal internal : std_logic_vector(4 downto 0) := (others => '0');

type matrix_t is array (natural range <>) of std_logic_vector(6 downto 0);

signal matrix_s : matrix_t(2 downto 0);

begin

matrix_s(0)(4 downto 0) <= internal;

matrix_s(1)(4 downto 0) <= internal;

matrix_s(2)(4 downto 0) <= internal;

end arch;. combined to generate statement:

```

# 4. Module "ssd"

- open firmware/modules/ssd/ssd.vhd with a text editor

- implement following functionality:

- four digit number input data\_i

- use division / and modulo mod to separate digits

- save all results in matrices quotient and remainder

- route separate digits to single\_disp to receive ss\_ds

- output four std\_logic\_vectors (seven segment display)

- simulation in firmware/sim/modelsim/ssd

- generate:

generate\_label: for i in 3 downto 0 generate

matrix\_s(i)(4 downto 0) <= internal;

end generate;</pre>

|   | 🔷 clock                       | 0  |               |        |     |                |    |    |

|---|-------------------------------|----|---------------|--------|-----|----------------|----|----|

|   | 🖪 🔶 data_i                    | 0  | 0             |        |     | 7352           |    | 0  |

|   | 🖃 🔶 quotient                  | {O | <u>{0}</u>    | )} {0} | £   | <b>{0} {</b> 7 | 3  | £0 |

|   | 🛓 🔶 (4)                       | 0  | 0             |        |     |                |    |    |

|   | + ~ (4)<br>+ ~ (3)<br>+ ~ (2) | 0  | 0             |        |     | 7              |    | 0  |

|   | 🚊 🔶 (2)                       | 0  | 0             |        |     | 73             |    | 0  |

|   | 📑 🔷 (1)                       | 0  | 0             |        |     | 735            |    | 0  |

|   | 😐 🔶 (0)                       | 0  | 0             |        |     | 7352           |    | 0  |

|   | 🖃 🔶 remainder                 | {0 | <u>{0} {(</u> | )} {0} | {0} | <b>{7} {</b> 3 | 33 | £0 |

|   | 🛓 🔶 (3)                       | 0  | 0             |        |     | 7              |    | 0  |

| ) | (2)                           | 0  | 0             |        |     | 3              |    | 0  |

| ' | 😐 🔷 (1)                       | 0  | 0             |        |     | 5              |    | 0  |

|   | 🔁 🔶 (0)                       | 0  | 0             |        |     | 2              |    | 0  |

|   | 😐 🔷 ss_d4_o                   | 10 | 100000        | 0      |     | 111100         | 0  | 10 |

|   | 😐 🔶 ss_d3_o 👘                 | 10 | 100000        | 0      |     | 011000         | 0  | 10 |

|   | 😐 🔶 ss_d2_o                   | 10 | 100000        | 0      |     | 00100:         | 10 | 10 |

|   | 🖪 🔶 ss_d1_o                   | 10 | 100000        | 0      |     | 010010         | 0  | 10 |

# 5. Module "top"

- solution of previous modules:

- firmware/modules/.top/

- copy and overwrite self written .vhd file

- open firmware/modules/top/top.vhd with a text editor

- implement following functionality

- entity data\_uart provides data (in simulation only a constant set)

- map all 4 modules into this entity and use internal signals to connect them

- simulation in firmware/sim/modelsim/top

- synthesis in firmware/syn/de0\_quartus\_top

### Sending data to FPGA

- go into terascale-DWS folder

- type python/slowCtrl.py

- choose displayed input file (type 1)

- choose displayed UART port (type 5)

- send pulses by typing 6

```

(1) select ADC data input file [/home/fpga/terascale-DWS/python/adcData/ADC_samples.txt]

(2) set scaling factor [1.0]

(3) set single value index [0]

(4) plot ADC samples

(5) open UART port [/dev/ttyS0]

(6) send pulse to fpga

(7) send single value to fpga

(0) exit

Enter option [5]:

```

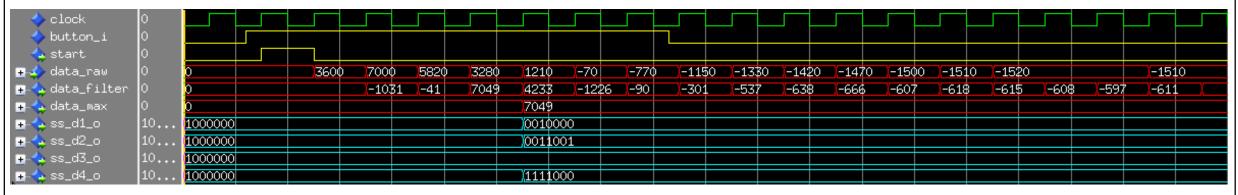

# Signal Tap

- powerful debugging tool, which enables to look inside FPGA

- type quartus\_stpw

- open file **stp1.stp**

- set hardware to USB Blaster

- trigger is already set to rising edge of button

- arm trigger -

- push button on board

# Writing a Test Bench

- test bench (**tb**) = entity used for simulation

- example: **seconds\_tb** on the right

- generics definition but without port

- example: set **counter\_max** = 5 to shorten simulation

- maps unit under test (uut) with internal signals

- output is not connected (**open**)

- clock (clk) generation via process

- wait for statement not synthesizable

```

library IEEE;

use IEEE.std logic 1164.all;

entity seconds tb is

generic(

counter max : positive := 5;

invert : boolean := true

);

end seconds tb;

architecture tb of seconds tb is

signal clk : std logic := '0';

begin

uut: entity work.seconds

generic map(

counter max => counter max,

invert

=> invert

port map(

clk

=> clk,

ss d1 o => open

);

clk proc: process

begin

clk <= '0'; -- clock cycle is 20 ns

wait for 10 ns;

clk <= '1':

wait for 10 ns;

end process clk proc;

end architecture;

```

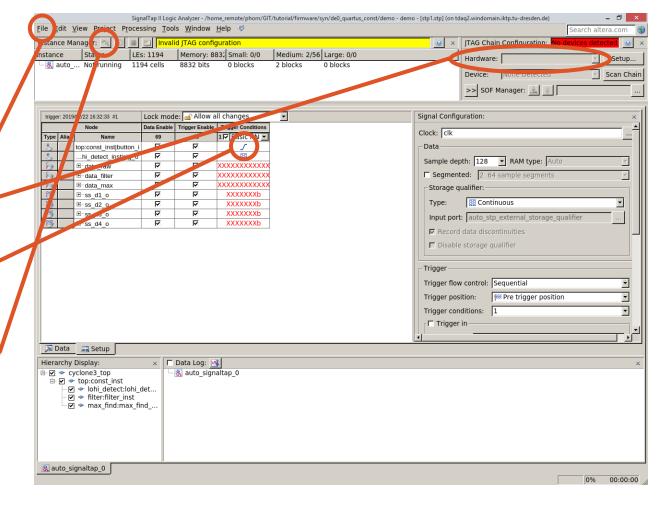

#### Input generation

additional possibilities written in test bench architecture

count proc: process(clk) begin if rising\_edge(clk) then counter <= counter + 1; end if; end process count proc; sim proc: process(clk) if rising edge(clk) then case counter is input1 <= '1'; input2 <= '0'; input1 <= '0'; input2 <= '1'; input1 <= '1'; input2 <= '1'; when others => input1 <= '0'; input2 <= '0'; end process sim proc;

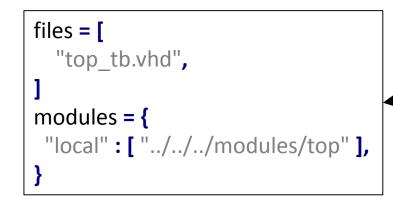

### hdlmake

- file **firmware/sim/modelsim/top/Manifest.py** is starting point for **top** simulation

- sim\_post\_cmd is a command that is issued after the simulation process has finished

- modules points to other Manifest.py files in local folders

- add needed files for simulation

# Reset signal

- input to initialize signals to a predetermined state

- synchronous: reset is checked at the rising edge of clock

- asynchronous: reset in sensitivity list of process

```

test_proc: process(clk, reset)

begin

if reset = '1' then

sig_o <= '0';

elsif rising_edge(clk) then

sig_o <= sig_i;

end if;

end process;</pre>

```

```

entity test is

port (

clk : in std_logic;

reset : in std logic;

sig_i : in std_logic;

sig_o : out std_logic

);

end entity;

test proc: process(clk)

begin

if rising_edge(clk) then

if reset = '1' then

sig o <= '0';

else

sig o <= sig i;

end if;

end if;

end process;

```

#### **Other Concepts**

- **package** = collection of declarations

- written in separate file

- can be called and used in an entity

- function = describe an algorithm

- one output and multiple inputs

- attributes = parameters of signal

signal A : std\_logic\_vector(7 downto 0);

A'left -- equals 7

A'range -- equals 7 downto 0

A'length -- equals 8

label\_gen: for i in A'range generate

package utils is constant six : positive := 6; type matrix\_t is array (natural range <>) of std\_logic\_vector(6 downto 0); function div(a : natural; b : positive) return natural; end package;

package body utils is

function div(a : natural; b : positive) return natural is

begin

return a / b;

end function;

end package body;

| use work.utils.all;                                             |

|-----------------------------------------------------------------|

| entity test is                                                  |

| generic (                                                       |

| gen : natural := 12;                                            |

| port (                                                          |

| data_i : in matrix_t(con downto 0);                             |

| <pre>data_o : out std_logic_vector(div(gen,con) downto 0)</pre> |

| );                                                              |

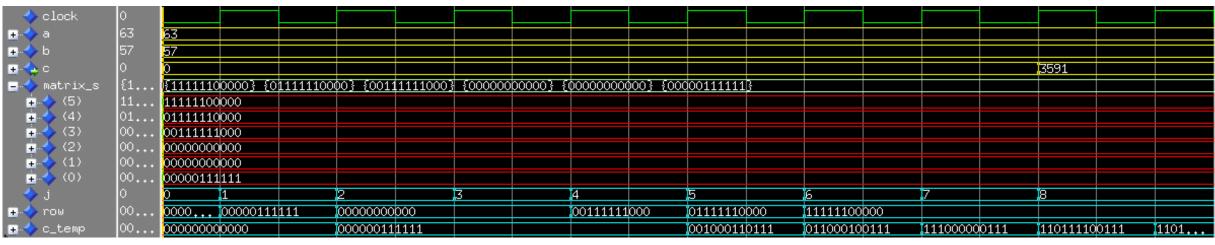

# **Binary Addition**

- open firmware/modules/bin\_add/bin\_add.vhd

- implement following functionality

- assume std\_logic\_vector **input** to be unsigned numbers

- use for generate to connect single bits via logic gates

- internal carry signal needed for addition

- use temporary signal **c\_temp** for result and assign **output** with next clock cycle

- simulation in firmware/sim/modelsim/bin\_add

| - 🔷 clock -    | N            |             |             |            |   |

|----------------|--------------|-------------|-------------|------------|---|

| 😐 🔶 a 🛛 –      | N 0          | 741         | 1023        | <u>)</u> 0 |   |

| 🕳 🧇 b 🛛 –      | N 0          | 249         | 1023        | )(O        |   |

| 🖪 🛧 c 🔤 –      | N 0          |             | 990         | 2046       | 0 |

| 🖪 🔶 c_temp 🛛 - | N 0000000000 | 01111011110 | 11111111110 | 0000000000 |   |

| , <u>∓</u>     | N 0000000000 | 00111000010 | 11111111110 | 0000000000 |   |

a = 110101110

c = 111011001

carry = 001011100

b =

101011

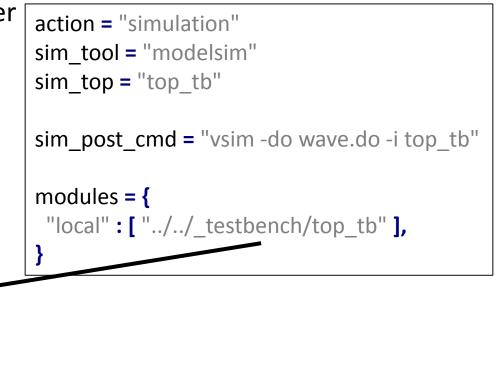

# **Binary Multiplication**

- open firmware/modules/bin\_mult/bin\_mult.vhd with a text editor

- implement following functionality

- fill **a** into row of **matrix\_s** if corresponding bit of **b** is asserted

- use **bin\_add** to keep adding **row** of **matrix\_s** to **c\_temp**

- simulation in **firmware/sim/modelsim/bin\_mult**

| a xb=         | 110101110 x 101001= |

|---------------|---------------------|

| matrix s =    | 110101110           |

| _             | + 000000000         |

| a text editor | + 110101110         |

|               | + 000000000         |

|               | + 000000000         |

| ccartad       | + 110101110         |

| sserted       |                     |

| b C =         | = 100010011011110   |