# LUXE (e+e-) detector

Noam Tal Hod

May 7 2019

### Recap

- Review of pixel technologies in the workshop

- https://indico.desy.de/indico/event/22605/session/4/contribution/7

- consensus towards ALPIDE/Malta technologies or similar (D)MAPS

- After the workshop:

- been in touch with Luciano Musa and Heinz Pernegger

- I presented LUXE in general and the detector plan particularly

- both are very enthusiastic about the experiment and about the possibility of us using their technologies

- TowerJazz link: both happy to share the technology

- discussed several options to move forward including costs (today)

- Really a production module (Chip+DAQ board / HIC)

- used by ALICE, explored by CLiC

- proton CT / hadron therapy (several places)

- <u>sPHENIX (RHIC facility at BNL)</u>, <u>NICA (Dubna)</u>,

- few applications for space (on satellites)

- Feature size 27×29  $\mu$ m<sup>2</sup> $\rightarrow$  resolution of  $\sigma$ ~5  $\mu$ m

- Time resolution of a few µs

- Probability that a random pixel fires (dark current rate) is very low: ~10<sup>-5</sup>

- orders of magnitude lower than hybrid pixels

- Using standard 180 nm TowerJazz technology

- already modified for HEP ("CERN option")

- Stitching: sensor can be as large as the wafer e.g. ~14×14 cm<sup>2</sup> w/o support structures and electrical substrates

Noam Tal Hod, WIS

Individual sensors, e.g. for a telescope

chip ~3×1.5 cm<sup>2</sup> + DAQ board (USB interface): >1500 CHF

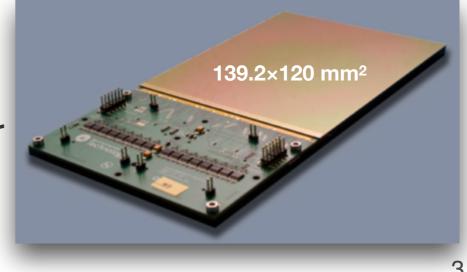

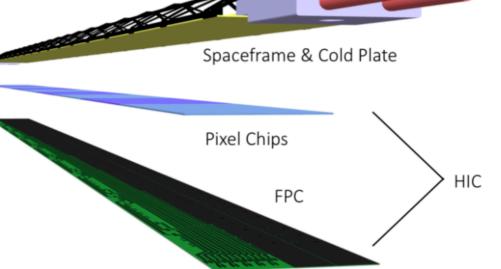

**HIC** 27×0.15 cm<sup>2</sup> (Hybrid Integrated Circuits) modules (staves)

- sensors and board glued on a carbon fibre support structure

- ~13k CHF ("gold category": >50/500k dead pixels/sensor)

- possible to go longer but requires some engineering work

- each sensor has its own readout line (2 Gb/s)

- standard Samtec cables transmit the signal

- MOSAIC readout system developed in Bari (Italy)

- can read a few staves simultaneously

- ALICE readout unit (one per stave)

- ► GBT link / PCI express → one PC can in principle handle 24 staves. Given our 10 Hz pulse rate this looks reasonable

- HICs production flow (approximately):

- 1. fabricate sensors at TowerJazz

- 2. thinning and dicing in S. Korea / Germany

- 3. testing in S. Korea

- 4. bonding to PCB, gluing, assembly at CERN

- 5. mount on the carbon fibre frame at CERN

- For our needs, the staves solution seems very appealing

- ► 4 layers × 2 sides × 2 to cover 50 cm (27×0.15 cm<sup>2</sup> staves):

- ► 16 staves + 2 spares... ~234k CHF (could be lower)

- computing costs should be small

- services & patch panels, mechanics & cooling, readout electronics & power supplies, (motorised) alignment system

- TBD (probably not below 100k CHF)

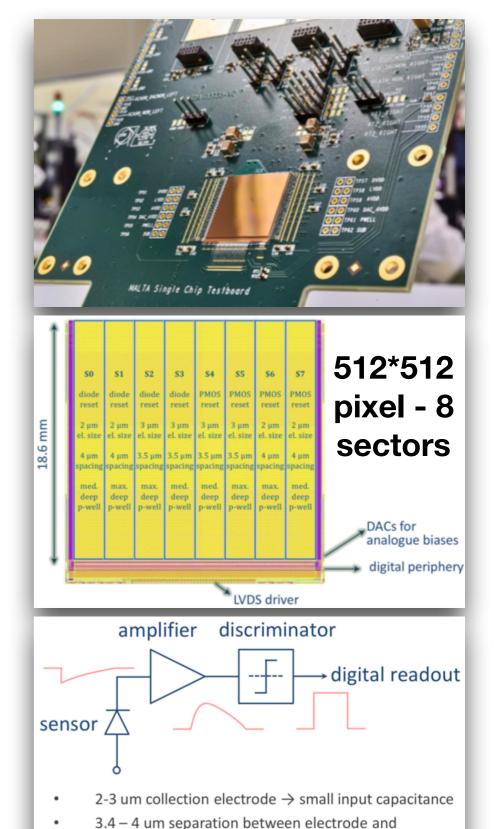

# MALTA

- Not yet a production module

- at least not a large-scale prototype yet

- R&D target rad-hardness (10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup>) and timing (peaking time<25 ns)</li>

- Feature size 36.4×36.4 µm<sup>2</sup>

- full matrix has 512x512 pixels

- ► active area of ~2x2 cm<sup>2</sup>

- asynchronous readout (reduce digital power consumption, increase hit rate capability, i.e. >100MHz/cm<sup>2</sup>)

- A few users already (PSI, high rate proton experiment in Vienna)

- Recent micro-cooling tests are successful

- Can get a test chip from Hienz for free

- xilinx evaluation board for one sensor at ~2000\$-3000\$

- can also buy a full "testbeam setup" (TBC)

- electronics  $\rightarrow$  low cross talk

- 1 uW/pixel analog power (75 mW/cm<sup>2</sup>)

- 10 mW/cm<sup>2</sup> digital power @ layer4

Sensor and analogue front-end (shaper-amplifier and discriminator) shielded from digital part to minimise crosstalk

Time walk information preserved

### Summary

- ► ALPIDE

- seems to match our needs, although the timing isn't the best

- off the shelf, can be ready in a short time, already quite integrated

- effectively no further design needed  $\rightarrow$  only some adaptations

- I will get from Luciano a detailed list of specifications

- I will get in touch with the ALPIDE simulation people

- study the detector response, efficiency, etc.

- ► New developments target smaller features  $10 \times 10 \ \mu m^2 \rightarrow \sigma \sim 1 \ \mu m$ , lower power consumption and  $\sim 100$  ns integration time

- ► MALTA:

- very promising and more cutting-edge, but not yet ready

- will require some non-negligible design/engineering work

- Recommendation:

- go with ALPIDE in phase0 while checking the developments on the MALTA front for phase1 possibly

- very preliminary & rough cost: ~350 CHF (with a grain of salt now...)

Noam Tal Hod, WIS

# BACKUP

- Produced in the TowerJazz 180nm CMOS Imaging Sensor (CIS) process

- Full CMOS within pixel matrix

#### Key concepts:

- In-pixel amplification

- In-pixel hit discrimination

- In-pixel 3-level event memory

- In-matrix zero-suppression

#### Features:

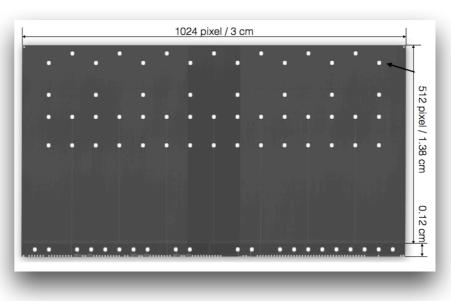

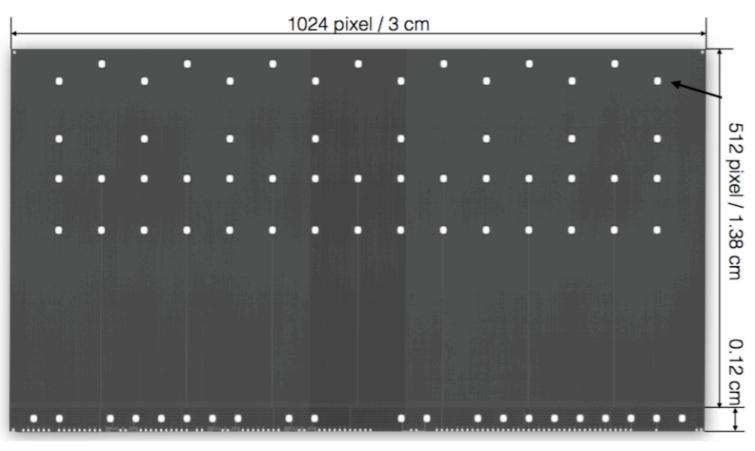

- Dimension: 30mm x 15mm (1024 x 512 pixels)

- Thinned to 50 $\mu$ m (0.05% x/X<sub>0</sub>) or 100 $\mu$ m

- Pixel pitch: 29μm x 27μm

- Possibility to apply reverse substrate bias

- Event-time resolution 2-4  $\mu$ s (charge collection time only 1-30ns, but not exploited)

- Very low power consumption (40mW/cm<sup>2</sup>) -> no cooling needed in test beam setup

- Global shutter: triggered acquisition (up to 200 kHz Pb-Pb, 1MHz pp) or continuous (progr. integration time: 1µs - ∞)

- Binary readout

- 1.2 Gbit/s high-speed link, can drive up to 5m of cable

- Two possible connection schemes: pads over the matrix and pads at the periphery

#### ALPIDE carrier card:

- Large opening underneath ALPIDE to reduce material budget

- PCIe connector used as mechanical and electrical interface (with custom electrical protocol)

- Small pads at periphery used for bonding

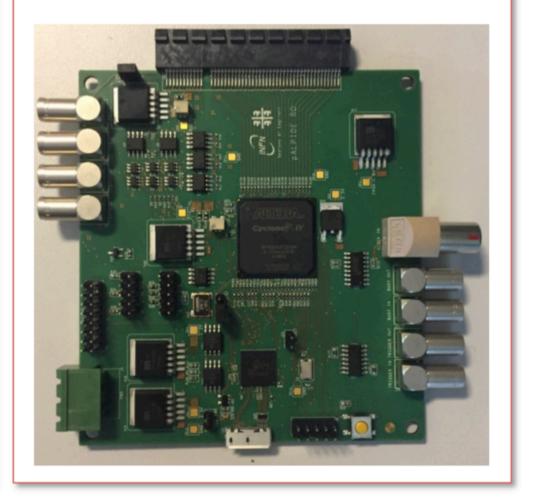

#### DAQ board:

- USB-3.0 for connection to PC

- PCle connector for carrier card

- Various GPIO connectors

- ALPIDE telescopes typically consist of 7 planes, plane distance ~2cm

- Central chip is typically treated as Device Under Test (DUT)

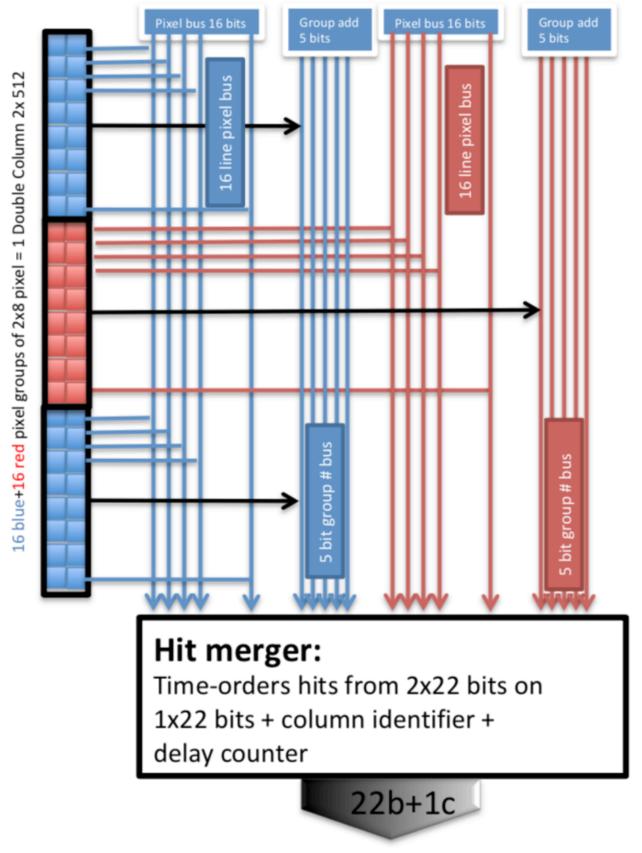

#### MALTA asynchronous readout

Noam Tal Hod, WIS