# Younes Otarid

**On behalf of the CMS Tracker group**

# Transverse momentum discriminating silicon modules for the Phase-II Upgrade of the CMS Outer Tracker

MATTER AND TECHNOLOGIES MEETING 02.02.2021

#### **Overview**

#### CMS Outer Tracker Upgrade

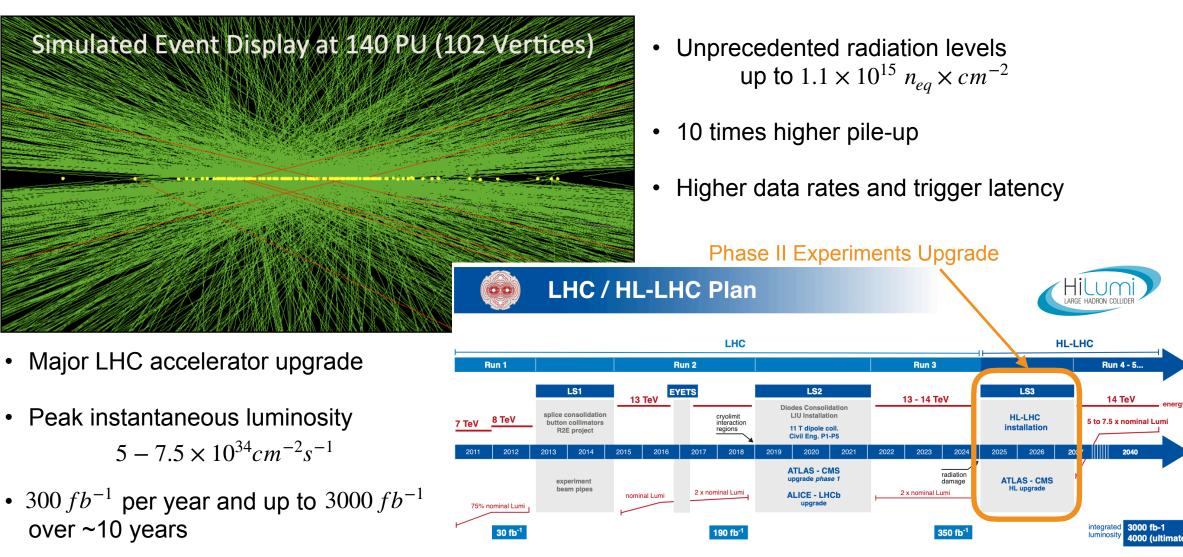

- High Luminosity LHC

- CMS experiment upgrade

- CMS Outer Tracker upgrade

#### Momentum discriminating silicon module

- Pixel-Strip silicon module concept

- Pixel-Strip silicon module design

- Pixel-Strip ASIC architecture

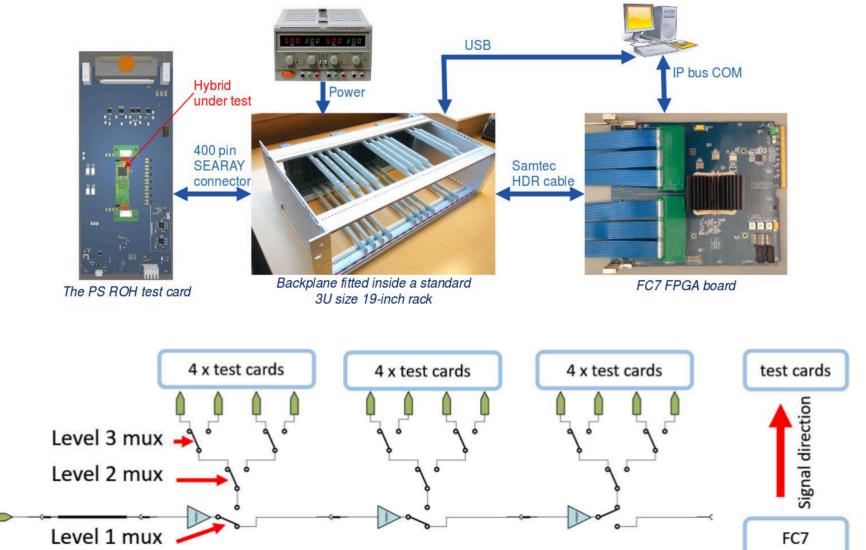

#### DAQ Test Systems

- Data acquisition test system

- Micro Data-Trigger-Control firmware

- MUX crate based test system

#### • Summary & Outlook

# **CMS Outer Tracker Upgrade**

## **High Luminosity LHC**

https://hilumilhc.web.cern.ch/content/hl-lhc-project

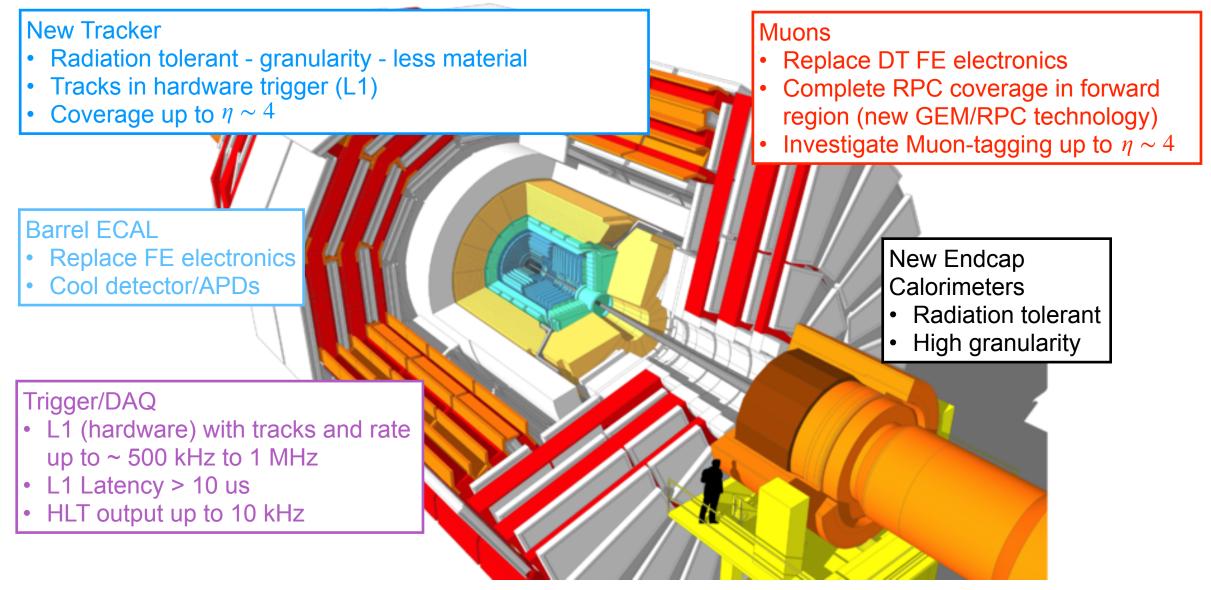

# **CMS experiment Phase II Upgrade**

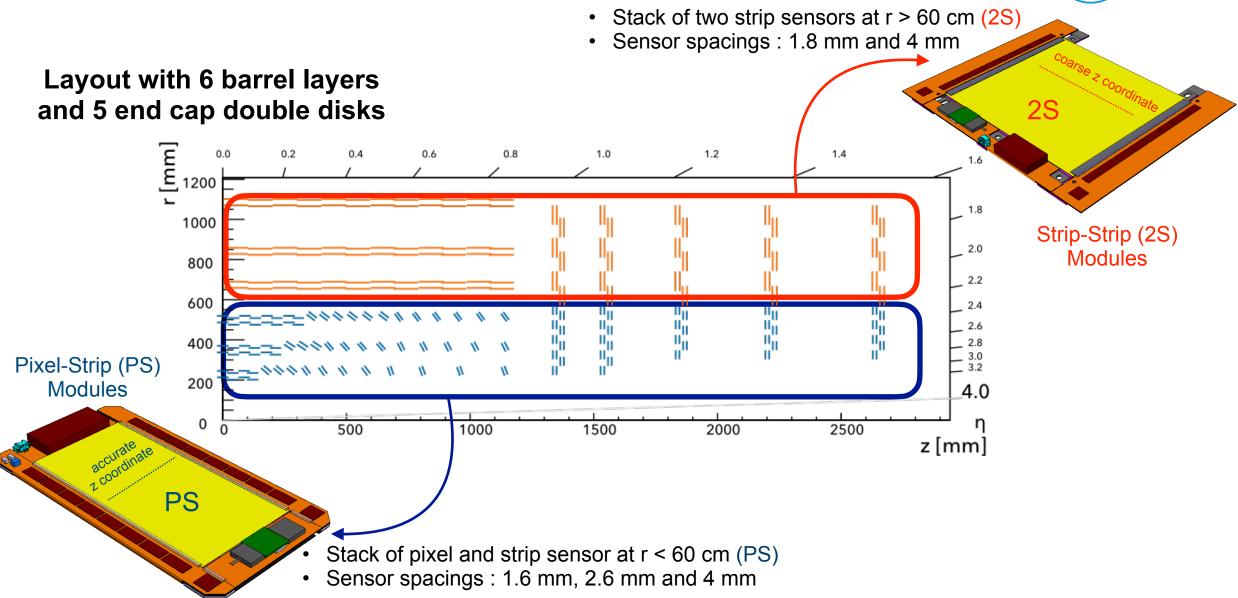

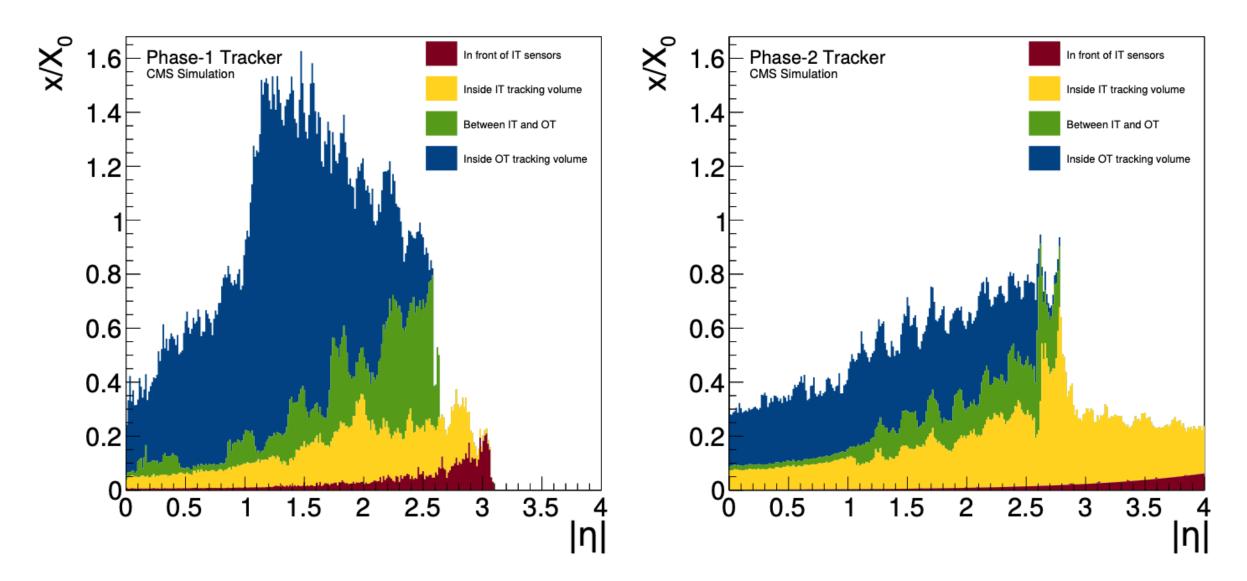

### **CMS Outer Tracker Phase II Upgrade**

# pT Discriminating Si Modules

# **Pixel-Strip (PS) Silicon Module Concept**

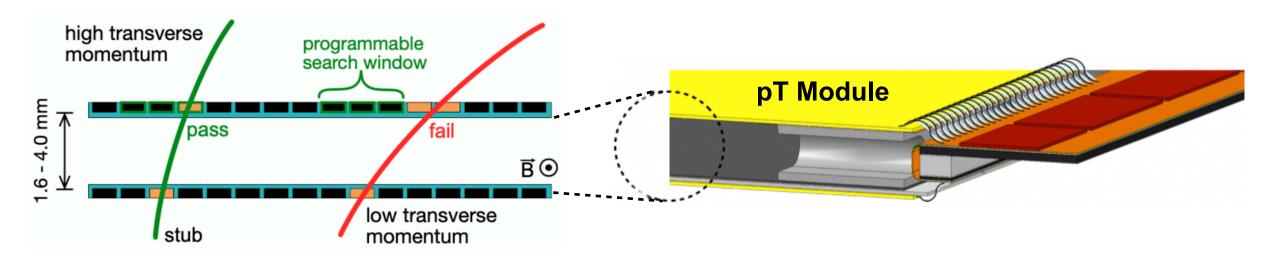

- Modules with on-board pT discrimination

- Correlation of signals from two closely spaced sensors

- Strong magnetic field exploited for local pT measurement

- Local rejection of low-pT tracks to reduce data volume

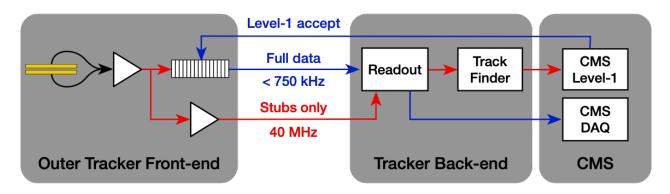

- Modules provide both Level-1 and readout data

- Trigger data ("stubs") sent every bunch crossing (40MHz)

- Readout data up to 750KHz

- "stubs" are used to form Level-1 tracks

CM

DESY.

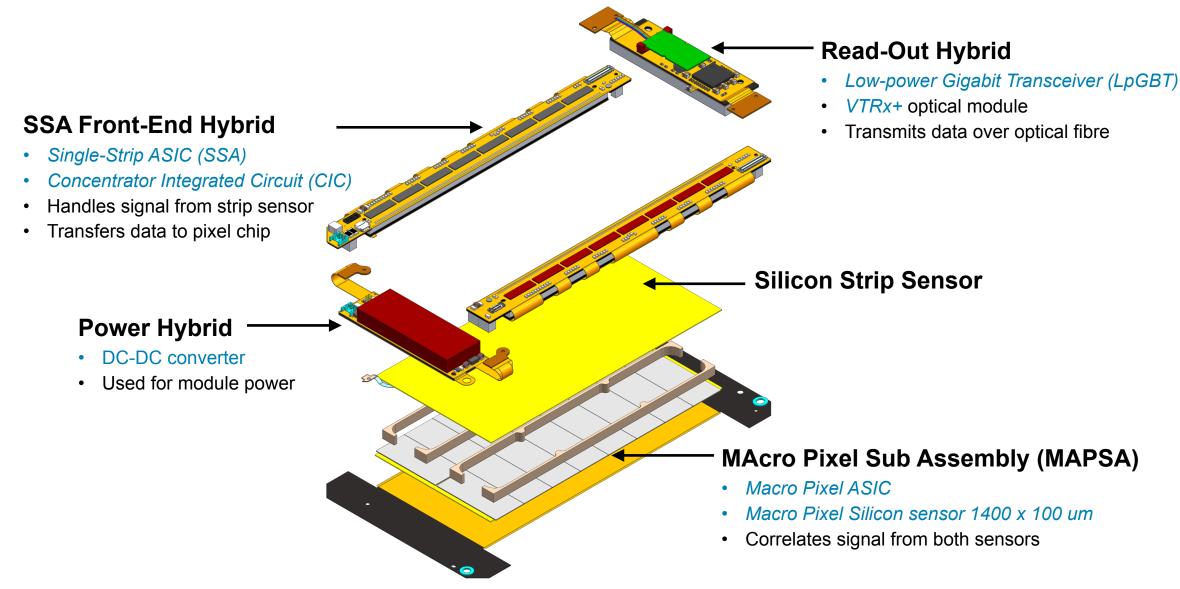

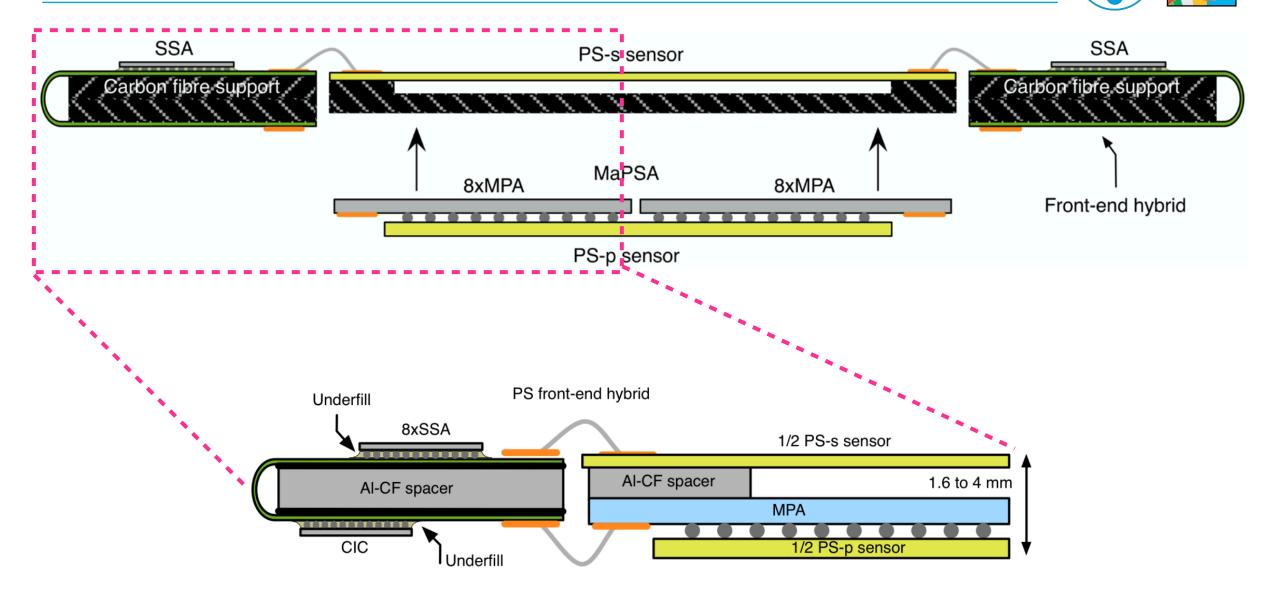

## **Pixel-Strip (PS) Silicon Module Design**

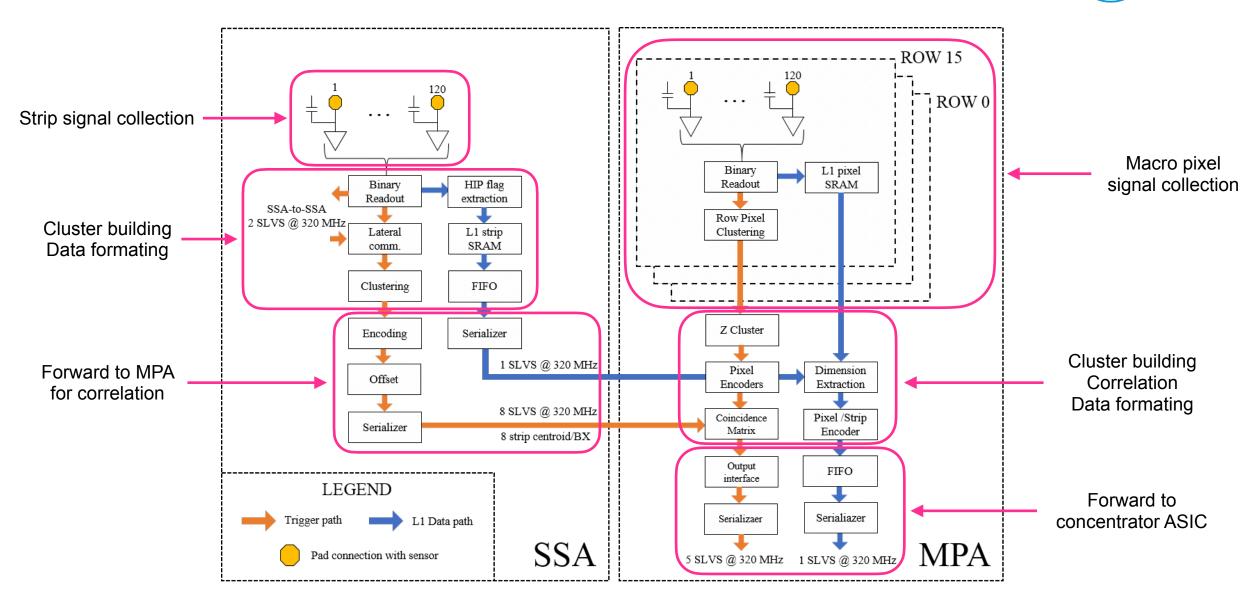

## **Pixel-Strip (PS) ASIC Architecture**

CM

DESY.

# **DAQ Test System**

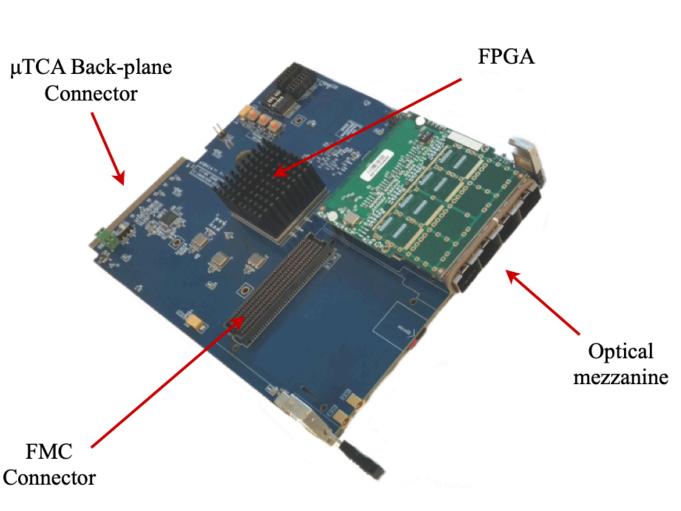

## **Data Acquisition Test System**

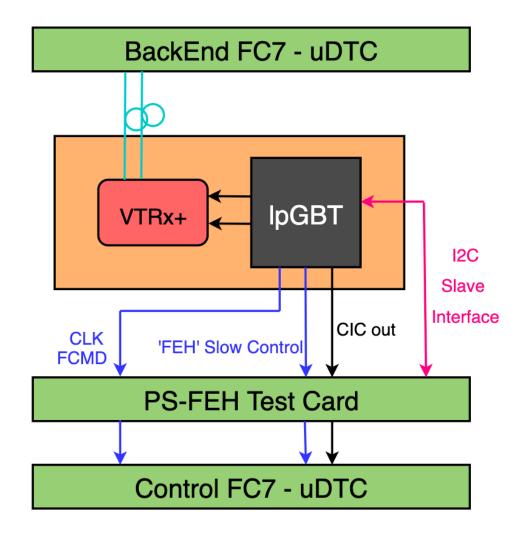

- Exploits *FC7* uTCA-compatible board for generic data acquisition and control applications

- Kintex-7 FPGA

- 2 FMC Connectors

- Advanced clock distribution system

- External DDR3 memory

- uTCA integration

- Several custom interface are supported by the system in case of needed synchronous operation

- Trigger Logic Unit (TLU)

- DIO5 (5 LEMO I/O)

- AMC13 (interface to the TCDS)

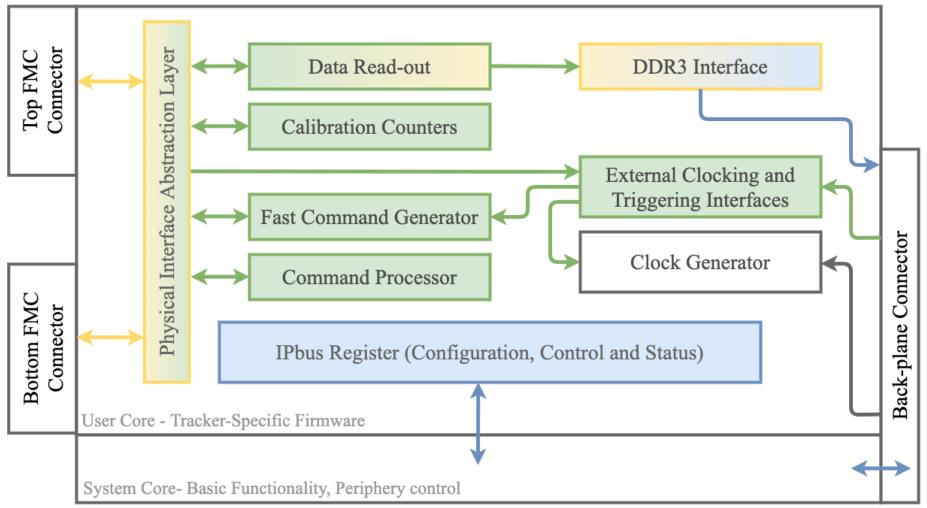

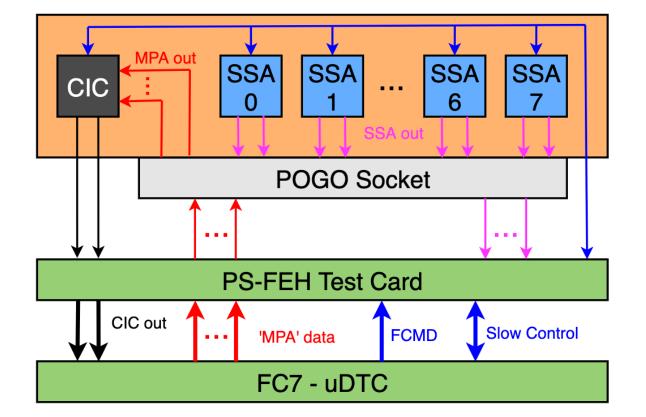

# Micro Data-Trigger-Control Firmware (uDTC)

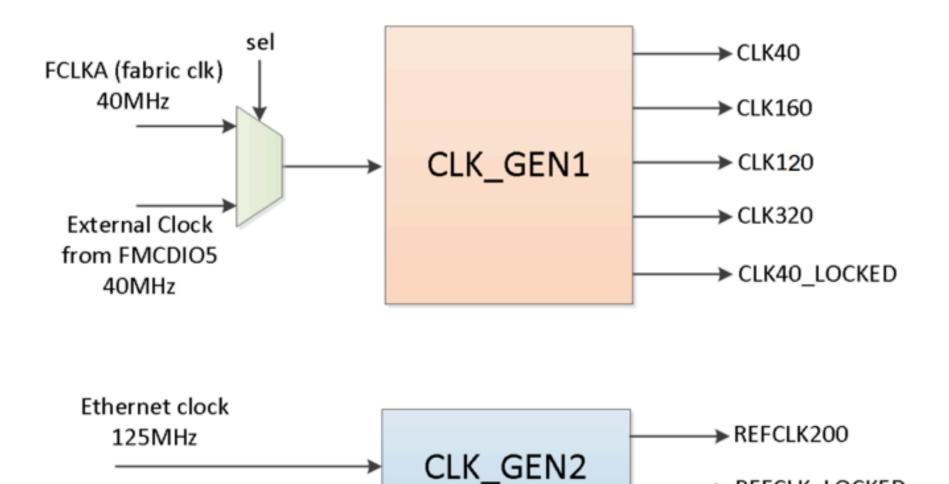

#### Clock Domains :

40 MHz 31.25 MHz 120 - 320 MHz

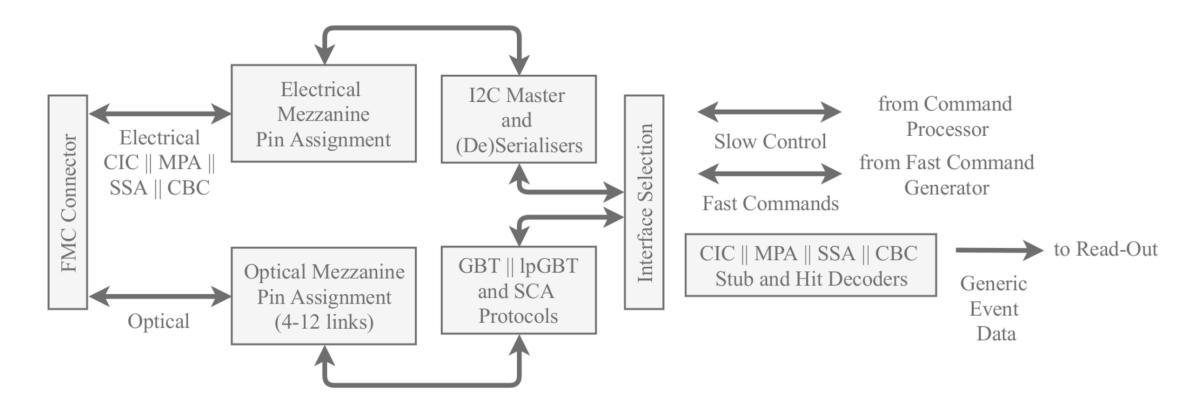

## **Physical Interface Abstraction Layer**

Abstraction layer introduced for a more efficient implementation,

providing needed support for all different front-end flavours (CIC, SSA, MPA, CBC)

including control of various interface boards

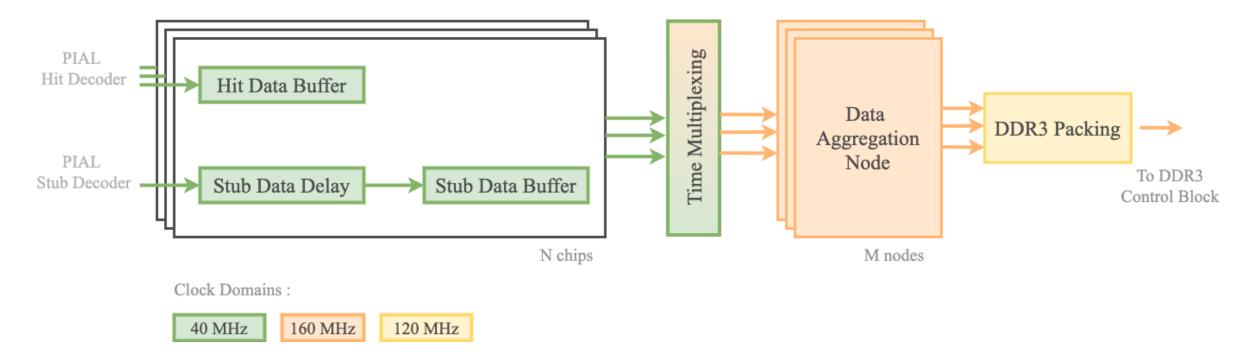

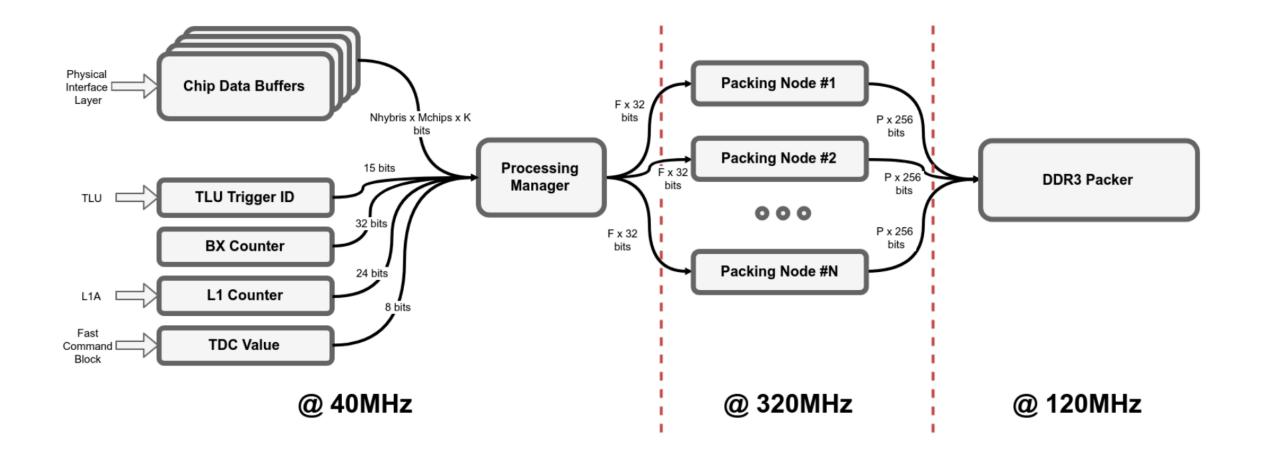

#### **Data Read-out Block**

- Aggregation of data from the Physical Interface Abstraction layer

- Data from all front-end chips/modules

- Event formatting and loading to the DDR3 memory, further read via IPbus

- Time multiplexing method for job distribution to the data aggregation nodes

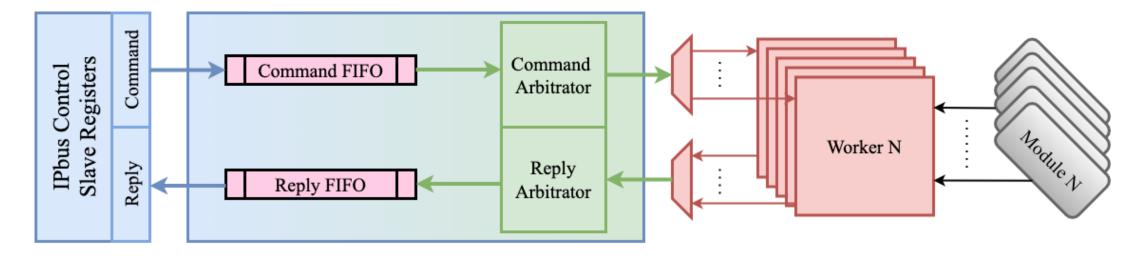

#### **Command Processor Block**

- Command Processor Core

- Unpacking/Packing command and replies from/to IPbus

- Command and Reply FIFOs for Clock Domain Crossing

- Command Processor Worker

- Implements module slow control functions and routines

Clock Domains :

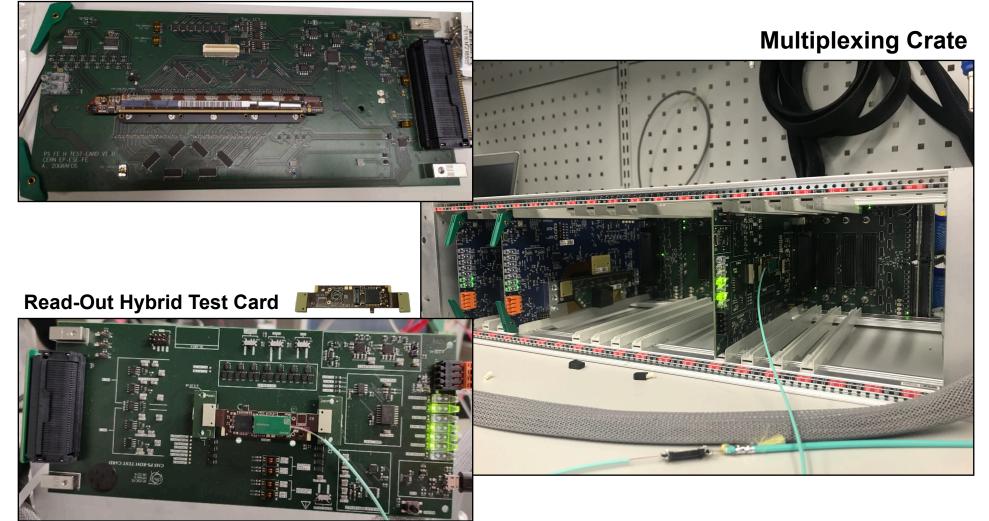

#### SSA Front-End Hybrid Test Card

Dedicated firmware block developed for MUX Crate control and electrical tests of single components

# Conclusion

#### Summary

- Introduction of new Tracker module design for the needs

of High Luminosity LHC upgrade

- Momentum discriminating design based on cluster correlation between two closely stacked Si sensor

- Data acquisition firmware developed for the needs of prototype testing and module production

- MUX crate based test system with custom test cards for single component testing of large production batches

#### Outlook

- DAQ Firmware and test systems development still ongoing

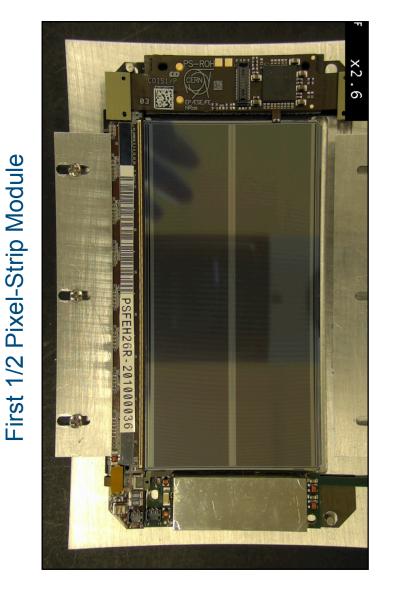

- First 1/2 PS Module soon to go for beam test

# THANK YOU.

#### Contact

**DESY.** Deutsches Elektronen-Synchrotron Younes Otarid CMS younes.otarid@cern.ch younes.otarid@desy.de

www.desy.de

# **Back-Up**

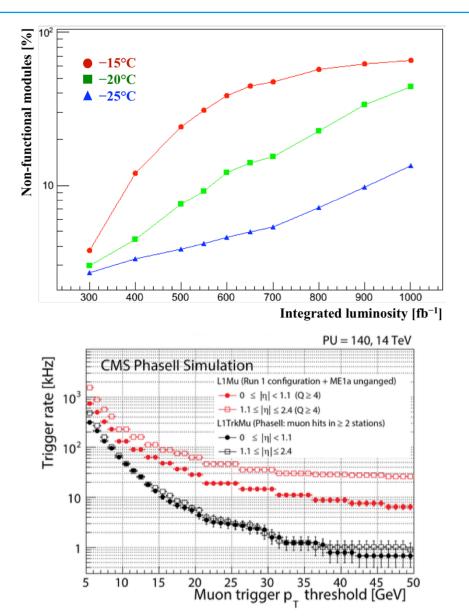

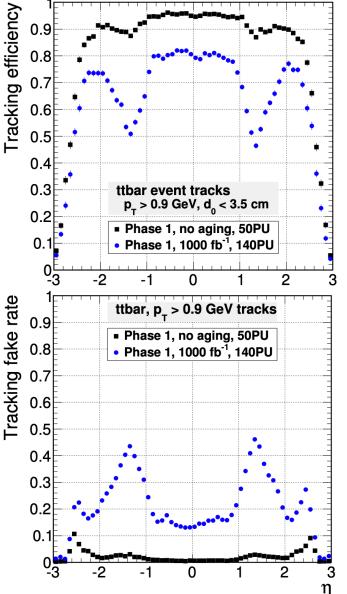

#### **Limitations of the current tracker**

#### Limitations of the current tracker

#### **Cut through the Pixel-Strip Module**

DESY.

#### **Clock Generator block**

→ REFCLK\_LOCKED

#### **Readout block data flow diagram**

DESY.

#### **MUX Crate System**

#### **PS-FEH Firmware**

#### FC7 (electrical readout)

- SC/FCMD/Data CIC\* blocks

- I2C, FCMD, Data decoder, Stub data

- Crate multiplexing block

- Selection of hybrid to be powered

- Single SSA readout

- SSA output clock testing

- Binary counters for signal rising edges

- SSA output fast command testing

- FCMD pattern/payload check

- MPA test vectors (CIC inputs)

- Configurable data player @320MHz / 640MHz

### **PS-ROH Firmware**

#### Control FC7

- Crate multiplexing block

- Selection of hybrid to be powered

- Clock testing

- Binary counters for signal rising edges

- Fast command testing :

- BRAM based test block

- I2C Slave Interface (SC) :

- 18 slaves (9 per hybrid)

- CIC test vectors

- Configurable data player @320MHz / 640MHz

#### BackEnd FC7

- IpGBT-FPGA implementation for single/multi-link

- GBT-SC (v2.0) for use of IpGBT Serial Interface

- VIO debug core