# Development and characterization of a novel high-density interconnection technology for the CBM Silicon Tracking System at FAIR

# Patrick Pfistner, Thomas Blank, Michele Caselle, for the CBM collaboration

Institute for Data Processing and Electronics

#### **Outline**

- Compressed Baryonic Matter (CBM) experiment @ FAIR

- Silicon Tracking System (STS)

- STS detector module

- High-density interconnection based on aluminum microcables and TAB

- Novel high-density interconnection technology based on Gold stud solder bump bonding

- Characterization of prototype modules in copper technology

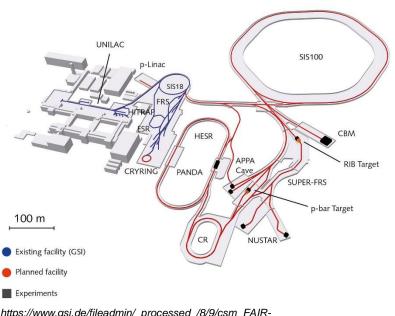

#### **CBM @ FAIR**

- CBM is one of the major scientific programs at FAIR

- Investigation of QCD phase diagram at high net-baryon densities and moderate temperatures

Image: D. Fehrenz/GSI/FAIR

Drone video of FAIR construction site: <a href="https://www.youtube.com/watch?v=8cSLI557CQk">https://www.youtube.com/watch?v=8cSLI557CQk</a>

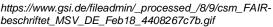

## **CBM** experimental setup

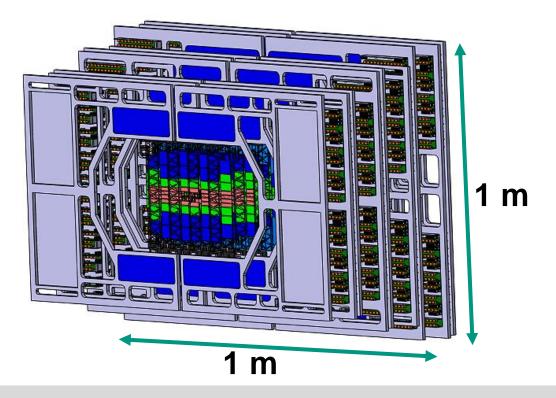

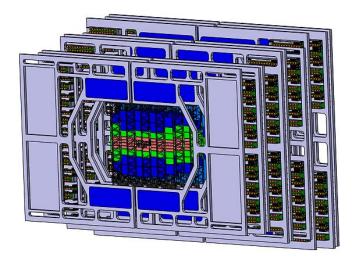

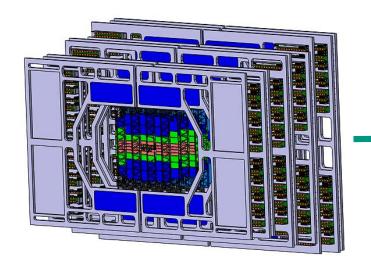

## Silicon Tracking System (STS)

- Track identification and momentum determination of charged particles

- Track mult.  $\leq$  700 per central Au+Au collision in aperture 2.5°  $< \theta <$  25°

- Lifetime fluence up to  $1 \times 10^{14} \, n_{eq} cm^{-2}$

- Momentum resolution  $\Delta p/p < 2\%$

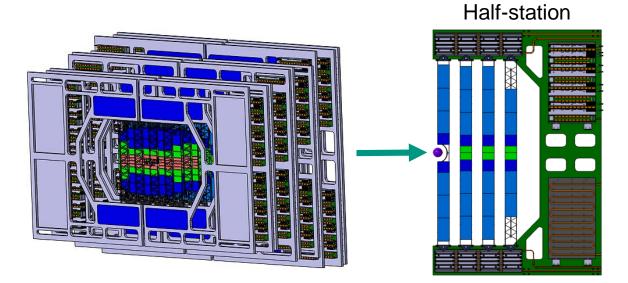

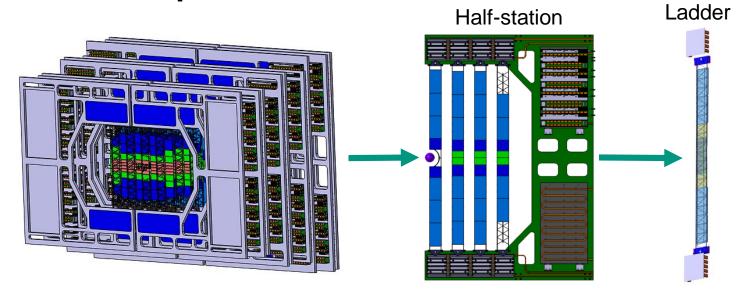

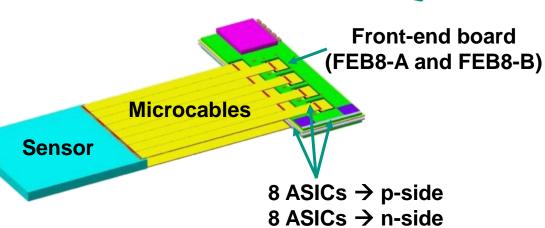

Ladder Half-station **Detector module**

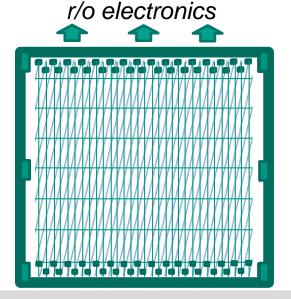

- Double-sided microstrip sensor

- Pitch: 58 µm

- 2 x 1024 channels

- 2 x 8/16 low mass microcables

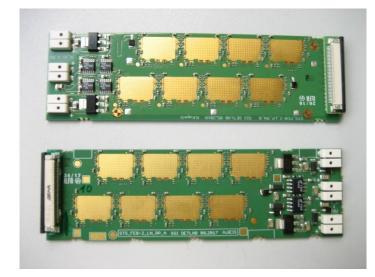

- 2 x FEB-8

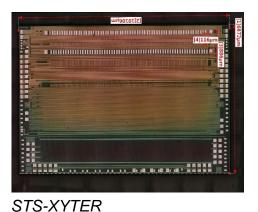

- 2 x 8 STS-XYTER ASICs

TAB interconnection

# **ALUMINUM TECHNOLOGY**

#### **Aluminum microcables**

#### **Aluminum microcable**

- 15 μm Al on 10 μm Polyimide

- Meshed PI spacer

- 64 signal lines

- Pitch: 116 μm

- Capacitance ~ 0.35 pF/cm

- $X/X_0 \sim 0.03 \%$

- 32 microcables per sensor

#### **Aluminum microcables**

#### **Aluminum microcable**

- 15 μm Al on 10 μm Polyimide

- Meshed PI spacer

- 64 signal lines

- Pitch: 116 μm

- Capacitance ~ 0.35 pF/cm

- $X/X_0 \sim 0.03 \%$

- 32 microcables per sensor

03.02.2021

#### **Aluminum microcables**

#### **Aluminum microcable**

- 15 μm Al on 10 μm Polyimide

- Meshed PI spacer

- 64 signal lines

- Pitch: 116 μm

- Capacitance ~ 0.35 pF/cm

- $X/X_0 \sim 0.03 \%$

- 32 microcables per sensor

03.02.2021

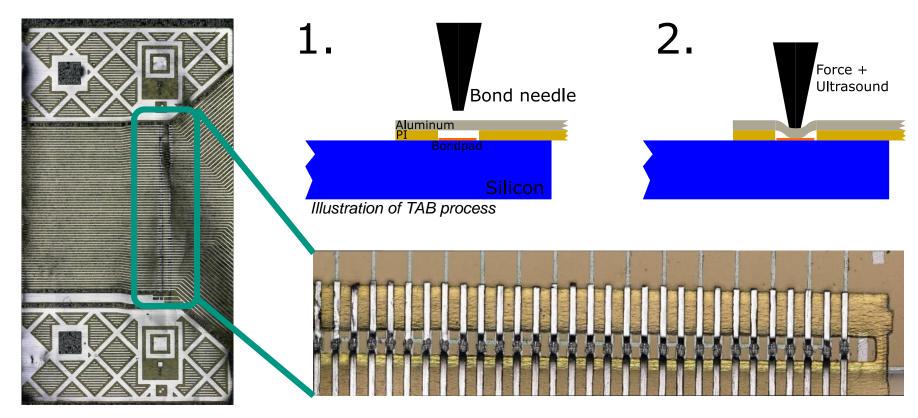

## Interconnection by TAB process

- Room temperature process

- Well-established, proven to work

- Manual and time-consuming

- Single supplier of aluminum microcables (LTU Ltd, Kharkov, Ukraine)

Gold stud – solder bump bonding

# **COPPER TECHNOLOGY**

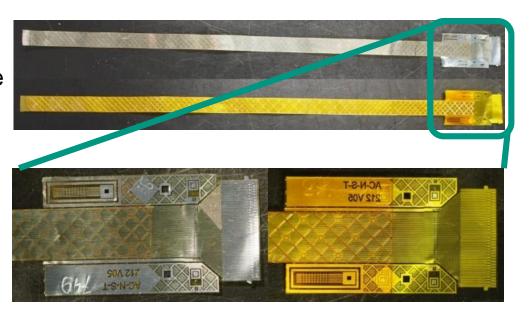

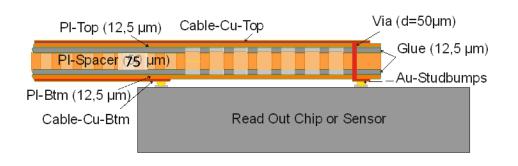

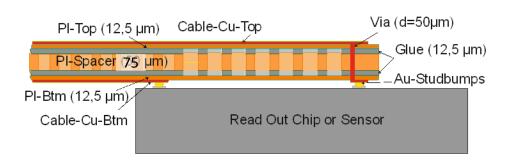

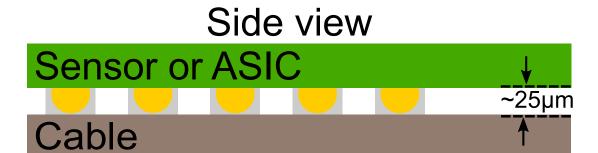

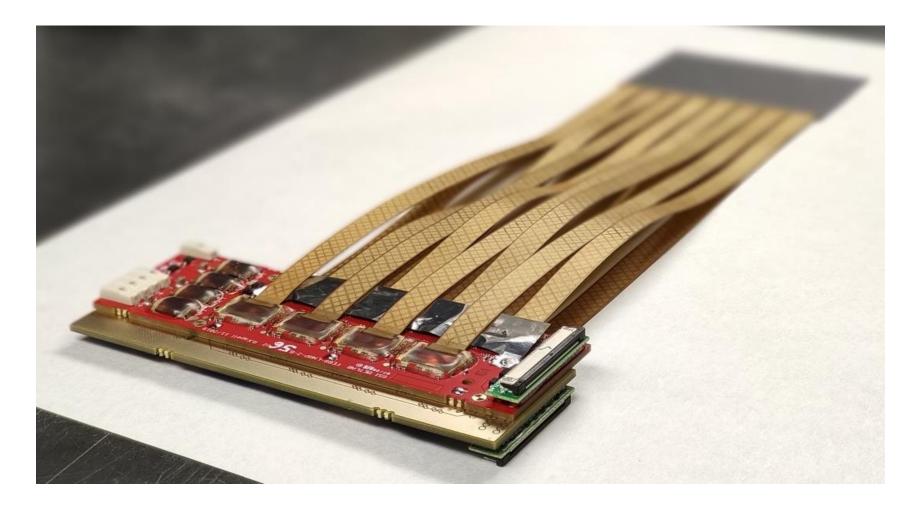

## Copper microcables for Au-solder process

- Two signal layers: 2 x 64 channels

- Bond pitch 116 μm

- Thickness 140 μm

- Capacitance ~ 0.38 pF/cm

- $X/X_0 \sim 0.05 \%$

## Copper microcables for Au-solder process

- Two signal layers: 2 x 64 channels

- Bond pitch 116 μm

- Thickness 140 μm

- Capacitance ~ 0.38 pF/cm

- $X/X_0 \sim 0.05 \%$

03.02.2021

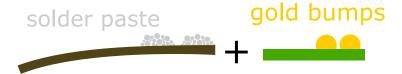

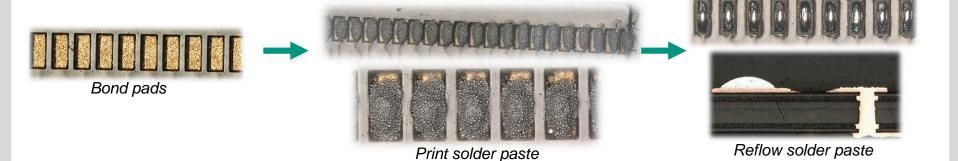

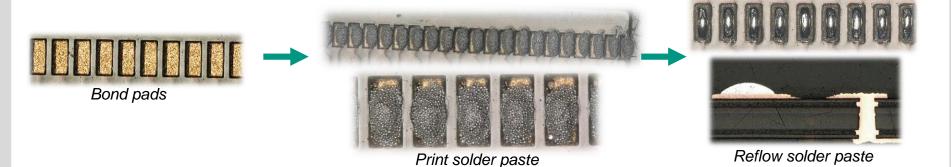

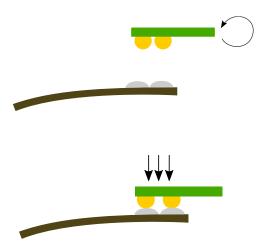

## Novel approach: Gold stud – solder process

1. cable and chip

4. flip chip

2. place bumps on chip and solder paste on cable

5. thermocompression bonding

3. reflow

6. underfill

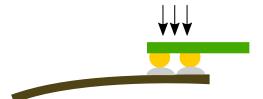

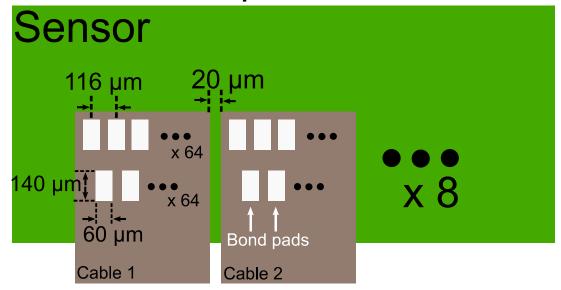

## Important dimensions

Top view

03.02.2021

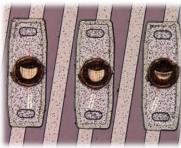

## Realization of Au stud – solder process

## Realization of Au stud – solder process

Place gold bumps

## Realization of Au stud – solder process

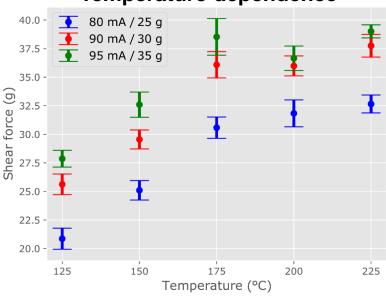

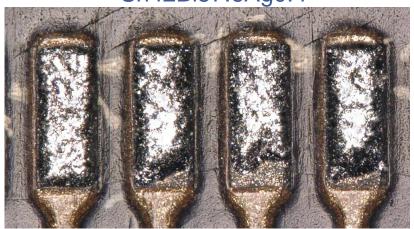

## Gold stud bumping process optimization

- Gold bumping parameter scan

- Temperature

- Bond force

- Ultrasonic current (USG)

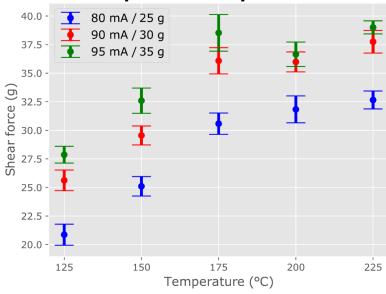

#### Temperature dependence

## Gold stud bumping process optimization

- Gold bumping parameter scan

- Temperature

- Bond force

- Ultrasonic current (USG)

#### **Temperature dependence**

#### Bond force - USG scan

## Solder paste type 7/8 printing and reflow

**Uniform solder deposition**

## Tackling the thermal mismatch

- Process temperature reduction

- Downscaling of microcable pitch

#### Solder paste type 7/8

| Alloy                     | T <sub>melt</sub> (°C) |

|---------------------------|------------------------|

| Sn96.5Ag3.0Cu0.5 (SAC305) | 217                    |

| Sn63Pb37                  | 183                    |

| Sn42Bi58                  | 138                    |

| Sn42Bi57.6Ag0.4           | 131                    |

**SAC305**

Sn42Bi57.6Ag0.4

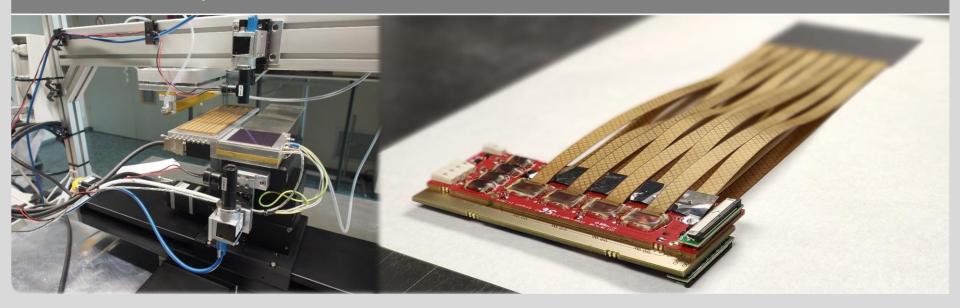

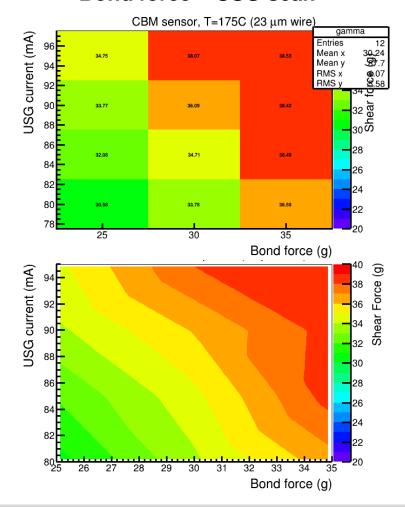

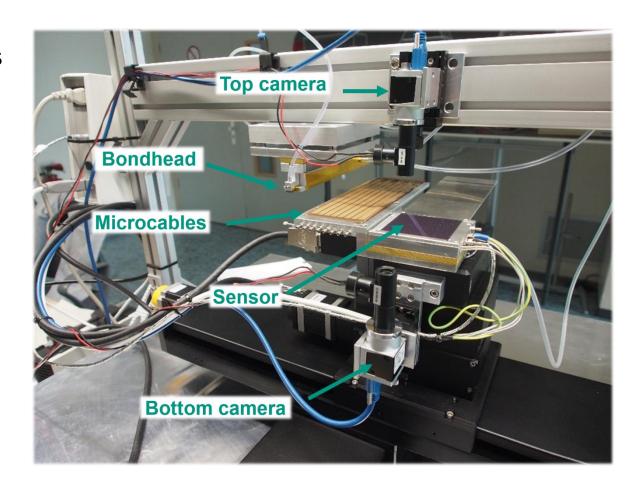

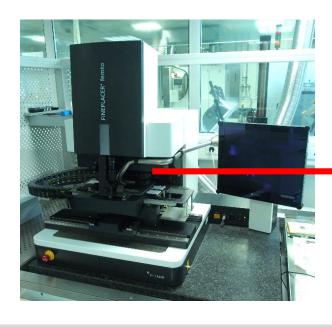

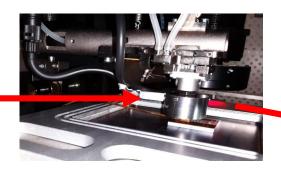

# In-house bonding machine for sensor-side interconnection

- Four stepper motors

(x,y,z,φ) with sub micron resolution

- Temperature regulated heatable bond head and sensor plate

- Dual-camera optical system

- Automated vacuum control

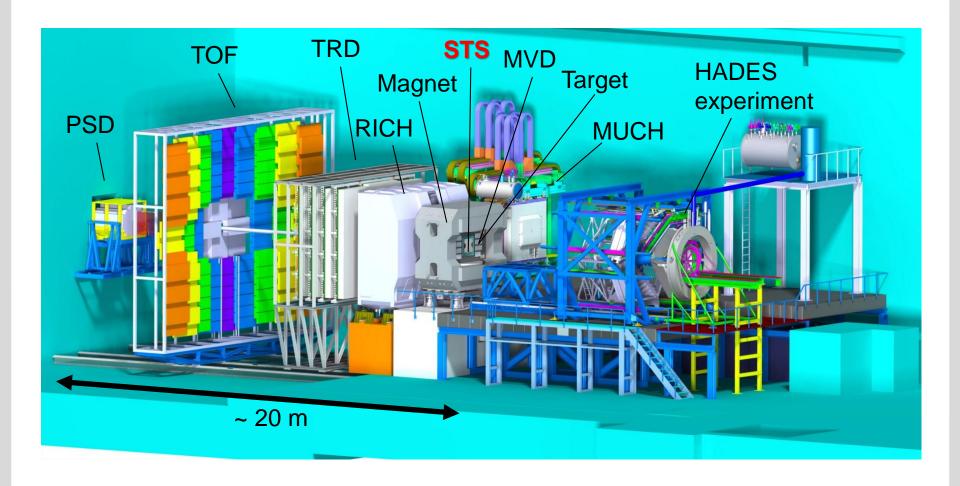

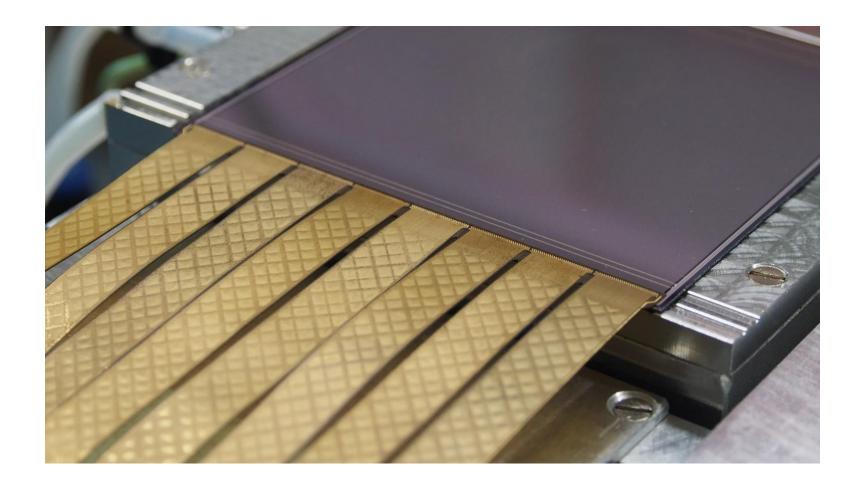

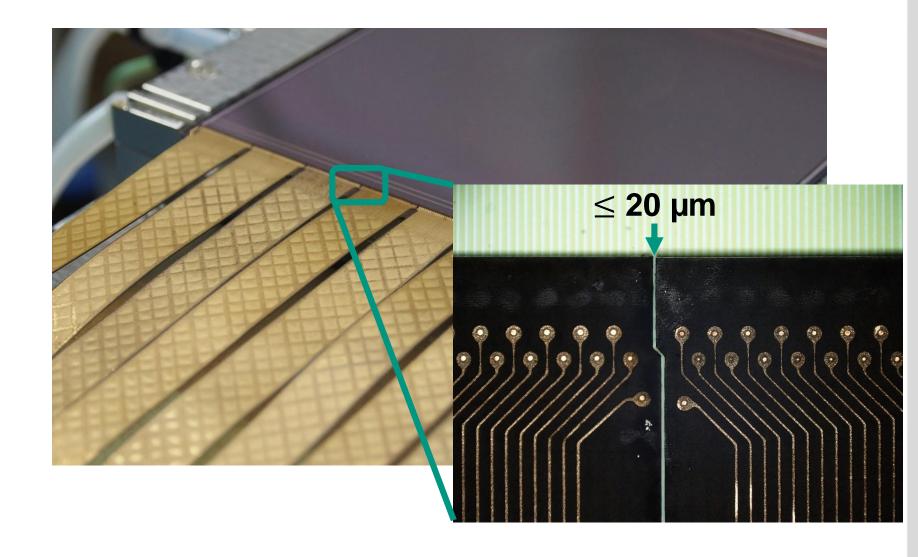

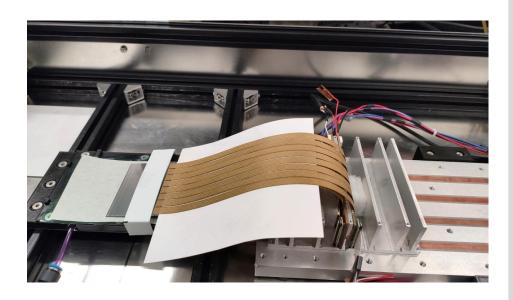

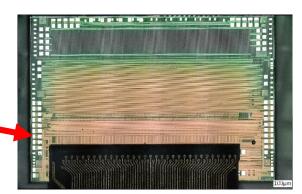

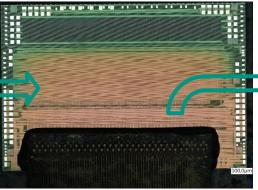

## **Complete single-sided assembly**

## **Complete single-sided assembly**

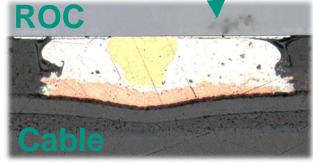

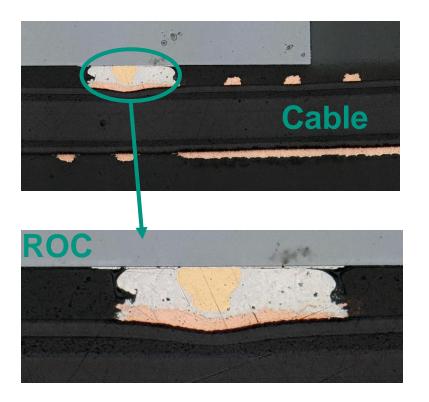

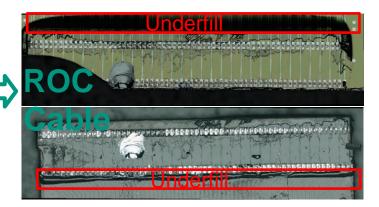

## **Quality assurance**

#### **Cross-sections**

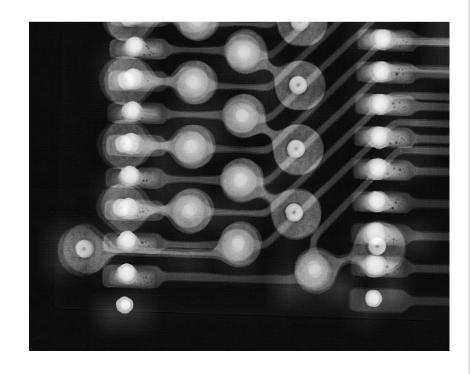

## X-ray inspection

03.02.2021

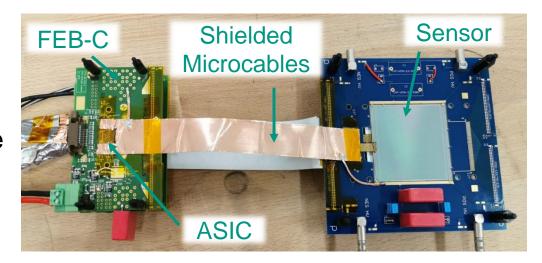

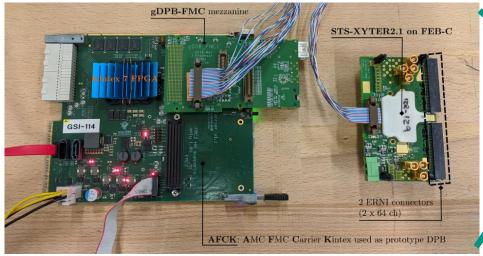

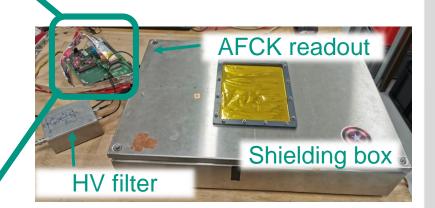

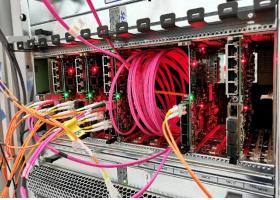

## Test setup small-scale prototypes

- Asymmetric bias at 150 V

- One microcable each on nand p-side

- 2 x FEB-C each hosting one readout ASIC

- Readout via AFCK hosting Kintex7 FPGA controlled by IPbus protocol

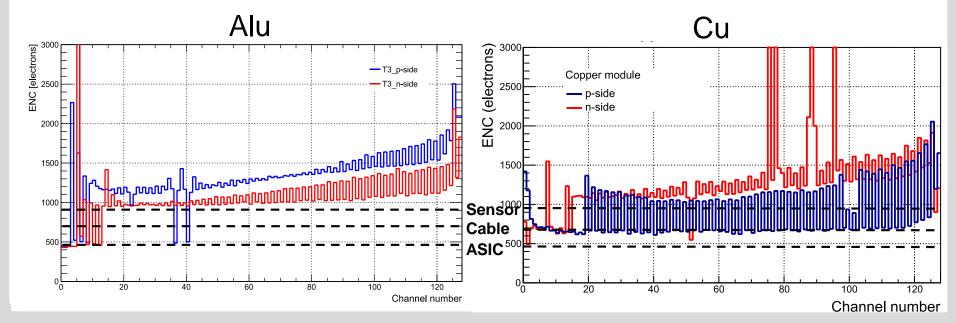

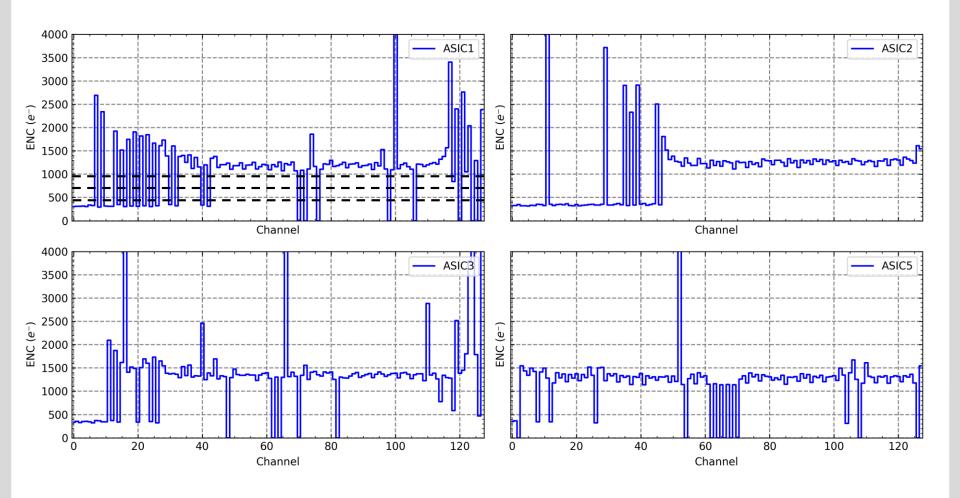

## **ENC** evaluation on prototype modules

Simple ENC parametrization based on capacitive load seen by CSA

ASIC Cable Sensor

Alu:  $460 e^{-} + \left(0.35 \frac{pF}{cm} * 25 cm + 1.52/1.74 \frac{pF}{cm} * 4.2 cm\right) * 27.4 \frac{e^{-}}{pF} = 875/900 e^{-}$ Cu:  $460 e^{-} + \left(0.38 \frac{pF}{cm} * 20 cm + 1.52/1.74 \frac{pF}{cm} * 6.2 cm\right) * 27.4 \frac{e^{-}}{pF} = 926/964 e^{-}$

## **ENC** evaluation on prototype modules

Simple ENC parametrization based on capacitive load seen by CSA

ASIC Cable Sensor

Alu:

$$460 e^{-} + \left(0.35 \frac{pF}{cm} * 25 cm + 1.52/1.74 \frac{pF}{cm} * 4.2 cm\right) * 27.4 \frac{e^{-}}{pF} = 875/900 e^{-}$$

Cu:

$$460 e^{-} + \left(0.38 \frac{pF}{cm} * 20 cm + 1.52/1.74 \frac{pF}{cm} * 6.2 cm\right) * 27.4 \frac{e^{-}}{pF} = 926/964 e^{-}$$

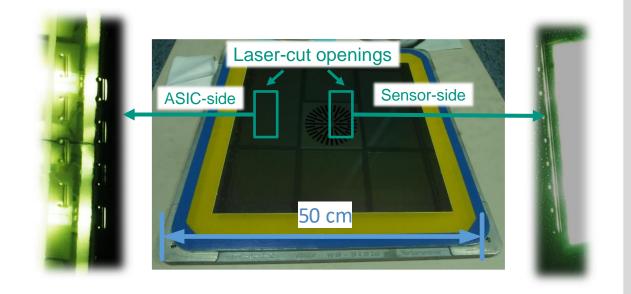

## **Full-scale prototype**

## Full-scale prototype testing

- Light-tight shielding box

- Symmetric bias ± 75 V

- Water cooling system

- Readout chain

- 1. FEB-8

- 2. C-ROB: data aggregation, electrical to optical interface

- 3. Data Processing Board (DPB) based on AFCK

**C-ROB**

DPB in µTCA

# ENC full-scale prototype: ASICs 1,2,3,5 n-side

## Challenges

- Double-layered fine-pitch flex technology on the edge of manufacturing capabilities (yield, cost)

- High demands on precision solder printing

- High demands on planarity between die and cable

- Copper microcable stiffness complicates assembly

- Thermal mismatch due to need for elevated process temperature

- Slightly higher capacitance and material budget compared to aluminum cables

## **Summary**

- A double-layered (2x64 channels) fine-pitch copper cable was developed and characterized

- Capacitance: 0.38 pF/cm (Alu: 0.35 pF/cm)

- Material budget:  $X/X_0 = 0.05\%$  (Alu: 0.03%)

- A novel high-density interconnection technology has been established

- Gold stud bumping on the die combined with precision solder printing on the cable assembled in a flip-chip process

- High degree of automization achievable

- Prototype modules show electronic performance comparable to established aluminum TAB modules

# Thank you for your attention!

## **BACKUP**

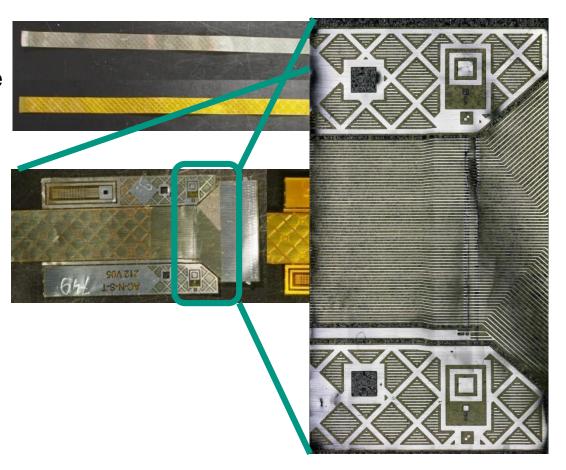

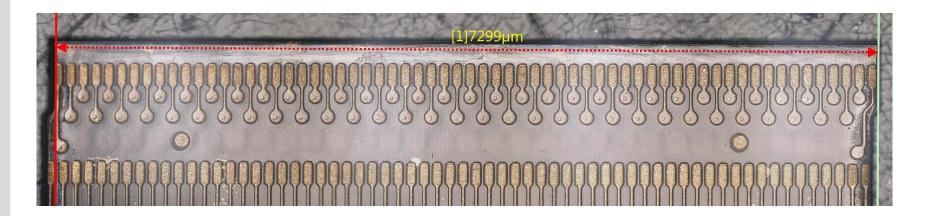

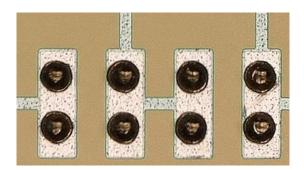

## ASIC and sensor: Gold stud bumping

Karlsruhe Institute of Technology

- Iconn ball wire bonder

- 20 bumps/s

- STS parameters

- 23 μm Au wire

- Bump diameter 55 μm

- Bump height: 30 μm

Fast, flexible, reliable

## Solder paste type 7/8 printing and reflow

#### **ASIC** – microcable interconnection

- Fineplacer femto flip chip machine with 0.5 μm alignment accuracy

- Thermocompression bonding process

- F = 40 N

- T = 230 °C

# Karlsruhe Institute of Technology

## **Underfill application**

Improves mechanical strength to survive CBM lifetime of 10 years

- Spark protection between LV microcable and HV sensor edge

- Gap height ~ 25 μm, obstructions by gold bumps

- Polytec EP601-LV ()

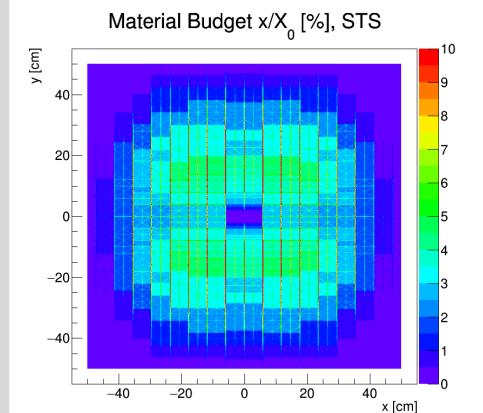

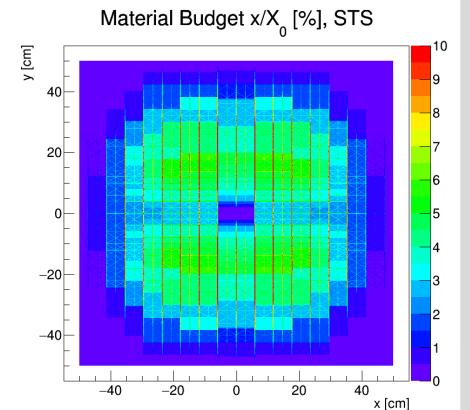

## **STS** material budget simulations

#### **Aluminum microcables**

#### **Copper microcables**

## Module components

Low mass microcables with varying length. Top: single cable. Bottom: sheet of 8 cables.

FEB-8 for p- and n-side

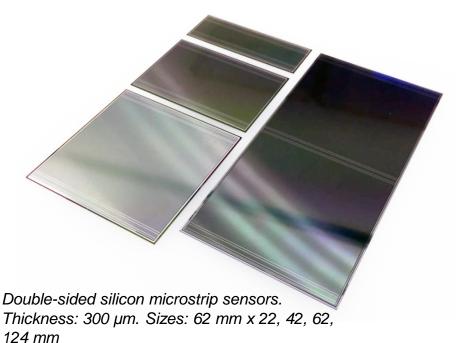

## Silicon microstrip sensors

- $285/320 \pm 15 \mu m$  thick

- · n-type silicon

- · double-sided segmentation

- 1024 strips of 58 µm pitch

- strip length 2/4/6/12 cm

- angle front/back: 7.5/0 deg

- n-side strip insulation: modulated p-spray

- read-out from top edge

- · double-metal routing on p-side

- rad. tol. up to 10<sup>14</sup> n<sub>eq</sub>/cm<sup>2</sup>

- rad tol. w.r.t. TID?

# n-side 0 p-side