# **Development of the ATLAS Liquid Argon Calorimeter Read-out Electronics for the HL-LHC**

## Sana Ketabchi

## On behalf of the ATLAS Liquid Argon Group EPS-HEP, 27 July 2021

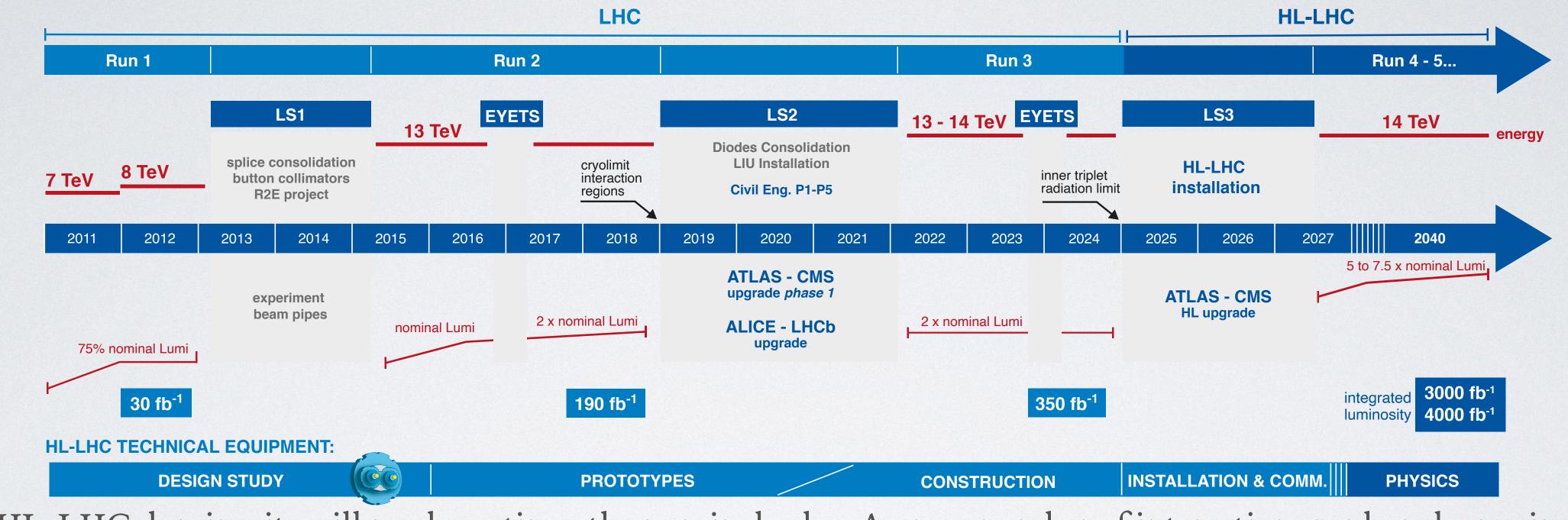

## LHC / HL-LHC Plan

- During HL-LHC, luminosity will reach 5-7 times the nomin up to 200.

- ATLAS LAr calorimeters electronic read-out system will be u during LS2. Physical detector will remain unchanged.

- The LAr upgrade aims to provide the necessary radiation hard trigger read-out system.

Sana Ketabchi

# High-Luminosity LHC

During HL-LHC, luminosity will reach 5-7 times the nominal value. Average number of interactions per bunch crossing can reach

ATLAS LAr calorimeters electronic read-out system will be upgraded during LS3. Trigger read-out is being upgraded currently

The LAr upgrade aims to provide the necessary radiation hardness and make the read-out chain compatible with future ATLAS

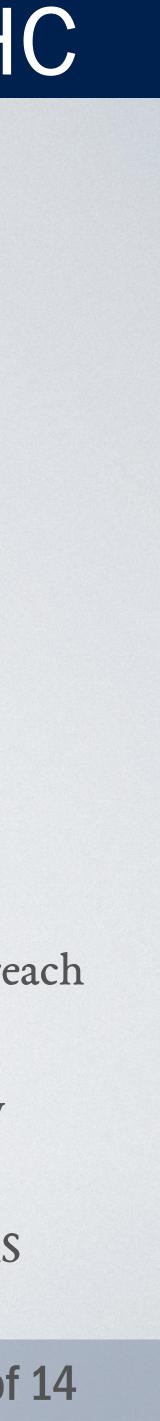

# ATLAS Liquid Argon (LAr) Calorimeter

Trigger read-out path is currently being upgraded during LS2 and will remain operational during HL-LHC.

Sana Ketabchi

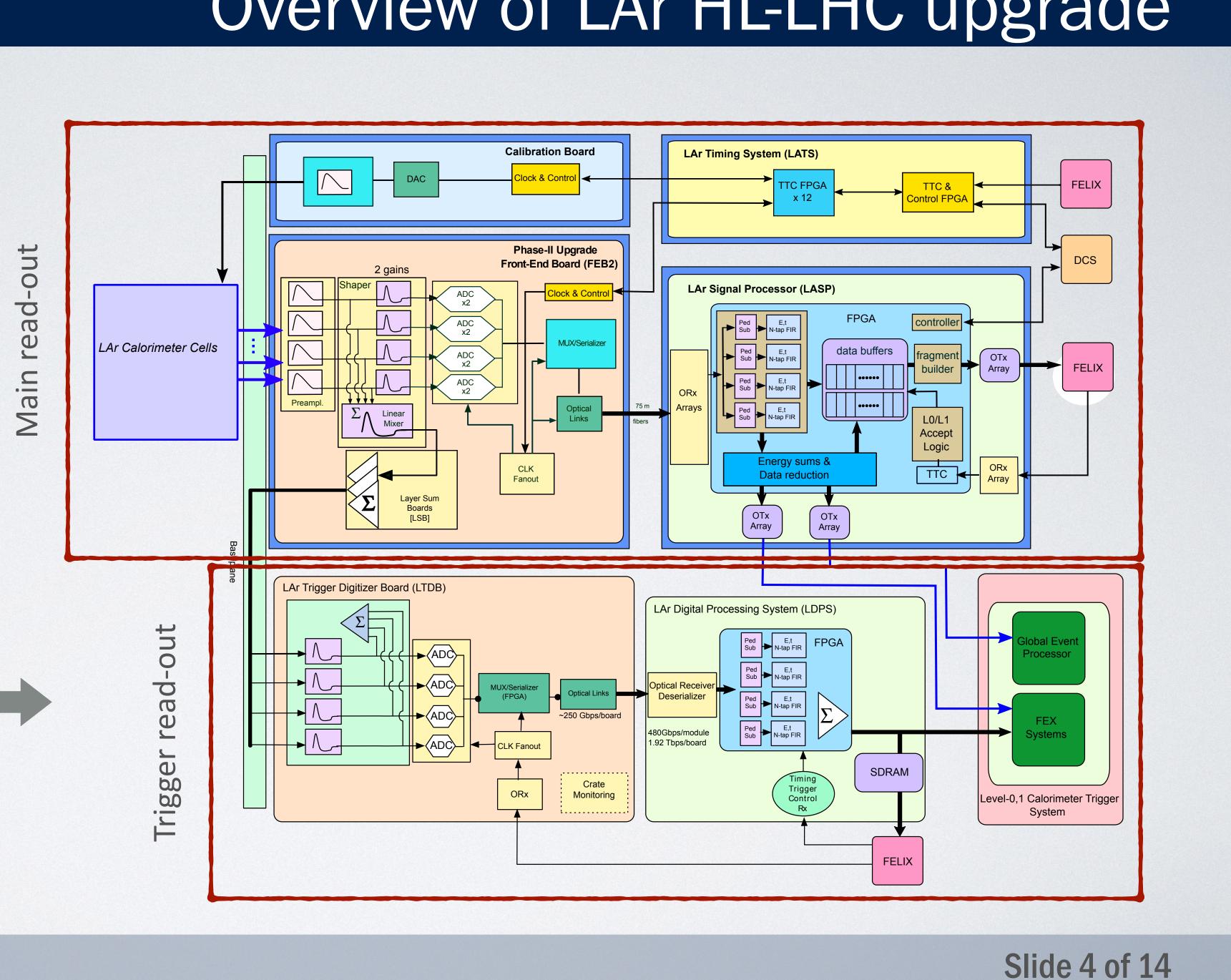

# Overview of LAr HL-LHC upgrade

Main read-out will be updated during LS<sub>3</sub>.

read-out

Main

LAr Calorimeter Cells

Sana Ketabchi

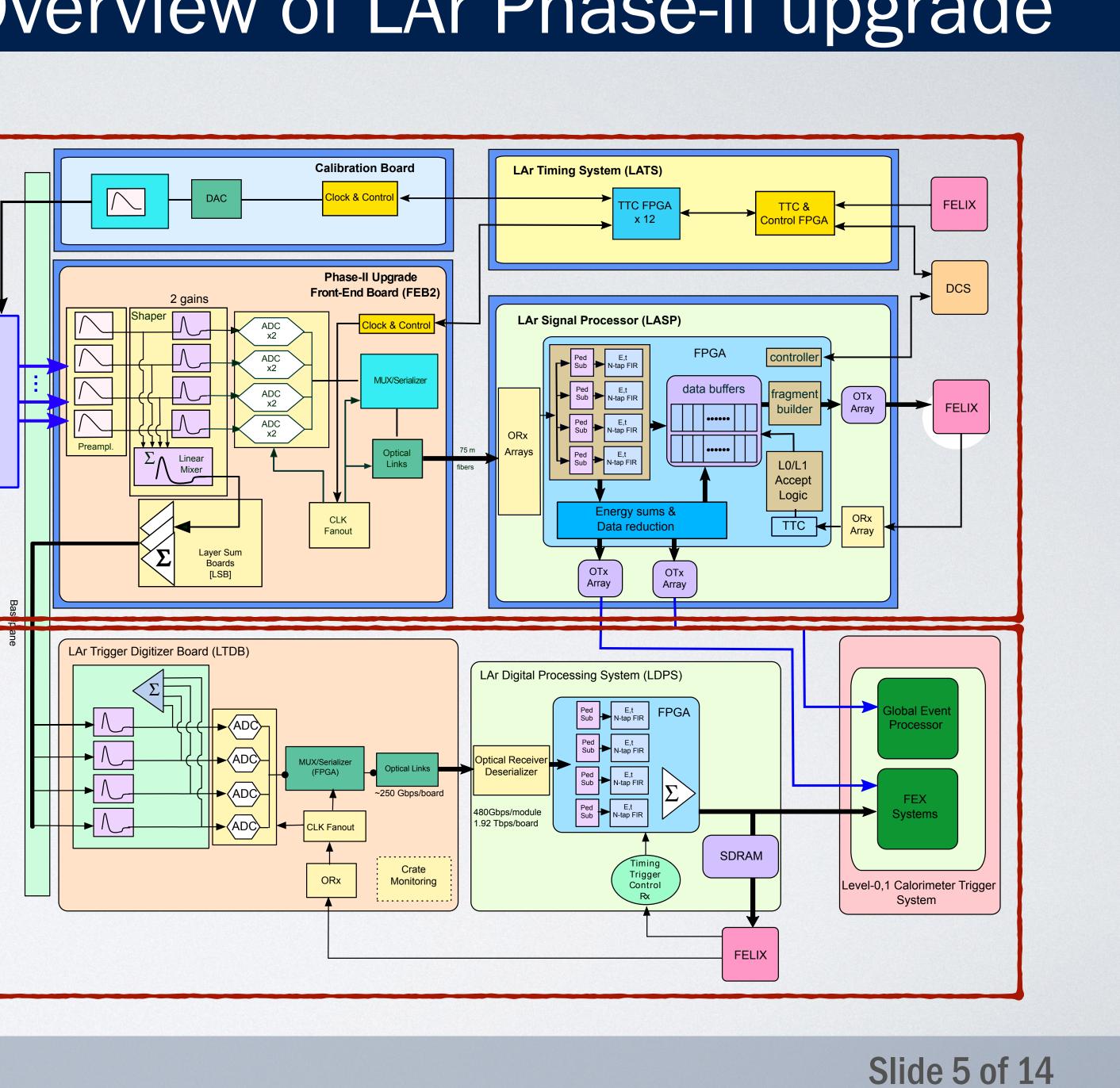

## Overview of LAr Phase-II upgrade

Main read-out will be updated during LS3.

Free-running scheme: All analog signals will be digitized and sent off-detector at 40 MHz.

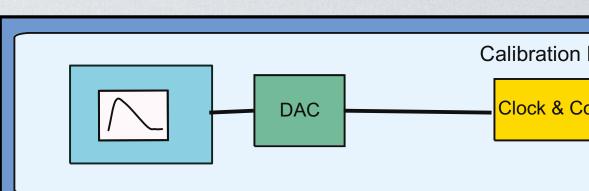

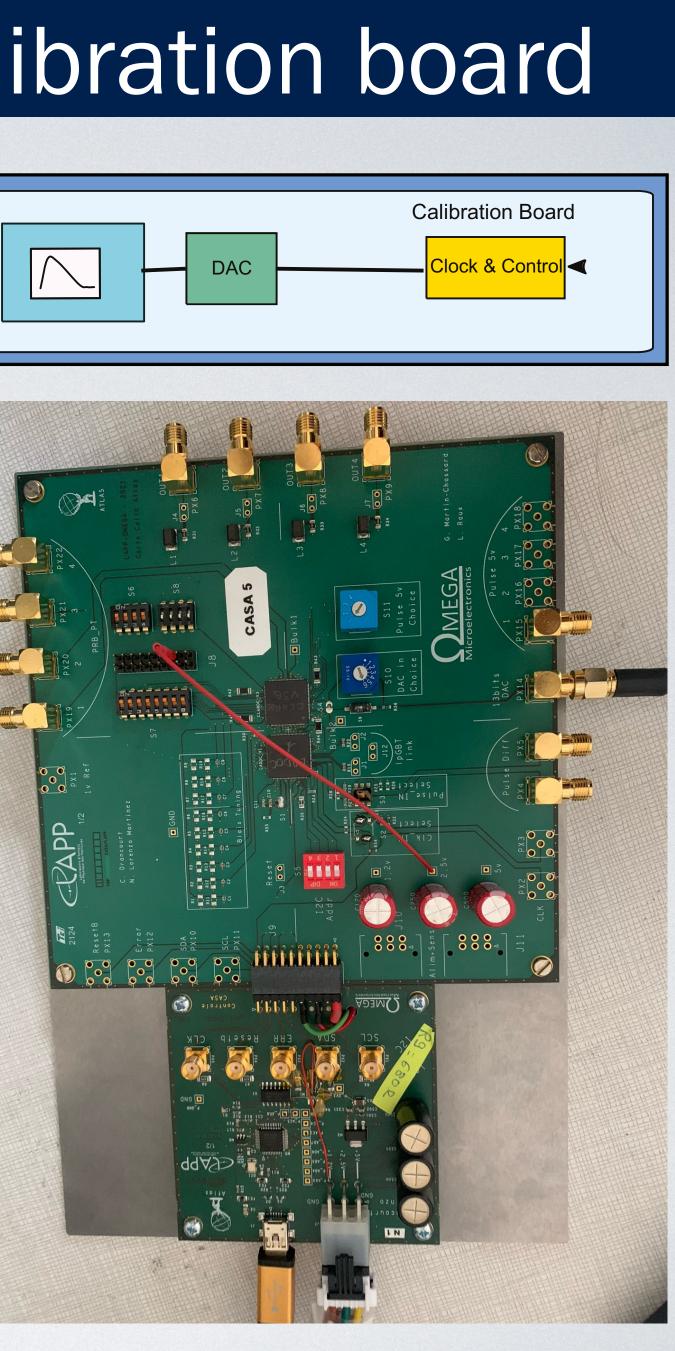

- Injects signals similar to ionization pulses directly into calorimeter cells for calibration of read-out electronics

- **Requirements:**

- Integral non-linearity < 0.1%, pulse rise time < 1 ns, 16-bit dynamic range and • radiation tolerance of 1.8 kGy

- **CLAROCv3 + LADOCv1:**

- CLAROCv3: Integrated ASIC, HV-CMOS (XFAB 180 NM), 4 high frequency (HF) switches to pulse up to 4 calibration channels

- LADOCVI: TSMC DAC chip & I2C •

- CASA test board: to test CLAROCv3 + • LADOC

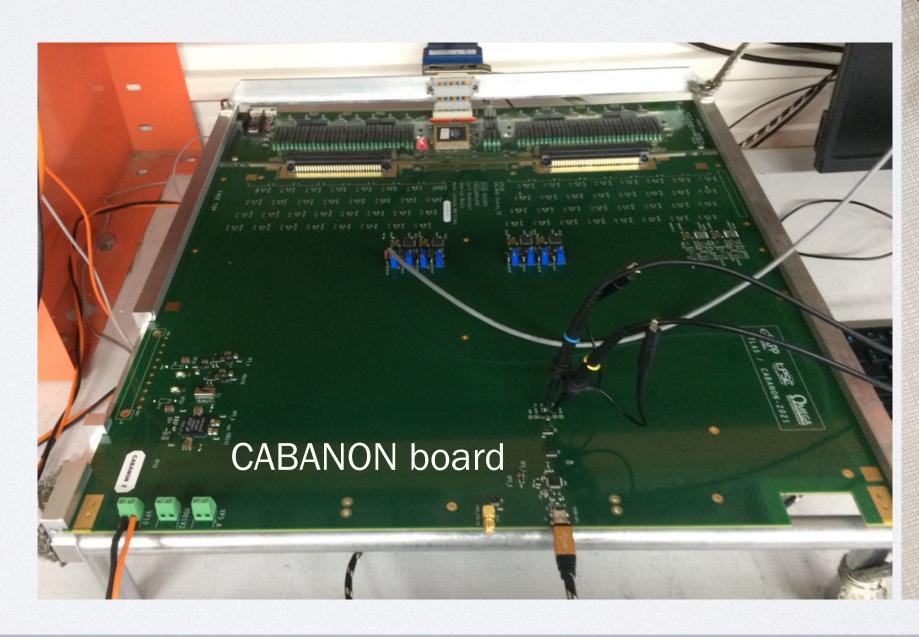

- 32 channel (8 ASIC) calibration prototype board (CABANON) is produced and is currently undergoing various tests.

## Calibration board

## Slide 7 of 14

- Performs amplification and bipolar shaping of calorimeter signals

- Both preamplifier and shaper implemented on same chip

- **Requirements:**

- Summing 4 channel signals with linearity < 0.2%, CR-RC<sup>2</sup> shaping, low and high gain output for each channel with ratio~23, radiation tolerance up to 1.8 kGy

- Two ASICs, ALFE and LAUROC, were developed and evaluated. The former was selected based on its lower noise levels.

- ALFE: 130 nm TSMC CMOS

- Differential outputs to ADC

- vi satisfies irradiation requirements and analog specifications

- For HEC, polarity of amplified signals is inverted.  $\rightarrow$  HEC-specific preshaper ASIC to correct for inverted polarity: HPS

- Design based on existing preshaper+ALFE/LAUROC

|                            | Specificat                                            |

|----------------------------|-------------------------------------------------------|

| Input Impedance            | 25 Ω / 50 Ω ± 5%                                      |

| Input impedance tol.       | ± 5% up to 20 MHz                                     |

| Input current range        | 10 mA / 2 mA                                          |

| Output range               | 0.1 – 1.1 V                                           |

| Output P DC LVL            | 300 mV ±150 mV                                        |

| Output N DC LVL            | 900 mV ±150 mV                                        |

| Shaping                    | CR-RC <sup>2</sup>                                    |

| High Gain / Low Gain ratio | 22 tol. ±5                                            |

| Peaking times              | 45 ns / 40 ns ±5 ns $\tau$ steps                      |

| INL HG                     | ±0.2 %                                                |

| INL LG                     | ±0.5 % / ±5%                                          |

| ENI HG                     | < 350 nA <sup>@50 ns</sup> / < 120 nA <sup>@4</sup>   |

| ХТК                        | < 0.5% <sup>HG-HG</sup> , < 0.5% <sup>LG-LG</sup> , < |

| PSR CH                     | 10+ dB below 1 MHz                                    |

| Output load                | 20 pF (10 pF)*                                        |

| Total Power Consumption    | < 650 mW                                              |

### Sana Ketabchi

## Slide 8 of 14

# Pulse Linearify alog-to-digital convertor

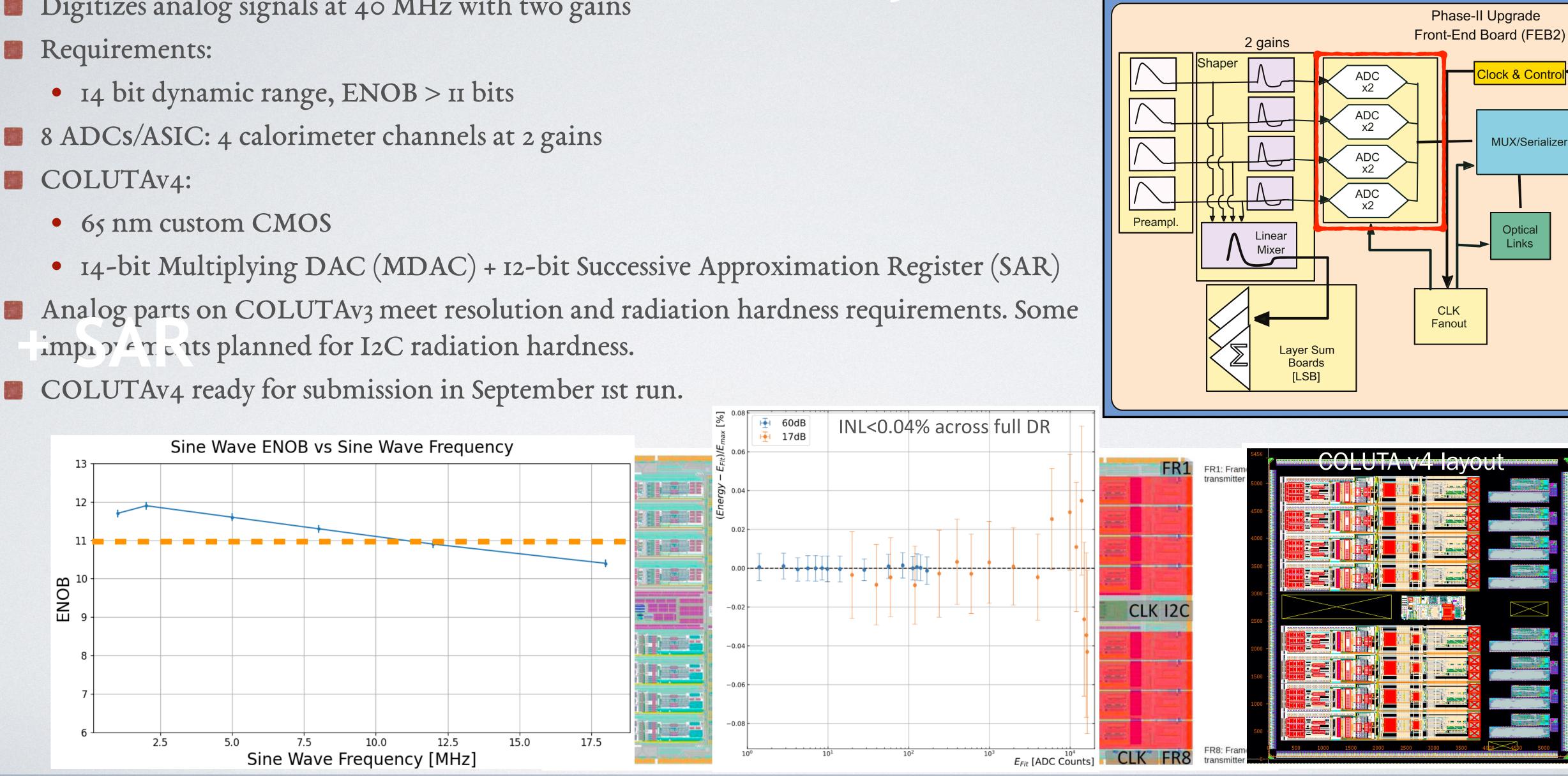

- Digitizes analog signals at 40 MHz with two gains

- **Requirements:**

- **8** ADCs/ASIC: 4 calorimeter channels at 2 gains

- **COLUTAv4:**

- improvent ents planned for I2C radiation hardness.

- COLUTAv4 ready for submission in September 1st run.

Sana Ketabchi

### Slide 9 of 14

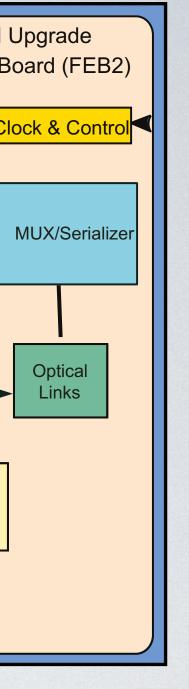

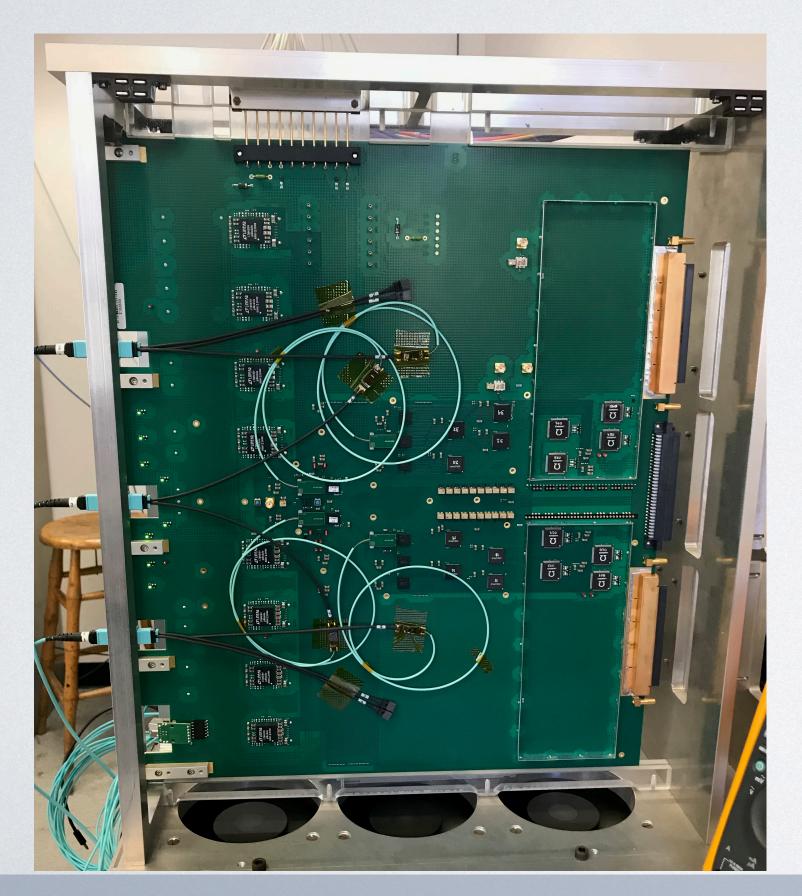

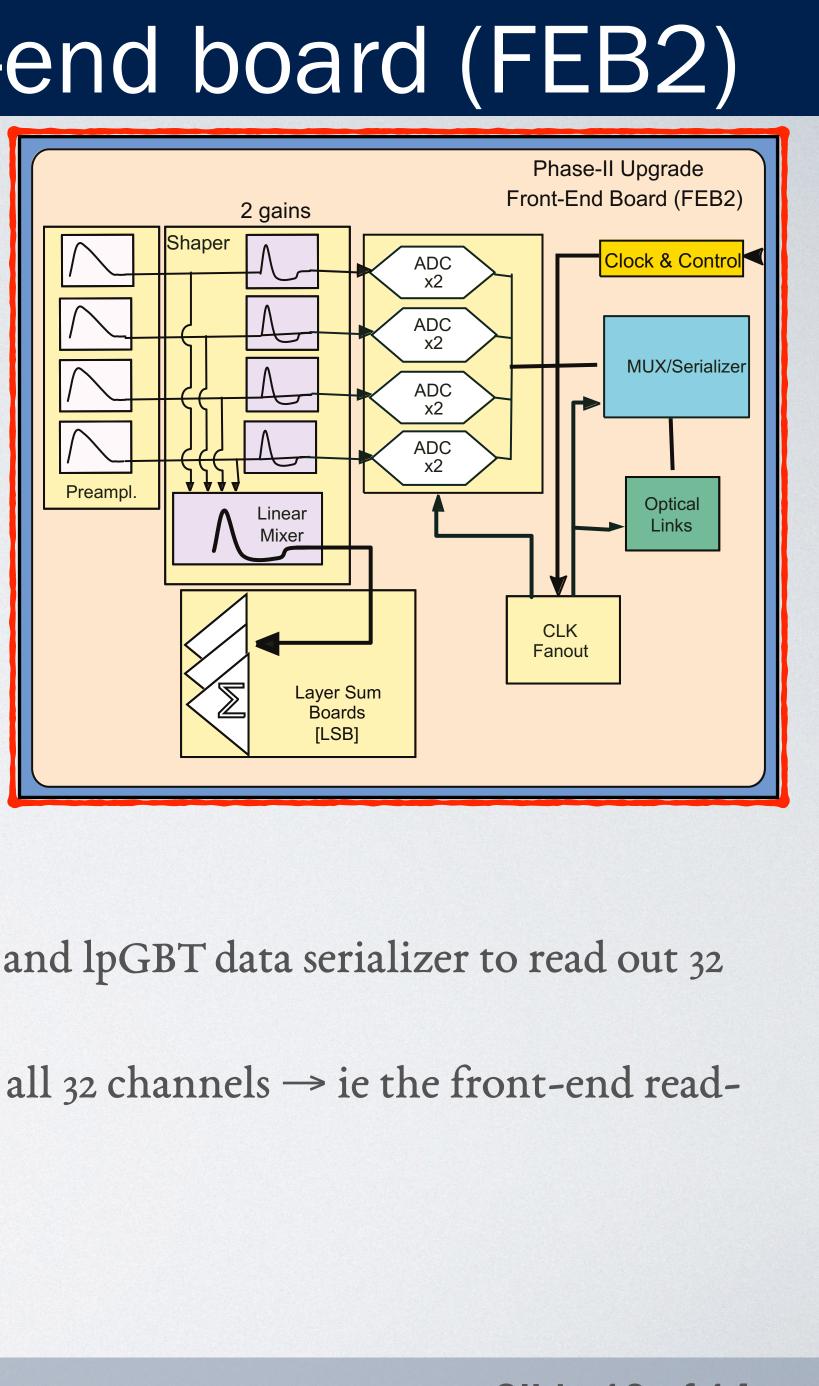

- Integrate several custom components and ultimately read-out 128 calorimeter cells per board

- Provide clock distribution and control, configuration and monitoring functions

- Also including Layer Sum Boards

Slice test board:

- Goal: to demonstrate multi-channel performance, bi-directional control links and radiation tolerant power

- Integrate pre-prototype PA/shaper, ADC and lpGBT data serializer to read out 32 channel signals

- Able to successfully read out signals from all 32 channels  $\rightarrow$  ie the front-end read-• out chain is functional

- Control and read-out links are validated

### Sana Ketabchi

## Front-end board (FEB2)

## Slide 10 of 14

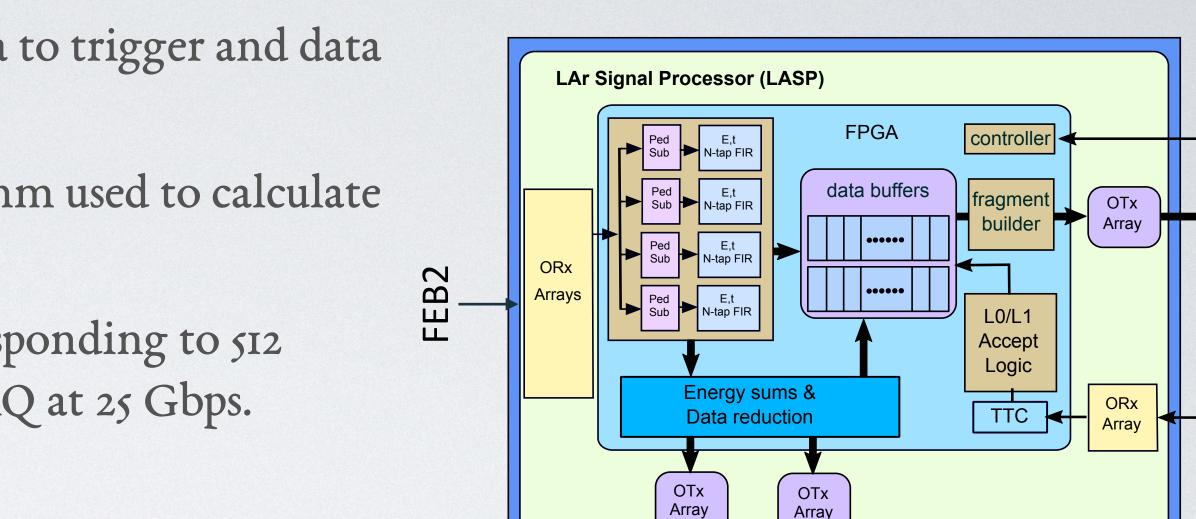

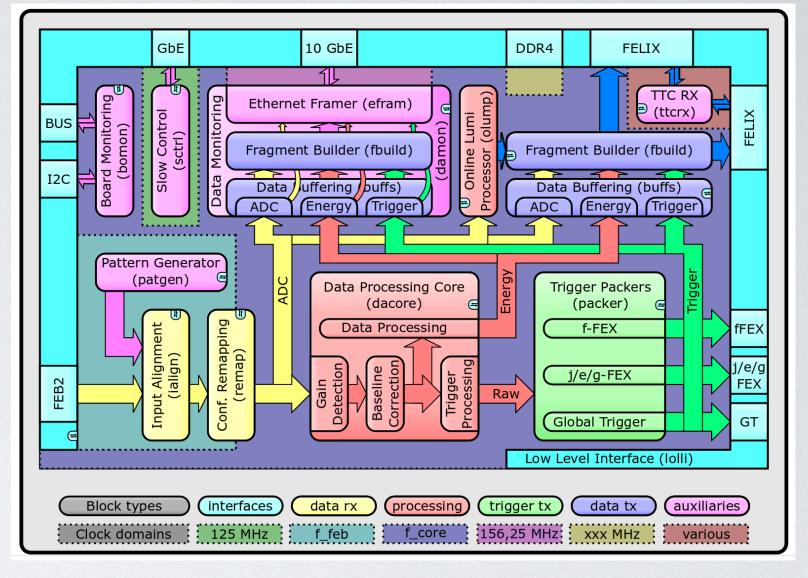

- Digital signal processing, buffering and transmitting data to trigger and data acquisition (TDAQ)

- Includes gain selection and application of the algorithm used to calculate • signal energy and deposition time

- Each FPGA (Stratix 10) handles input from 4 FEBs (corresponding to 512 calorimeter channels). Output from FPGA is sent to TDAQ at 25 Gbps.

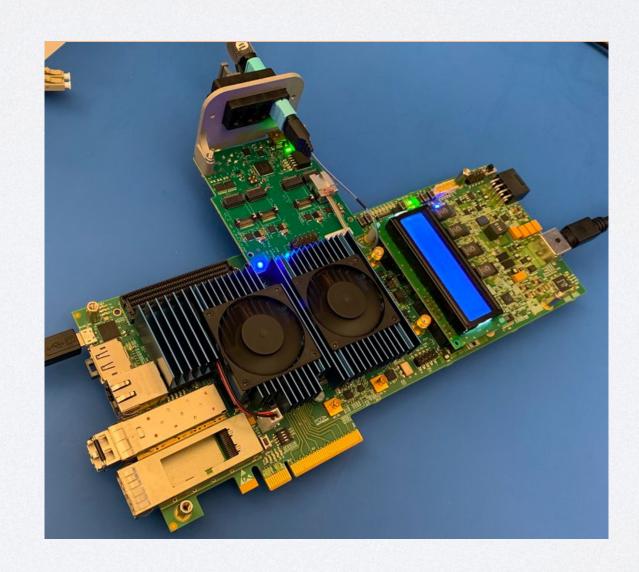

- LASP test board:

- Includes two processing FPGAs (Stratix-10), one control FPGA (MAX10) and 12 FireFly transceiver modules

- Test board with interposers in place of FPGAs is tested and all functions are confirmed as operational.

- Test board with FPGAs to be produced soon.

# LAr Signal Processor (LASP)

## **Slide 11 of 14**

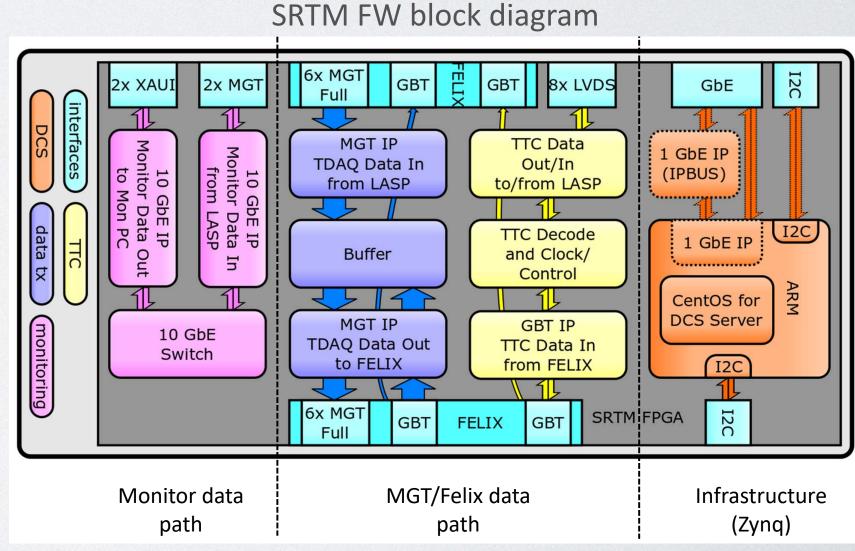

- Alongside the LASP board is a smart RTM (SRTM) which helps with monitoring and provides electro-optics

- First test board is available and system infrastructure functionality is validated.

- LASP and SRTM firmware (FW) development is ongoing.

- There are ongoing studies concerning implementation of ANNs on FPGAs for energy reconstruction (to replace the previously used optimal filtering algorithm).

- Simulations have yielded promising results.

Mezzanine board for Intel devkit are produced to create a "LASP slice".

• Setup including LASP and FEB slices is to be tested soon.

| Institutes                        | Slow cards ordered | Fast cards ordered | Card sent in March | Remaining cards to send |

|-----------------------------------|--------------------|--------------------|--------------------|-------------------------|

| IcGill University                 | 4                  | 0                  | 1                  | 3                       |

| esden University<br>of Technology | 1                  | 1                  | 1 (slow)           | 1 (fast)                |

| A Paris - Saclay                  | 1                  | 0                  | 1                  | 0                       |

| TORIA University                  | 1                  | 0                  | 1                  | 0                       |

### Sana Ketabchi

# LAr Signal Processor (LASP)

### LASP FW block diagram

**Slide 12 of 14**

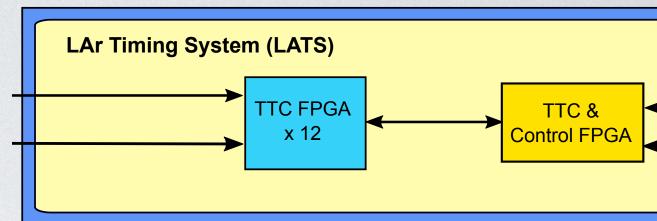

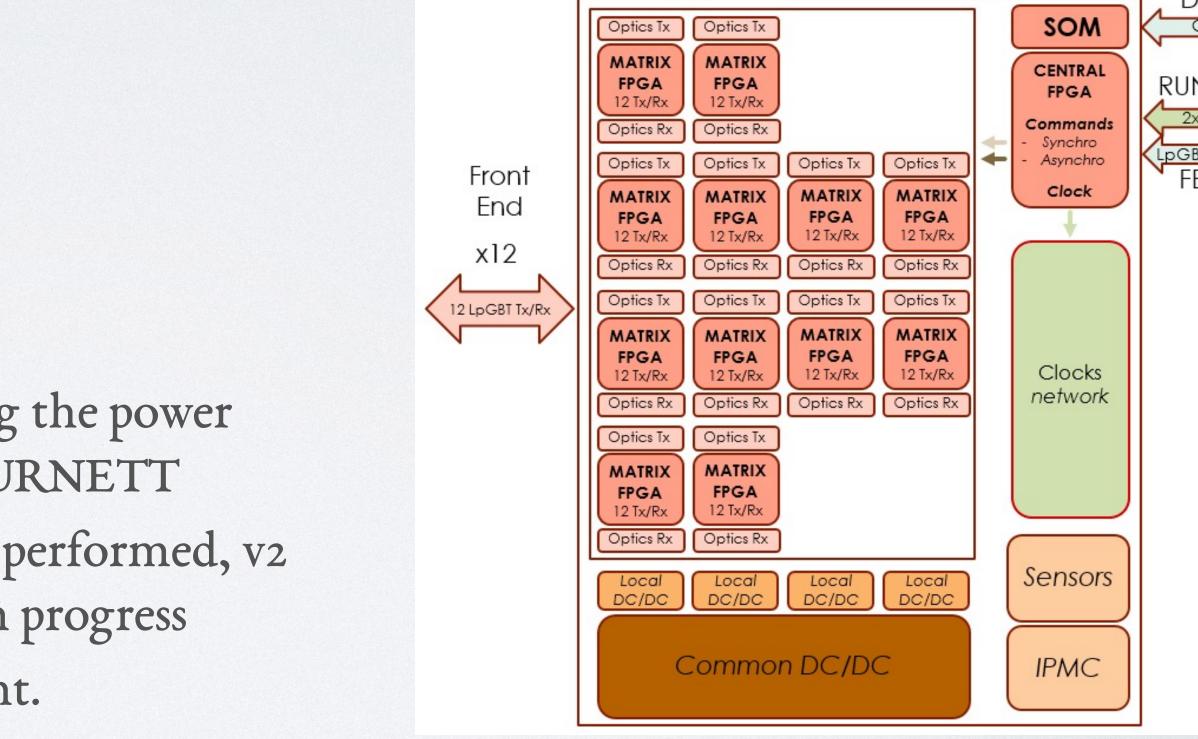

- Distribution of TTC signals and configuration and monitoring of FEB2 and calibration boards

- Dedicated clock and control distribution implementation on ATCA blade

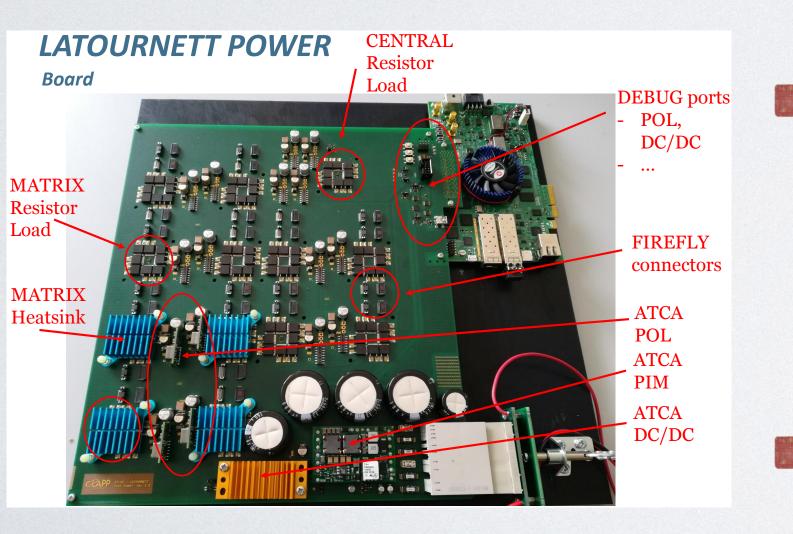

- **LATOURNETT** design:

- Central FPGA connected to TDAQ

- Matrix FPGAs connected to front-end

- System on module embedding OPCUA

- IPMC for reading critical sensors

Power board:

- Board imitating the power tree on LATOURNETT

- Initial tests are performed, v2 development in progress

- **FW** in development.

### Sana Ketabchi

# LAr Timing System

### **Slide 13 of 14**

- ATLAS LAr calorimeter will be upgraded for the HL-LHC to accommodate high expected radiation levels and to be compatible with the future trigger read-out.

- This involves development and extensive testing of custom electronic components.

- All custom ASICs are at prototype stage.

- We have started integrating and testing different components of the new read-out system.

- Integration tests have been successful so far.

- On track for timely installation during LS3

## Summary

# Questions/Comments/Concerns?

Sana Ketabchi