# Planned LLRF upgrades

F. Ludwig / T. Jezynski for the LLRF - Team

### **Outline**

FIL

- Motivation

- Consequences from FLASH operation

- Transition to uTCA hardware platform

- Planned LLRF upgrades

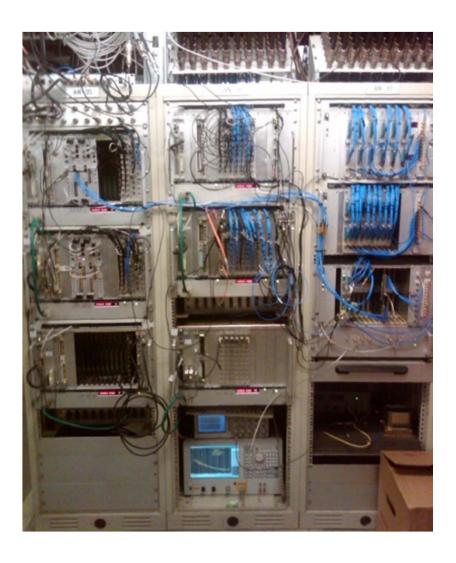

### FLASHs LLRF system at 2010

FIL

#### Upgrade of all injector RF stations

- Actuator and input power chain upgraded

- New cabling for RF-Gun, ACC1, ACC39

- Enclosed racks for better temperature stability

- Parallel cabling for development system

- Careful noise investigation, documentation

Energy stability improved by a factor of 3 to dE/E=0.5E-4.

We're done?...

## **Motivation: Robust long-term operation**

FIL

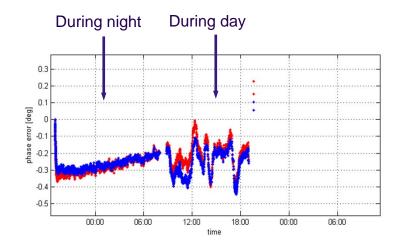

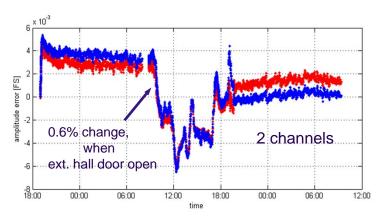

#### ACC456 Ext. Hall 3:

## **Motivation: Single cavity resolution**

FIL

| L | .LR | F pe | erfo | rma | nce | i |

|---|-----|------|------|-----|-----|---|

|---|-----|------|------|-----|-----|---|

#### Current system Testsystems

| Status of the Performance Evaluation: [10min, 1MHz]          | Switched-modulation (existing at FLASH) | CW modulation (non-IQ-sampling) | Direct-sampling    |

|--------------------------------------------------------------|-----------------------------------------|---------------------------------|--------------------|

| Self test using the reference in Laboratory (Single channel, | 0.015% (11/2008) <sup>3</sup>           | . 0.003% (2007)¹                | to be done         |

| Beam based in FLASH using SR-4BC2                            | 0.016% (11/2008) <sup>3</sup>           | 0.022% (10/2007) <sup>2</sup>   | to be done         |

| 2 DUT in FLASH using cavity probe splitting                  | 0.0065% (VS) <sup>3</sup>               | ' ?                             | to be cone         |

| Self test using the reference in FLASH (Single channel,      | 0.0068%<br>(8 channels) <sup>3</sup>    | 0.016% (11/2007) <sup>2</sup>   | 0.022% (09/2008) 4 |

| Long-term operation at FLASH                                 | YES                                     | YES (ACC39)                     | No                 |

| Calibration scheme tested in laboratory / FLASH              | YES (ACC1)                              | to be done                      | Reference tracking |

Confguration: 1: Passive Receiver, 16-bit ADC ACB 2.1,

2: Active Receiver, 14-bit ADC SIMCON 3.1

3: Active Receiver, 14-bit ADC SIMCON Boards, 4: 12-bit ADC, 200Msps

- → We benefit from cavity channel scaling in vector sum by about sqrt(8).

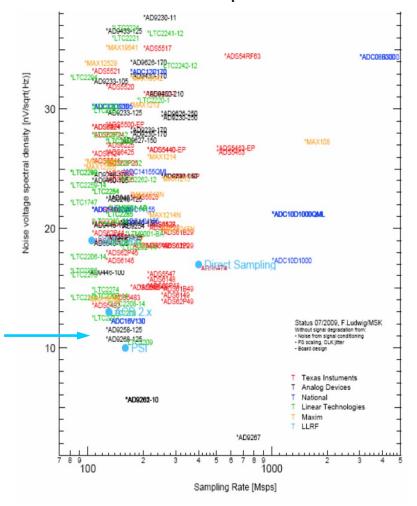

- → ADC spectral density is (was) the limitation in the current SIMCON system 14-bits (-135dBc/Hz) -> 16-bits (-147dBc/Hz)

AD9268 Eval Board with FLASH reference

Actual ADC landscape:

Figure 1. AD9268 and AD9269 Family Evaluation Board and HSC-ADC-EVALCZ Data Capture Board

- <u>Testconfguration:</u> Multi-channel active receiver (KS Version)

- AD9268, dual, 16-bits, 125Msps, Evaluation Board

- FLASH Reference, Extension Hall

- LO-Generation Module (19", FL, PM version)

- Offline Matlab non-ig analysis (N=2\*65K)

## Consequences from FLASH operation

FIL

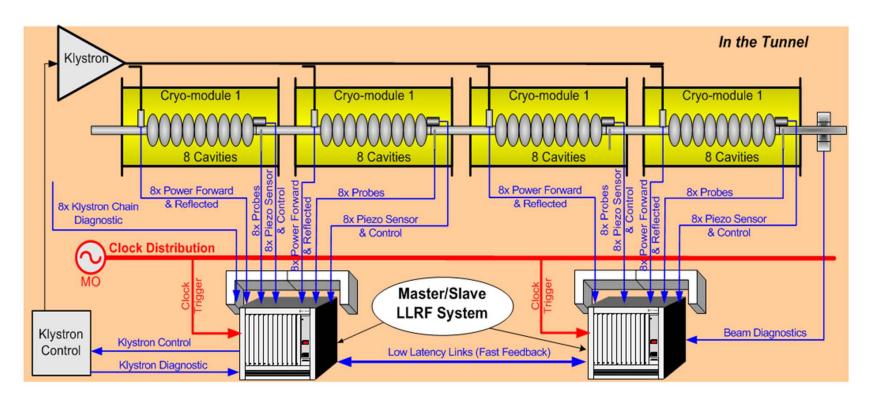

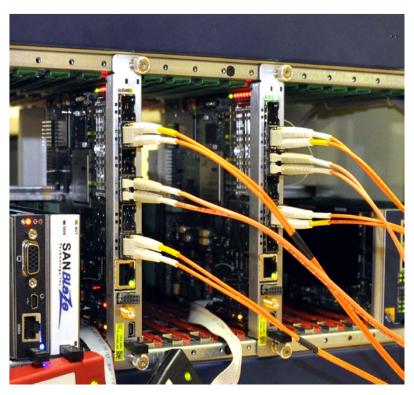

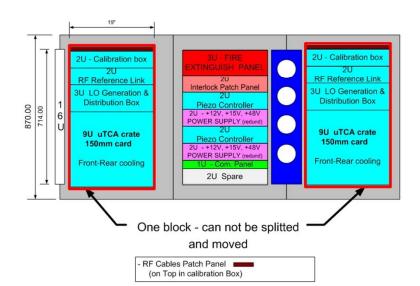

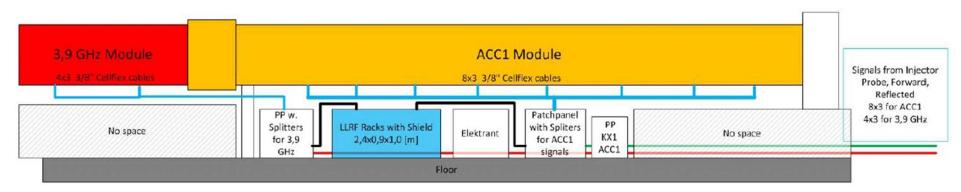

2 semi-distributed uTCA stations supply 4 cavity modules (J0,L1,L2,L3)

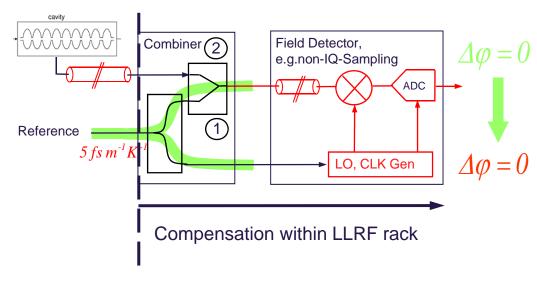

Driving Argument — Short pickup cables for low drifts (10fs/m/K) and prevent crosstalk from high power cables

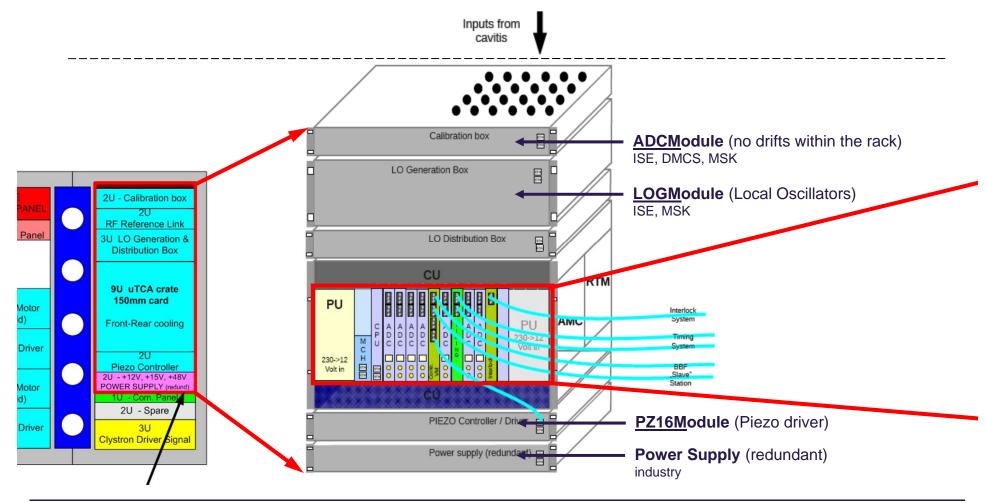

■ How will a LLRF System look like inside . . . 19" modules . . .

FIL

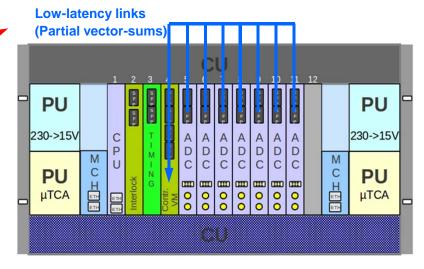

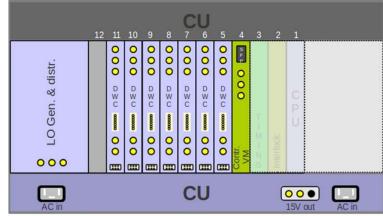

#### ... and the crate ...

AMC front : (data pre-processing)

RTM rear: (signal conditioning)

Slot #01: CPU

Slot #02: Interlock

Slot #03: Timing

Slot #04: **LLRF Controller**Slot #05: ADC, Klystron Chain

Slot #06: ADC, VS Reflected

Slot #07: ADC, VS Reflected

Slot #08: ADC, VS Forward

Slot #09: ADC, VS Forward

Slot #10: ADC, VS Probe

Slot #11: ADC, VS Probe

Slot #12: free

(Industry)

(MCS)

(MCS)

(uTLC / DMCS, MSK)

(SIS8300 / Struck, MCS, MSK)

Slot #01: -Slot #02: -Slot #03: -Slot #04: Klystron Driver (uTLC VM / DMCS, ISE) Slot #05: **DWC**, **Klystron Chain** (DWC8300 / ISE, MSK) Slot #06: DWC, Reflected (DWC8300 / ISE, MSK) Slot #07: DWC, Reflected (DWC8300 / ISE, MSK) Slot #08: DWC, Forward (DWC8300 / ISE, MSK) Slot #09: DWC, Forward (DWC8300 / ISE, MSK) Slot #10: DWC, Probe (DWC8300 / ISE, MSK) Slot #11: DWC, Probe (DWC8300 / ISE, MSK) Slot #12: free

Slot #15: Test LO-Generation

(uLOG RF-Backplane Test)

FIL

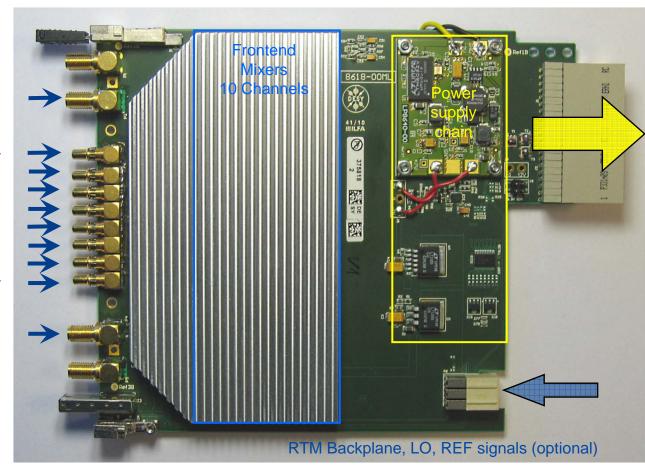

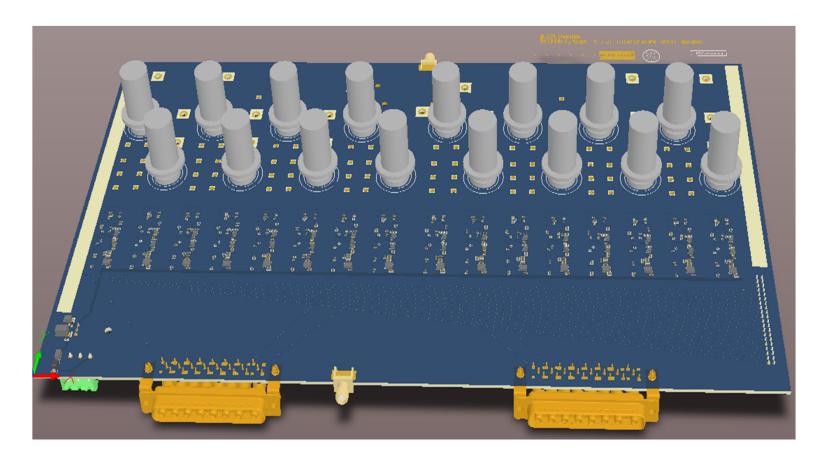

#### Multi-channel Down-Converter (DWC8300 R1.0)

- 10 channel field detection (1.3GHz ... 3.9GHz version)

- Rear / Backplane RF access

- 8 Layer, Rogers (ZE)

8+1 x RF Inputs LO Input (1.3GHz...3,9GHz)

Courtesy: J.Piekarski / ISE M.Hoffmann, D.Kühn / DESY

FIL

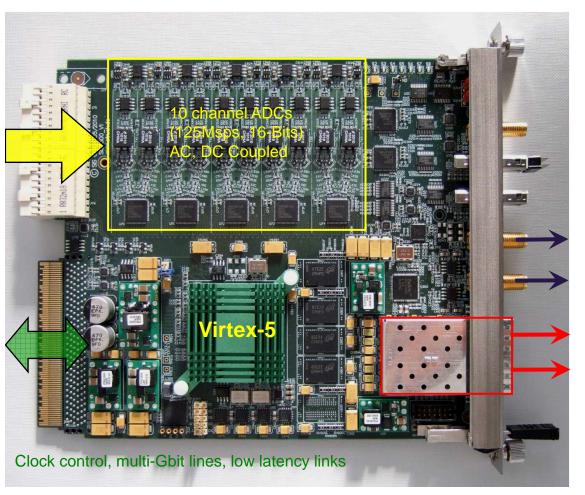

#### Digitizer, Partial Vector Sum (SIS8300\_V2)

- 10 channel ADCs (125Msps, 16-Bits)

- FPGA partial cavity vector sum

- Low latency links via uTCA-backplane

2x DAC Outputs

SFP front I/O's Fiber or cable

FIL

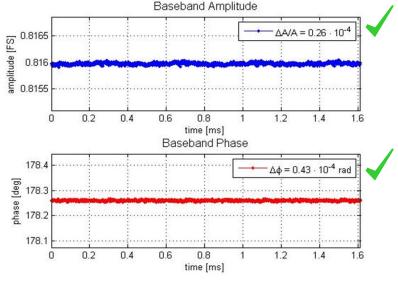

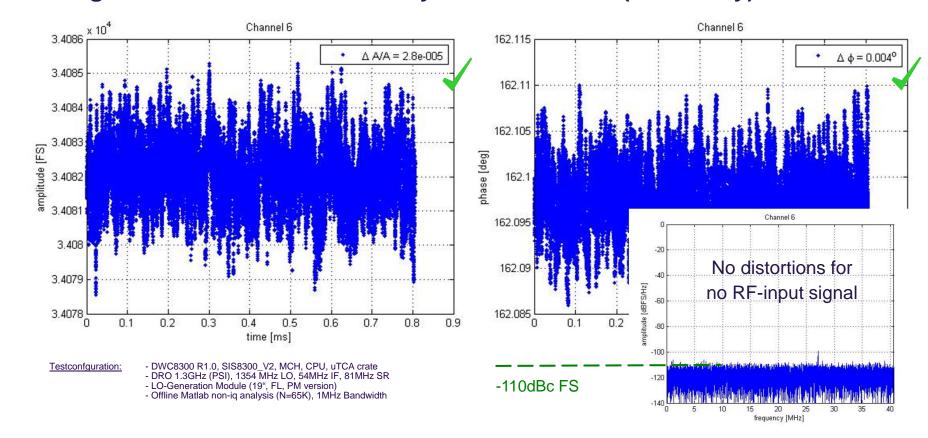

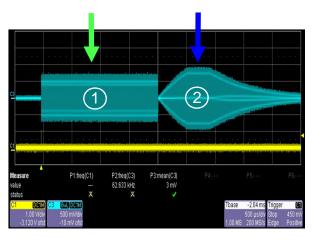

#### Signal-chain short-term stability in a uTCA crate (laboratory) :

Single cavity resolution improved by a factor of 5 to dA/A=2.8E-5.

Signal integrity in uTCA crate achieved Eval board performance!

FIL

#### LLRF Controller (uTLC)

... during debugging ...

- LLRF Controller, 6 Fiber Ports, 2 GB-Links

- FPGA, DSP

Courtesy: D. Makowski / DMCS

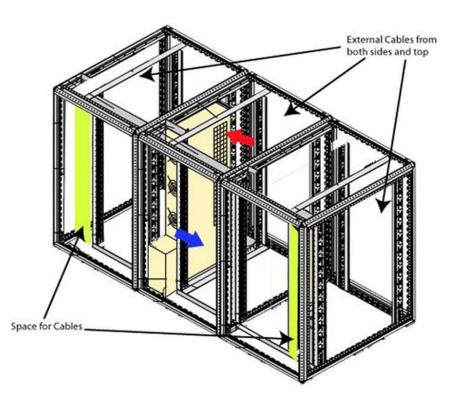

### Coarse inner rack temperature stability (<0.5°<sub>pp</sub>)

Courtesy: W. Wierba / IFJ

#### Reference injection calibration (simplified):

#### **Relative Phase Calibration:**

Injected reference Cavity signal and calibration Measurement

#### \* Uncompensated Heliax Pickup-cables:

- Covered by Beam-based Feedback

- Heliax optimal operating point [32 deg] by heating

- 201x cavity-pickup reflectometer upgrade

- Long-term stability improvements by a factor of 100 from the ps-range to about 20fs (pp).

- /

- Demands on rack temp-conditioning will be relaxed.

FIL

<u>Automated Drift Calibration Module (ADCM)</u> (design stage)

Courtesy: J. Piekarski / ISE

FIL

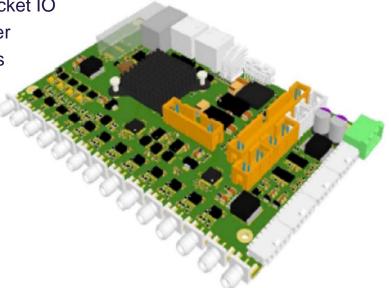

#### <u>Temperature Control & Monitoring Board (TMCB)</u>

- Control module for all 19" modules

- Common hardware, software and firmware

- Variant assembly

- ADC, DAC data-acquisition (16-, 24-bit)

- Peltier temperature control

■ I2C, GPIO, Rocket IO

Timing Receiver

GP LVDS Links

Ethernet

Instrumentation Technologies d.d.

Velika pot 22 5250 Solkan

Tel: +386 5 3352600 Fax: +386 5 3352601

#### Production folder for:

name: TMCB1

version: A

variant: Master

I-Tech Code: 4205

## Planned LLRF upgrades at FLASH

#### 2011

| • | REGAE | (May-July) | 1 Crate (8) |

|---|-------|------------|-------------|

|---|-------|------------|-------------|

FLASH ACC1 Test & Software (July-Sep) 1 Crate (24)

(Aug-Sep) PITZ TDS 1 Crate (8)

(Sep) 1 Crate (24) CMTB

Racks ACC67 (Sep-Dec) Ext. Hall 3

(Sep-Dec) Racks ACC1/ACC39

Tunnel (preparation) Racks ACC23 (Sep-Dec) Tunnel (preparation)

#### 2012

FLASH ACC23 (Spring) 1 Crate (48)

(Spring) 1 Crate (48) FLASH ACC67

## Planned LLRF upgrades at FLASH

FIL

- Test of long-term and short-term stability at FLASH.

- Investigate possible improvements on the beam and SASE.

# Thanks for your attention!