## Developing for SoC-based AMCs.

Jan Marjanovic (MTCA Tech Lab/DESY) 2021-12-07

#### 10th MicroTCA Workshop, Hamburg

- Hardware Introduction

- Device and Board Architecture

- Advantages of SoC-based AMCs

- Examples

- Tips and Tricks

- Conclusion

## **Hardware Introduction**

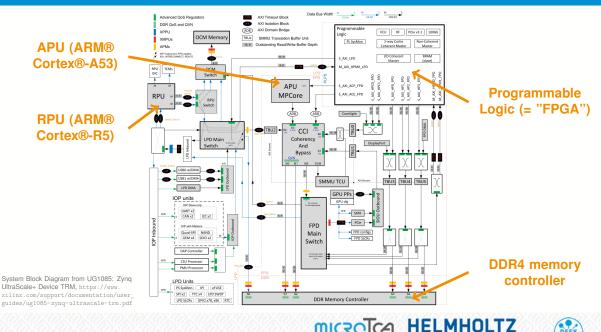

The Zyng MPSoC [...] comprises a number of different processing elements, each optimised for particular purposes — for instance, a set of applications processors, real-time processor, and a graphics processor, as well as Field Programmable Gate Array (FPGA) programmable logic.

from L.H. Crockett, D. Northcote, C. Ramsay: Exploring Zynq® MPSoC, 2019, https://www.zynq-mpsoc-book.com/

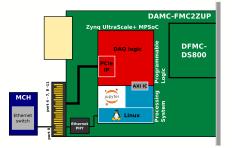

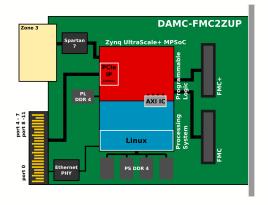

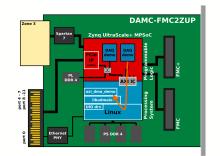

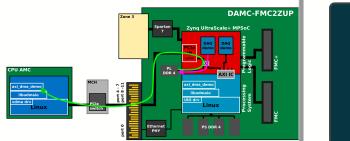

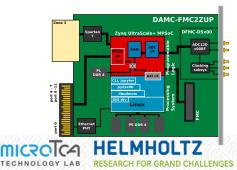

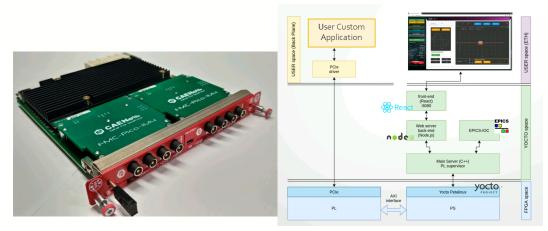

#### DAMC-FMC2ZUP

High-performance FMC/FMC+ carrier (Xilinx Zyng<sup>®</sup> UltraScale+<sup>™</sup> MPSoC)

TECHNOLOGY LAB

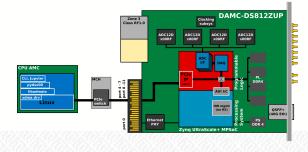

#### DAMC-DS812ZUP

Low-latency high-speed 8-ch digitizer (Xilinx Zyng<sup>®</sup> UltraScale+<sup>™</sup> MPSoC)

DAMC-FMC1Z7IO Cost-optimized FMC carrier (Xilinx Zvng

-7000)

#### The "standard" part:

- a large FPGA, lots of DSPs, fast transceivers

- FMC and FMC+ slot, Zone 3 Class D1.1

- backplane connections: PCIe, LLL, MLVDS, TCLK

- flexible clocking scheme with White Rabbit support

#### The "computer" part:

- processors

- Ethernet (next slide)

- USB C and DisplayPort

- SATA on AMC port 2 and port 3

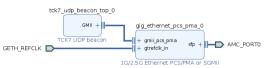

Example with DFMC-DSx00 on DAMC-FMC2ZUP; the board can be interfaced either through PCI Express or through Ethernet (Jupyter notebooks)

Backplane Ethernet (port 0) is ...

- ... on previous-gen boards<sup>1</sup> connected to FPGA MGT

- Ethernet implementation in FPGA:

- with hard IP: requires high effort, not very flexible

- with soft core: low performance, limited capabilities, complicated integration

- ... on SoC-based boards<sup>2</sup> connected to Processing System (ARM® CPU)

- Link is operational even when FPGA is not programmed

- Leverages Linux network stack

- SSH for development

- ▶ HTTP(S), EPICS, ... for deployment

<sup>1</sup>DAMC-FMC20, DAMC-FMC25, DAMC-TCK7 <sup>2</sup>DAMC-FMC1Z7IO, DAMC-FMC2ZUP, DAMC-DS812ZUP

https://github.com/MicroTCA-Tech-Lab/damc-tck7-fpga-bsp

## **Architecture**

#### Device architecture - Xilinx Zynq UltraScale+ MPSoC

Developing for SoC-based AMCs J. Marjanovic, 2021-12-07, Page 8/37

**RESEARCH FOR GRAND CHALLENGES**

TECHNOLOGY LAB

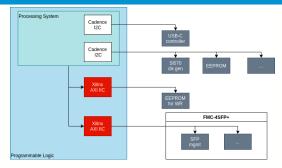

#### Board architecture - DAMC-FMC2ZUP

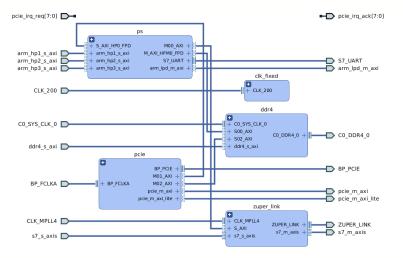

- PCIe connected to Programmable Logic (PL)

- Ethernet connected to Processing System (PS)

- Independent memories for PL and PS

Omitted for clarity: LLL (port 8 - 11, 12 - 15), MLVDS, SATA, USB-C, White Rabbit, clocking, IPMI/management

Vivado project in the Board Support Package, each subsystem is handled in a separate hierarchy:

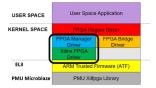

#### Software

#### Components of an Embedded Linux:

First Stage BootLoader

initializes Zynq internals (PLL, PS DDR4, ...)

#### bootloader (u-boot) and bootloader commands/script

copies kernel image and Device Tree Blob (DTB) into memory, prepares environment (e.g. MAC address for Ethernet), optionally programs PL (FPGA)

#### device tree blob

describes HW to Linux (Zynq internals, on-board periphery)

- kernel

- root filesystem

init, coreutils, ssh server, glibc, Python, application programs, ...

Built using Yocto from:

- "standard" layers

- Xilinx layers

- AMC BSP layers

- application layer

With Bitbake (Yocto) images derived from petalinux-image-full (e.g. zup-image-demo-full) the result is a full-blown Linux distribution:

| jan@ZUP-0555 🔪 lsb      | release -a   |                          |               |               |    |

|-------------------------|--------------|--------------------------|---------------|---------------|----|

| LSB Version: n/a        |              |                          |               |               |    |

| Distributor ID: petalin | ux           |                          |               |               |    |

| Description: PetaLin    | ux 2020.1    |                          |               |               |    |

| Release: 2020.1         |              |                          |               |               |    |

| Codename: zeus          |              |                          |               |               |    |

| jan@ZUP-0555 🔷 una      | me -a        |                          |               |               |    |

| Linux ZUP-0555 5.4.0-xi | linx-v2020.1 | l #1 SMP Thu             | Mar 4 22:37:  | 31 UTC 2021 a | аа |

| ch64 GNU/Linux          |              |                          |               |               |    |

| jan@ZUP-0555 🚬 fre      | e -h         |                          |               |               |    |

| total                   | used         | free                     | shared bu     | iff/cache av  | /a |

| Mem: 3.8Gi              | 318Mi        | 3.3Gi                    | 0.0Ki         | 267Mi         |    |

| Swap: OB                | 0B           | 0B                       |               |               |    |

|                         | hon3versi    | Lon                      |               |               |    |

| Python 3.7.6            |              |                          |               |               |    |

| jan@ZUP-0555 🔪 ~ 🖉 gcc  | version      |                          |               |               |    |

| gcc (GCC) 9.2.0         |              |                          |               |               |    |

| Copyright (C) 2019 Free |              |                          |               |               |    |

| This is free software;  |              |                          |               |               |    |

| warranty; not even for  | MERCHANTABIL | ITY or FITNE             | ESS FOR A PAR | TICULAR PURPO | )S |

| jan@ZUP-0555 🚬 cat      | /sys/class/  | /fpga_manager            | /fpga0/state  |               |    |

| operating               |              |                          |               |               |    |

| jan@ZUP-0555 🔪 fil      | e /mnt/sd-mr | ncblk0p1/down            | load-damc-fr  | c2zup.bit     |    |

| /mnt/sd-mmcblk0p1/downl | oad-damc-fmc | :2zup.bit: Xi            | linx BIT dat. | a - from damo | c  |

| D=0XFFFFFFFF;Version=20 | 20.1 - for > | <pre>(czu11eg-ffvc</pre> | :1760-2L-e -  | built 2021/03 | 3/ |

| ta length 0x167d0ec _   |              |                          |               |               |    |

| jan@ZUP-0555 🚬 ~        |              |                          |               |               |    |

## **Advantages of SoC-based AMCs**

- Application partitioning

- Stand-alone products

- Configuration, monitoring

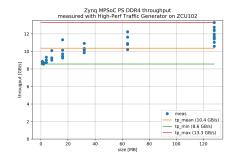

SoC-based design vs PCIe-based designs:

- data bandwidth between FPGA and CPU<sup>1</sup>

- interrupt latency, real-time performance

- computing power

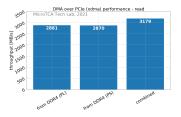

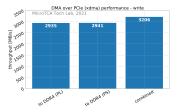

### Data bandwidth

TECHNOLOGY LAB

PCIe throughput on DAMC-FMC2ZUP in gen3 x4 config

<sup>1</sup>assuming PCIe gen3 x4 or x8

#### **Application partitioning**

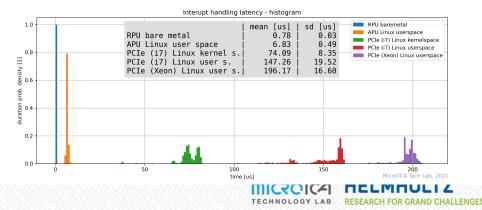

#### **Interrupt latency**

- ▶ Real-time processing unit (with Arm Cortex™-R5F) unsurprisingly performs really well

- Application Processing Unit (with Arm Cortex<sup>TM</sup>-A53) in user space provides a good compromise between latency and ease of use

- PCIe interrupt latency higher and less deterministic

→ still OK for some applications (e.g. pulsed accelerators)

#### **Computing power**

On everyday tasks Cortex-A53 is approx. 10 times slower than a dedicated CPU AMC (with Intel i7)

| In [1]:                                                                          | In [1]:                                                                                  |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| <pre>import platform import numpy as np</pre>                                    | <pre>import platform import numpy as np</pre>                                            |

| In [2]:                                                                          | In [2]:                                                                                  |

| platform.machine()                                                               | platform.machine()                                                                       |

| Out[2]:                                                                          | Out[2]:                                                                                  |

| 'aarch64'                                                                        | 'x86_64'                                                                                 |

| In [3]:                                                                          | In [3]:                                                                                  |

| <pre>xs = np.random.random(1024)</pre>                                           | <pre>xs = np.random.random(1024)</pre>                                                   |

| In [4]:                                                                          | In [4]:                                                                                  |

| %timeit np.fft.fft(xs)                                                           | %timeit np.fft.fft(xs)                                                                   |

| 110 µs ± 89.5 ns per loop (mean ± s<br>td. dev. of 7 runs, 10000 loops eac<br>h) | 11.5 $\mu s$ $\pm$ 38.3 ns per loop (mean $\pm$ std. dev. of 7 runs, 100000 loops e ach) |

#### XML parsing with Cortex-A53

#### XML parsing with Intel i7

- ▶ User software can run on the board, e.g. Web server, EPICS IOC or Jupyter notebook

- ▶ No installation needed → better out-of-box experience

- Easier deployment of FPGA images (sync between software and firmware)

- Vendor has a better control of the environment

- Advanced diagnostics tools can be "hidden" on the board

#### Configuration

Typically a board has several on-board components which need to be configured or initialized at the startup according to the application.

#### Old approach (non-SoC-based AMCs):

- state machines in the FPGA

- soft-core CPU (MicroBlaze, Nios II, LM32, ...)

#### New approach (SoC-based AMCs):

- a lot of I2C and SPI devices have Linux drivers<sup>1</sup>

- standard GPIO (libgpio) and I2C (i2c-tools) utilities

- Python or other high-level languages can be used

RESEARCH FOR GRAND CHALLENGE

https://www.analog.com/en/about-adi/news-room/press-releases/2021/11-30-2021-analog-devices-expands-linux-distribution.html

TECHNOLOGY LAB

<sup>&</sup>lt;sup>1</sup> press release from a couple of days ago:

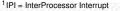

## **Examples**

BSP comes with Data Acquisition example

TechLab presentation on Thu at 13:30

- ► Two transfer paths:

- from FPGA into the PS memory (allocated with u-dma-buf)

- from FPGA into the PL memory, then with PCIe to the CPU

- libudmaio and pyudmaio used to handle the data

- Xilinx XDMA driver for PCle (https://github.com/MicroTCA-Tech-Lab/xdma-metapackage)

- BSP comes with Data Acquisition example

- ► Two transfer paths:

- from FPGA into the PS memory (allocated with u-dma-buf)

- from FPGA into the PL memory, then with PCIe to the CPU

- libudmaio and pyudmaio used to handle the data

- Xilinx XDMA driver for PCle (https://github.com/MicroTCA-Tech-Lab/xdma-metapackage)

TechLab presentation on Thu at 13:30

\$ axi\_dma\_demo\_cpp \ --mode xdma \ /dev/xdma/slot11 \ --pkt\_pause 35000 \

#### Standalone product

#### **DSx00 family**

- 8-channel digitizer, talks:

- Zink: "RF Performance of Z3 class RF1.0 ...", Wed 16:00

- Fenner: "Latest Hardware Developments ....", Thu 12:35

- Python library (pydsx00) provides a high-level interface to the hardware

- Runs both on x86\_64 (over PCIe, with xdma driver) and on aarch64 (ARM)

- Easy start with Jupyter notebooks

- CLI for advanced users (long captures, ...)

\$ dsx-cli AMC \

--xdma /dev/xdma/slot4 '

plot\_fft --nr\_samp 1e6

# \$ dsr-cli AMC \ --xdma /dev/xdma/slot4 \ dump \ --nr\_samp 250e6 \ meas\_data0.npy Written meas\_data0.npy

#### DAMC-DS812ZUP - communication between the app and the RPU

- PLL and ADCs are managed by the firmware (HW mgmt) running on Cortex-R5 (RPU)

- Application software (pydsx00) needs to communicate with the HW mgmt

- Solution: IPI<sup>1</sup> Messages

- Managing other processors from Cortex-A53 (APU) - still to be implemented on DS812ZUP:

remoteproc - https://www.kernel.org/doc/Documentation/remoteproc.txt

Figure 13-6: IPI Message Passing Architecture

Processor communications include both an IPI interrupt structure and memory buffers to exchange **short private 32B messages** between eight IPI agents — the PMU, RPU, APU, and PL processors. Access to the interrupt registers and message buffers is protected by the XPPU to give exclusive access to the AXI transactions of the agents.

from UG1085, https://www.xilinx.com/support/documentation/user\_guides/ug1085-zynq-ultrascale-trm.pdf

#### Configuration, example #1

#### FMC116 with DAMC-FMC1Z7IO - PLL configuration

- ► Used in a LISA phasemeter prototype → "Prof. Gerberding: Update on LISA Phasemeter ..." at 16:00 today

- Code migrated from Virtex-6 to Zynq-7000

**Before:** . coe file to initialize BRAM, state machine to program the PLL over SPI

Round-trip-time for a change: approx. 30 minutes

After:

Use of vendor tool to generate a .stp file

#### CLI to program the PLL, used in init script:

| \$ fmc1 |           | ad9517  |    | ogram-stp | iqdemod.stp |  |

|---------|-----------|---------|----|-----------|-------------|--|

|         | 6_cli py  |         |    |           |             |  |

| AD9517  | part_id = |         |    |           |             |  |

| AD9517  | PLL readt |         | 4f |           |             |  |

| Digit   |           | letect  |    |           |             |  |

| REF1    | freq > th | reshold |    |           |             |  |

HELMHOLTZ

RESEARCH FOR GRAND CHALLENGE

Round-trip-time for a change: approx. 1 minute, easier to use

#### Monitoring, example #2

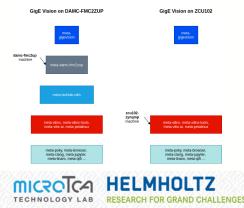

#### GigE Vision on ZUP

- Protocol implementation split between HW (high-performance part) and SW (initialization, XML parsing, link management)

- MAC addresses, S/N, production date stored in on-board EEPROM

- SFP modules (EEPROM at 0x50 for identification, DDI at 0x51 for monitoring)

|  |  |  |  |  |  |  |   |            | 789abcde |

|--|--|--|--|--|--|--|---|------------|----------|

|  |  |  |  |  |  |  |   |            | @.?.?g   |

|  |  |  |  |  |  |  |   |            |          |

|  |  |  |  |  |  |  |   |            | .SFP-10G |

|  |  |  |  |  |  |  | Т |            |          |

|  |  |  |  |  |  |  |   | 22 8 0 1 0 | 04009153 |

#### **Examples from our partners**

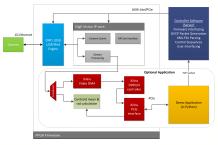

#### D-TACQ ACQ400 RTM with DAMC-FMC1Z7IO

D-TACQ Solutions Ltd (https://www.d-tacq.com/) is using Z7IO in combination with ACQ400-MTCA-RTM-2.

#### Example: EPICS IOC running on Z7IO

#### CAEN ELS picoammeter on DAMC-FMC2ZUP

Web server (Node.js) with React front-end and EPICS IOC running on the board.

MICROTCA HELMHOLTZ

TECHNOLOGY LAB

**RESEARCH FOR GRAND CHALLENGES**

CAENels presentation on Wed at 13:40

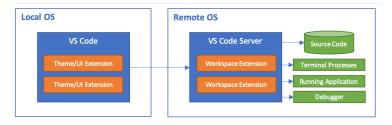

## **Tips and Tricks**

- SDK can be generated with Yocto (bitbake -c populate\_sdk)

- ▶ vim, nano, ed<sup>1</sup> and git are installed on the board by default

- for more complex development, several cross-development options are available, for example: Visual Studio Code Remote Development

https://code.visualstudio.com/docs/remote/remote-overview

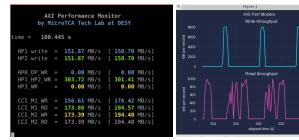

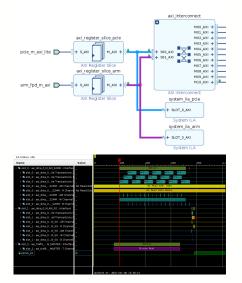

#### System ILA and AXI Performance Monitor

- systems are becoming increasingly complex

- good debugging tools are available, e.g. System ILA<sup>1</sup>

- System ILA can be used to observe AXI transactions

- three System ILAs are included in the example design

- ARM interface, PCIe interface, DMA operation

- AXI Performance Monitor can be used to observe interconnects, e.g. when acquiring data:

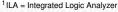

Xilinx Virtual Cable (XVC) is a TCP/IP-based protocol that acts like a JTAG cable and provides a means to access and debug your FPGA or SoC design without using a physical cable.

from https://www.xilinx.com/products/intellectual-property/xvc.html

#### Figure 15: AXI to BSCAN Debug Bridge

- Software-side of the XVC is included in the BSP

- two packages in meta-techlab-utils layer: xilinx-xvc-driver and xilinx-xvc-server

- Useful links:

- https://support.xilinx.com/s/article/974879

- https://www.xilinx.com/support/documentation/sw\_manuals/xilinx2020\_2/ ug908-vivado-programming-debugging.pdf

#### **FPGA Manager**

## The Zynq UltraScale+ MPSoC Programmable Logic (PL) can be programmed either using First Stage Boot-loader(FSBL), U-Boot or **through Linux**.

from https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18841847/Solution+ZynqMP+PL+Programming

Load the FPGA image (and the device tree overlay) from Linux userspace

(init script from fpgautil-init.bb):

echo "fpgautil-init: downloading FPGA image" fpgautil ~b /lib/firmware/base/damc\_fmc2zup\_top.bit.bin ~o /lib/firmware/base/base.dtbo echo "fpgautil-init: FPGA image download done"

#### Un-load the FPGA image and the device tree overlay:

# fpgautil -R

#### Get the FPGA ID code (device identifier):

# fpgautil -r

Readback contents are stored in the file readback.bin

# grap IDCODE readback.bin

IDCODE --> 4a4e093

FPGA MANAGER FLOW DIAGRAM

local.conf should include:

IMAGE\_FEATURES += " fpga-manager"

#### **Device Tree**

- Two separate files on the board (when using FPGA manager):

- system: /mnt/sd-mmcblk0p1/damc-fmc2zup-system.dtb

- PL:/lib/firmware/base/base.dtbo

- when using our BSP (meta-techlab-utils) add DT\_FROM\_BD\_ENABLE = "1" to local.conf to get the IPs from the application into the device tree

- User-generated IPs can be handled by the UIO driver (https://www.kernel.org/doc/html/v5.4/driver-api/uio-howto.html)

- Isuio (https://www.osadl.org/UIO-Archives.uio-archives.0.html) can be used to list all IPs present in the device tree

```

root22UP-0001: 7/lsuio-0.2.0# ./lsuio

ui09: name=hier_daq_pcie_axi_bram_ctrl, version=devicetree, events=0

map[0]: addr=0xA0220000, size=8192

ui08: name=hier_daq_arm_axi_traffic_gen, version=devicetree, events=0

map[0]: addr=0xA010000, size=65536

ui07: name=hier_daq_arm_axi_dma, version=devicetree, events=0

map[0]: addr=0xA012000, size=4096

ui06: name=hier_daq_arm_axi_bram_ctrl, version=devicetree, events=0

map[0]: addr=0xA0120000, size=8192

ui06: name=lier_da_arm_axi_bram_ctrl, version=devicetree, events=0

map[0]: addr=0xA0120000, size=8192

```

- > A single command required to create a repo: bitbake package-index

- Configuration file in /etc/yum.repos.d/

#### Serving the repository (on the build server):

| 0                                                |                |               |                          | ,                          |

|--------------------------------------------------|----------------|---------------|--------------------------|----------------------------|

| 1an@MSKTECHLABEXTCPU0004                         |                | ➡ 7c2e51b     | python3 \                |                            |

| -m http.server \                                 |                |               |                          |                            |

| bind EXTCPU-100-0004                             | .tech.lab 8123 |               |                          |                            |

| Serving HTTP on 192.168.1.                       | 149 port 8123  | (http://192.) | 168.1.149:8123/)         |                            |

| 192.168.1.87 [06/Oct/2                           | 021 20:18:591  | "GET /repodat | ta/repond.xml HTTP/1.1"  | 200 -                      |

| 192.168.1.87 [06/Oct/2                           | 021 20:18:59   | "GET /repodat | ta/repond.xml HTTP/1.1"  | 260 -                      |

| 192.168.1.87 [06/Oct/2<br>192.168.1.87 [06/Oct/2 | 021 20:18:591  | "GET /repodat | ta/5375abad73abc6a4b10a  | 0358a03fd739416e5a62a1eed  |

| c01f60dcd20b1376f7-primary                       | .xml.oz HTTP/1 | 1.1" 200 -    |                          |                            |

| 192.168.1.87 [06/Oct/2                           | 021 20:18:591  | "GET /repodat | ta/0a48513bdbabb2eb35df  | a9075af4d822bbcb920cda187  |

| 298c2ad24d01aa402e-filelis                       | ts.xml.az HTŤE | 2/1.1" 200 -  |                          |                            |

| 192.168.1.87 [06/Oct/2                           |                |               | ta/repond.xml HTTP/1.1"  | 260 -                      |

| 192.168.1.87 06/Oct/2                            | 021 20:19:261  | "GET /damc fr | nc2zup/device-tree-lic-; | cilinx+v2020.2+git0+f725aa |

| ecff-r0.damc_fmc2zup.rpm H                       |                |               |                          | ,                          |

| 192.168.1.87 - [06/Oct/2                         | 021 20:19:261  | "GET /damc fr | nc2zup/device-tree-xili  | x+v2020.2+git0+f725aaecff  |

| -r0.damc fmc2zup.rpm HTTP/                       |                |               |                          |                            |

| 192.168.1.87 [06/Oct/2                           | 021 20:19:26]  | "GET /damc fr | nc2zup/fpga-manager-uti  | -base-xilinx+oit0+bc84458  |

| 333-r0.danc fnc2zup.rpn HT                       | TP/1.1" 200 -  |               |                          | ,                          |

| 192.168.1.87 [06/Oct/2                           | 021 20:19:26]  | "GET /damc fr | nc2zup/fpga-manager-uti  | -lic-xilinx+git0+bc844583  |

| 33-r0.damc fmc2zup.rpm HTT                       | P/1.1" 200 -   |               |                          | 2                          |

| 192.168.1.87 [06/Oct/2                           |                | "GET /damc_fr | nc2zup/fpga-manager-uti  | -xilinx+git0+bc84458333-r  |

| 0.damc fmc2zup.rpm HTTP/1.                       |                |               |                          |                            |

|                                                  |                |               |                          |                            |

|                                                  |                |               |                          |                            |

|                                                  |                |               |                          |                            |

|                                                  |                |               |                          |                            |

|                                                  |                |               |                          |                            |

|                                                  |                |               |                          |                            |

|                                                  |                |               |                          |                            |

|                                                  |                |               |                          |                            |

|                                                  |                |               |                          |                            |

|                                                  |                |               |                          |                            |

|                                                  |                |               |                          |                            |

|                                                  |                |               |                          |                            |

|                                                  |                |               |                          |                            |

|                                                  |                |               |                          |                            |

|                                                  |                |               |                          |                            |

|                                                  |                |               |                          |                            |

|                                                  |                |               |                          |                            |

|                                                  |                |               |                          |                            |

#### Updating the packages (on the board):

| root@ZUP-0552:~# dnfre<br>extcpu0004<br>Dependencies resolved.                                                          | fresh update                                                                                                  | 607 kB/s   3.0                                                                                                                                                                                                                                                            | [ <u>38/172]</u><br>kB 00:00                                                         |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Package                                                                                                                 | Architecture                                                                                                  | Version Repo                                                                                                                                                                                                                                                              | sitory Size                                                                          |

| Reinstalling:<br>device-tree-lic<br>device-tree<br>fpga-manager-util-base<br>fpga-manager-util-lic<br>fpga-manager-util | damc_fnc2zup<br>damc_fnc2zup<br>damc_fnc2zup<br>damc_fnc2zup<br>damc_fnc2zup<br>damc_fnc2zup                  | xilinx+v2020.2+git0+f725aaecff-r0 oe-p<br>xilinx+git0+bc84458333-r0 oe-p<br>xilinx+git0+bc84458333-r0 oe-p                                                                                                                                                                | oackages 13 k<br>oackages 15 k<br>oackages 2.5 M<br>oackages 7.2 k<br>oackages 5.8 k |

| Transaction Summary                                                                                                     |                                                                                                               |                                                                                                                                                                                                                                                                           |                                                                                      |

| (2/5): device-tree-xilinx<br>(3/5): fpga-manager-util-<br>(4/5): fpga-manager-util-                                     | linx+v2020.2+git<br>+v2020.2+git0+f7<br>lic-xilinx+git0+<br>xilinx+git0+bc84                                  | 9+7725aaacff+r0.danc_fnc2zup 2.0 W8/s   13<br>25aaccf+r0.danc_fnc2zup.rpn 2.1 W8/s   15<br>0c6436333-14 cm_fnc2zup.rpn 1.1 W8/s   15<br>0c643633-14 cm_fnc2zup.rpn 1.1 w8/s   12.4<br>45445833-05 cm_fnc2zup.rpn 4.6 W8/s   2.5<br>0c6445833-05 cm_fnc2zup. 46 W8/s   2.5 | kB 00:00<br>kB 00:00<br>kB 00:00                                                     |

| Reinstalling : fpga<br>Reinstalling : devi<br>Running scriptlet: devi<br>%prein(device-tree-xilinx                      | ed.<br>d.<br>-nanager-util-li<br>-nanager-util-ba<br>ce-tree-lic-xili<br>ce-tree-xilinx+v<br>+v2020.2+git0+f7 | 43 MB/s   2.6<br>c-xilixxxgit0Hc0445833-r0.damc_fmc2zup<br>se-xilinxvgit0Hc04458333-r0.damc_fmc2zup<br>zwv2020.2qtit0+f725aacff-r0.damc_fmc2zup<br>250aceff-r0.damc_fmc2zup):scriptletstart<br>25aacff-r0.damc_fmc2zup):scriptletstart                                    | 1/1<br>1/10<br>2/10<br>3/10<br>4/10                                                  |

| + set -e<br>+ rm -rf /usr/lib/opkg/al                                                                                   | ternatives/devic                                                                                              |                                                                                                                                                                                                                                                                           |                                                                                      |

HELMHOLTZ

RESEARCH FOR GRAND CHALLENGE

## Conclusion

- Several new and interesting AMC boards were developed; available to the community and partners for their projects

- All important features of previous-gen boards are still present (PCIe, LLL, MLVDS, TCLK, Zone3)

- ► Tight integration between a CPU and FPGA → solutions leveraging all components

- Good eco-system (driven by Xilinx); smooth integration between different components

- The board can act as a standalone product

- Improved quality-of-life for the developers and users

## Thank you

https://techlab.desy.de mtca-techlab@desy.de

Deutsches Elektronen-Synchrotron DESY A Research Centre of the Helmholtz Association Notkestr. 85, 22607 Hamburg, Germany