# IPMI Support for FMC modules in MicroTCA.4 Systems

Dariusz Makowski Patryk Nowak vel Nowakowski

## **FPGA Mezzanine Card Standards (2)**

- Two standards available:

- FMC ANSI/VITA 57.1-2019 (+Errata)

- FMC+ ANSI/VITA 57.4-2018 (+Errata)

- Modular expansion of FPGA systems

- High speed communication interfaces (up to 28 Gbps)

- Low/High Pin Count (LPC/HPC) connectors for I/O flexibility (160/400 pins)

- High Serial Pin Count (HSPC) connector (560 pins)

- High Serial Pin Count extension (HSPCe) connector (80 pins)

- Mechanical dimensions allow for up to two

FMC modules on a single MTCA.4 AMC

board

# Example of FMC module

2/25

### Support for FMC Module in MTCA.4 Systems

- Many existing MicroTCA.4 designs utilizes FMC modules

- FMC I/O available on front panel of AMC or RTM carriers

- Identification of connected FMC module by reading FRU inside fixed-address I2C EEPROM

- FMC module managed and controlled by MMC on AMC carrier board

## Support for FMC Module in MTCA.4 Systems

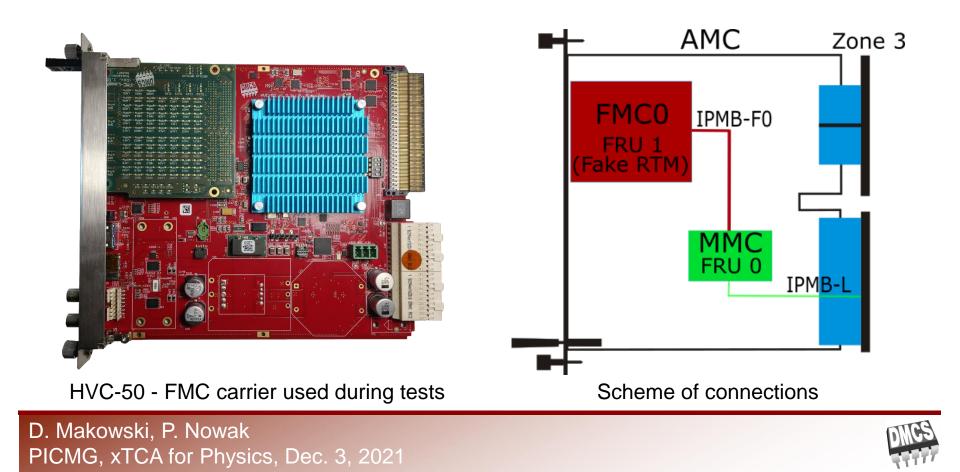

The HVC-50 board with single FMC module (Xilinx Zynq US+ XCZU4CG)

The MFMC carrier board with two FMC modules (Xilinx Artix XC7A200T)

# 5/25

#### **Current Issues with FMC modules in MTCA.4 Systems**

- Lack of management compatibility of MicroTCA and FMC standards

- No thermal management Risk of overheating FMC module

- FMC modules may dissipate significant amount of heat (more than 10 Watts)

- FMC modules need thermometers, now included in VITA57.x standards

- FMC modules should be involved in temperature stabilisation process in the whole MicroTCA infrastructure

#### No centralized management of FMC – Full IPMI support needed

- FMC managed only locally by AMC carrier board MCH should have access to FMC FRU as well as sensors and initiate power on/off of the FMC module.

- FMC should be managed by MCH in similar manner as it is done currently with RTM

- FPGA IO voltages are automatically configured according to FMC module requirements and carrier possibilities

Powering up FMC must be done after checking if FMC is compatible with the carrier – DC load records need to be read from the FMC's FRU to chose right supply voltage

### **Proposed Assumptions**

- Allow for 2 FMC modules on AMC and 2 modules on RTM (total 4 modules)

- Prefer a simple solution based on I2C devices (no programmable IPMI controller on FMC, no complex sensors)

- A single FMC module should support:

- FRU EEPROM with Subtype 0 and Subtype 1 data

- Configurable voltages for each FMC module

- Temperature sensor: max. 2 sensors per FMC module

- MCH should provide support to detect 4 additional FRUs on AMC/RTM pair

- Display FRU data (reference voltages, clock direction, etc.)

- Additional sensors implemented as dynamic IPMI sensors

- Additional voltage sensors do we need them? Other sensors?

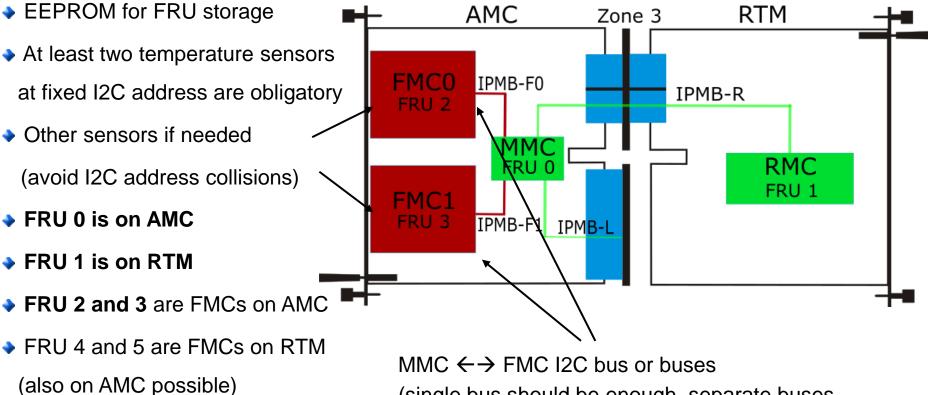

#### **Possible IPMI Support for FMC modules on MTCA.4 systems**

#### FMC modules with:

Do we need FRU 4 and 5?

MMC  $\leftarrow$  > FMC I2C bus or buses (single bus should be enough, separate buses could give more freedom )

We prefer a simple solution

## VITA 57.1 – Important Signals

#### **IPMB-F Bus:**

- **SCL** System Management I2C serial clock. This signal provides a clock reference to the FMC+ module from the carrier card for a two-wire serial management bus.

- **SDA** System Management I2C serial data. This signal provides a data line for a two-wire serial management bus.

- **GA[0..1]** These signals provide geographical addresses of the module(s) and are used for I2C channel

- **PRSNT\_M2C\_L** Module present signal. The ANSI/VITA-57.1 FMC standard defines this signal for a carrier card to successfully detect that an IO mezzanine module is installed.

- **CLK\_DIR** Used to determine whether the mezzanine module or the carrier card is the driver for CLK[2..3].

- PG\_C2M Power Good Carrier Card. This signal asserts high by the carrier card when power supplies VADJ, 12P0V, 3P3V are within tolerance.

- **PG\_M2C** Power Good Mezzanine. This signal asserts high by the mezzanine module when power supplies VIO\_B\_M2C, VREF\_A\_M2C, VREF\_B\_M2C are within tolerance.

## **IPMI** Support

The FMC mezzanine module provides hardware definition information that is read by an external controller using **IPMI commands and I2C serial bus transactions**. The mezzanine module supports the I2C link on pins SDA and SCL and optionally supports the base **IPMI commands defined in the PICMG 2.9** specification.

- FRU records according to Platform Management FRU Information Storage Definition V1.0

- **EEPROM shall include** the BOARD\_INFO area for identification of the mezzanine module

- Other data provided via FMC-specific MultiRecords (type 0xFA): Subtype 0 and Subtype 1.

9/25

#### **FRU EEPROM Address**

- Standard defines I2C addresses for EEPROM depending on GA [1/0] addresses (4 possibilities)

- Now double byte addressing also possible (32 kB)

- MicroTCA.4 needs suport for 32 kB

#### Table 10: I2C Address Decoding 2Kb and 32Kb EEPROM

|        | GA[01] | I2C Address    | I2C Addresses       |

|--------|--------|----------------|---------------------|

|        |        | for serial 2Kb | for <b>Optional</b> |

|        |        | EEPROM         | Devices             |

| 2Kb    | 00     | 0b101 0000     | 0bxxx xx00          |

| EEPROM | 01     | 0b101 0001     | 0bxxx xx01          |

|        | 10     | 0b101 0010     | 0bxxx xx10          |

|        | 11     | 0b101 0011     | 0bxxx xx11          |

|        | GA[01] | I2C Address    | I2C Addresses       |

|        |        | for serial     | for <b>Optional</b> |

|        |        | 32Kb           | Devices             |

|        |        | EEPROM         |                     |

| 32Kb   | 00     | 0b101 0100     | 0bxxx xx00          |

| EEPROM | 01     | 0b101 0101     | 0bxxx xx01          |

|        | 10     | 0b101 0110     | 0bxxx xx10          |

|        | 11     | 0b101 0111     | 0bxxx xx11          |

# **IPMI Support – Record Subtype 0**

#### **Provides informative data**

- Module size

- P1 and P2 connectors types

- Clock direction

- P1/P2 signals number

- Max clk frequency

| Field                         | Byte<br>Offset | Bit<br>Location | Length | Description                                                                                           |

|-------------------------------|----------------|-----------------|--------|-------------------------------------------------------------------------------------------------------|

| Subtype                       | 0              | 7:4             | 4 bits | 0 for main definition type                                                                            |

| Version                       | 0              | 3:0             | 4 bits | 0 for current version                                                                                 |

| Module Size                   | 1              | 7:6             | 2 bits | 0b00 = single width,<br>0b01 = double width                                                           |

| P1 Connector size             | 1              | 5:4             | 2 bits | $\begin{array}{l} 0b00 = LPC, \\ 0b01 = HPC \end{array}$                                              |

| P2 Connector size             | 1              | 3:2             | 2 bits | 0b00 = LPC,<br>0b01 = HPC,<br>0b11 = not fitted                                                       |

| Clock Direction               | 1              | 1               | 1 bit  | Defines direction of CLKx_BIDIR<br>0b0 = from Mezzanine to Carrier<br>0b1 = from Carrier to Mezzanine |

| reserved                      | 1              | 0               | 1 bit  | = 0b0                                                                                                 |

| P1 Bank A Number<br>Signals   | 2              | 7:0             | 8 bits | = number needed                                                                                       |

| P1 Bank B Number<br>Signals   | 3              | 7:0             | 8 bits | = number needed                                                                                       |

| P2 Bank A Number<br>Signals   | 4              | 7:0             | 8 bits | = number needed                                                                                       |

| P2 Bank B Number<br>Signals   | 5              | 7:0             | 8 bits | = number needed                                                                                       |

| P1 GBT Number<br>Transceivers | 6              | 7:4             | 4 bits | = number needed                                                                                       |

| P2 GBT Number<br>Transceivers | 6              | 3:0             | 4 bits | = number needed                                                                                       |

| Max Clock for TCK             | 7              | 7:0             | 8 bits | = clock in MHz                                                                                        |

## **IPMI Support – DC Output/DC Load Records**

Provides more useful data

- Supply voltages:

- VIO\_B\_M2C

- VREF\_A\_M2C

- VREF\_B\_M2C

- Power loads

- VADJ

- 3P3V

- 12P0V

- VADJ voltage ranges

- minimum

- maximum

- preferred

| DC Output<br>Record | Connector | Record<br>Type | Output<br>Number | Description                                                           |

|---------------------|-----------|----------------|------------------|-----------------------------------------------------------------------|

| VADJ                | P1        | LOAD           | 0                | Mandatory                                                             |

| 3P3V                | P1        | LOAD           | 1                | Mandatory                                                             |

| 12P0V               | P1        | LOAD           | 2                | Mandatory                                                             |

| VIO_B_M2C           | P1        | OUTPUT         | 3                | Mandatory                                                             |

| VREF_A_M2C          | P1        | OUTPUT         | 4                | Mandatory                                                             |

| VREF_B_M2C          | P1        | OUTPUT         | 5                | Mandatory                                                             |

| VADJ                | P2        | LOAD           | 6                | Mandatory for double width<br>with P2 fitted, n/a for Single<br>Width |

| 3P3V                | P2        | LOAD           | 7                | Mandatory for double<br>width with P2 fitted, n/a for<br>Single Width |

| 12P0V               | P2        | LOAD           | 8                | Mandatory for double<br>width with P2 fitted, n/a for<br>Single Width |

| VIO_B_M2C           | P2        | OUTPUT         | 9                | Mandatory for double width<br>with P2 fitted, n/a for Single<br>Width |

| VREF_A_M2C          | P2        | OUTPUT         | 10               | Mandatory for double width<br>with P2 fitted, n/a for Single<br>Width |

| VREF_B_M2C          | P2        | OUTPUT         | 11               | Mandatory for double<br>width with P2 fitted, n/a for<br>Single Width |

#### **Temperature Sensors**

**Observation 5.23-2:** The VITA 57.1 standard started with development cards, and as the market has grown and matured, more of the FMC sockets are being deployed on production systems. These systems depend on IPMI to enable easier system integration of boards from different vendors. In future revisions, this Standard could more tightly specify how the I2C bus can be used. **The potential addition of temperature sensor documentation is an example of this issue.**

- We could easily support up too 8 thermometers (2 per module)

- No strict definition of the temperature sensors addresses

Observation 5.23-3: To fully support using the I2C bus in a system supporting IPMI, the mezzanine module would need to have a Mezzanine Management Controller that can communicate with a Carrier Management Controller.

• We recommend a simple solution without MMC controller

## **Temperature Sensors (2)**

Currently, I2C addresses for thermometers can be specified only optionally in FRU via Subtype 1 record

The device string portion of this **MultiRecord subtype consists of 6-bit ASCII text** as defined in the ISD.

The string is divided into one or more I2C device records. Each device record consists of one or more address characters followed by one or more bytes of device name, example:

\* FMC module had two temperature sensors at addresses 0b0011nnn and 0b0100nnn

ICTLR\$%LM75

// I2C Controller addrres 0, I2C controller name: CTRL

// sensor 1 (address: 3), sensor 2 (address: 4)

Table 9: Subtype 1: I2C Device Definition (variable length and optional)

| Field         | Byte   | Bit      | Length | Description                    |

|---------------|--------|----------|--------|--------------------------------|

|               | Offset | Location |        |                                |

| Subtype       | 0      | 7:4      | 4 bits | 1 for I2C device definition    |

|               |        |          |        | subtype                        |

| Version       | 0      | 3:0      | 4 bits | 0 for current version          |

| Device String | 1N/8   |          | N bits | Device address / name strings, |

|               |        |          |        | see below                      |

## **Temperature Sensors (3)**

- Addresses of I2C thermometers could be specified in MicroTCA.X specification similarly as it is currently for EEPROM

- We need 2 address (A1/A0) for 4 FMC modules

- 1 address (A2) for sensor ID on FMC module (2 sensors max.)

- More possible using "Float" addressing (3 sensors)

| Table 10: | : I2C Address | Decoding | 2Kb and | 32Kb | EEPROM |

|-----------|---------------|----------|---------|------|--------|

|           |               | 0        |         |      |        |

|        | GA[01] | I2C Address              | I2C Addresses           |

|--------|--------|--------------------------|-------------------------|

|        |        | for serial 2Kb<br>EEPROM | for Optional<br>Devices |

| 2Kb    | 00     | 0b101 0000               | 0bxxx xx00              |

| EEPROM | 01     | 0b101 0001               | 0bxxx xx01              |

|        | 10     | 0b101 0010               | 0bxxx xx10              |

|        | 11     | 0b101 0011               | 0bxxx xx11              |

|        | GA[01] | I2C Address              | I2C Addresses           |

|        |        | for serial               | for <b>Optional</b>     |

|        |        | 32Kb                     | Devices                 |

|        |        | EEPROM                   |                         |

| 32Kb   | 00     | 0b101 0100               | 0bxxx xx00              |

| EEPROM | 01     | 0b101 0101               | 0bxxx xx01              |

|        | 10     | 0b101 0110               | 0bxxx xx10              |

|        | 11     | 0b101 0111               | 0bxxx xx11              |

|                     | GA[01] | I2C Address for thermometer #1 | I2C Address for thermometer #2 |

|---------------------|--------|--------------------------------|--------------------------------|

| I2C                 | 00     | 0b100 10 <mark>00</mark>       | 0b100 11 <mark>00</mark>       |

| thermometer<br>i.e. | 01     | 0b100 10 <mark>01</mark>       | 0b100 11 <mark>01</mark>       |

| MAX6626             | 10     | 0b100 10 <mark>10</mark>       | 0b100 11 <mark>10</mark>       |

| LM75<br>MCP980      | 11     | 0b100 10 <mark>11</mark>       | 0b100 11 <mark>11</mark>       |

## **Temperature Sensors (4)**

- TMP75 standard I2C thermometer

- 8 thermometers possible on a single bus, 2 on FMC module

- More is also possible, do we need?

- Implemented as dynamic sensors

|         |      |    |         |                     | GA[01]   | I2C Address for thermometer #1 | I2C Address for<br>thermometer #2 |

|---------|------|----|---------|---------------------|----------|--------------------------------|-----------------------------------|

| SDA 1   | 8 V+ |    |         | I2C                 | 00       | 0b100 10 <mark>00</mark>       | 0b100 11 <mark>00</mark>          |

| SCL 2   | 7 A0 |    | 1       | thermometer<br>i.e. | 10       | 0b100 10 <mark>01</mark>       | 0b100 11 <mark>01</mark>          |

| ALERT 3 | 6 A1 |    |         | MAX6626             | 01       | 0b100 10 <mark>10</mark>       | 0b100 11 <mark>10</mark>          |

| GND 4   | 5 A2 |    |         | LM75<br>MCP980      | 11       | 0b100 10 <mark>11</mark>       | 0b100 11 <mark>11</mark>          |

| A2      | A1   | A0 |         |                     | SLAVE AD | DRESS                          |                                   |

| 0       | 0    | 0  |         |                     | 10010    | 000                            |                                   |

| 0       | 0    | 1  | 1001001 |                     |          |                                |                                   |

|         |      | -  |         |                     |          |                                |                                   |

| 0 0 1 1001001 |  |

|---------------|--|

| 0 1 0 1001010 |  |

| 0 1 1 1001011 |  |

| 1 0 0 1001100 |  |

| 1 0 1 1001101 |  |

| 1 1 0 1001110 |  |

| 1 1 1 1001111 |  |

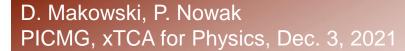

# VITA 57.4 (FMC+) Specification

#### 18/25

#### VITA 57.4 – Important Signals

- **SCL** System Management I2C serial clock. This signal provides a clock reference to the FMC+ module from the carrier card for a two-wire serial management bus.

- **SDA** System Management I2C serial data. This signal provides a data line for a two-wire serial management bus.

- GA[0..1] These signals provide geographical addresses of the module(s) and are used for I2C channel

- **PRSNT\_M2C\_L** Module present signal. The ANSI/VITA-57.1 FMC standard defines this signal for a carrier card to successfully detect that an IO mezzanine module is installed.

- **HSPC\_PRSNT\_M2C\_L** Module present signal. This signal allows the carrier to determine whether an FMC+ module is present.

- **HSPCe\_PRSNT\_M2C\_L** Module with HSPC and HSPCe connector present signal. This signal allows the carrier to determine whether an FMC+ module with optional HSPCe is present.

CLK\_DIR – Used to determine whether the mezzanine module or the carrier card is the driver for CLK[2..3].

**PG\_C2M** – Power Good Carrier Card. This signal asserts high by the carrier card when power supplies

VADJ, 12P0V, 3P3V are within tolerance.

**PG\_M2C** – Power Good Mezzanine. This signal asserts high by the mezzanine module when power supplies VIO\_B\_M2C, VREF\_A\_M2C, VREF\_B\_M2C are within tolerance.

## VITA 57.4 – IPMI Subtype 0 Record

- New Subtype 0 Record proposed

- The same EEPROM addresses, size and type

- Same address of thermometers

- Same additional signals required (HSPC\_PRSNT\_M2C\_L, HSPCe\_PRSNT\_M2C\_L)

|                                     |                | <b>D</b> ''     |        |                                                                                                                   |

|-------------------------------------|----------------|-----------------|--------|-------------------------------------------------------------------------------------------------------------------|

| Field                               | Byte<br>Offset | Bit<br>Location | Length | Description                                                                                                       |

| Subtype                             | 0              | 7:4             | 4 bits | 0b0000 for main definition type                                                                                   |

| Version                             | 0              | 3:0             | 4 bits | 0b0001 for FMC+<br>(see Observations in Section 5.3.1)                                                            |

| Module Size                         | 1              | 7:6             | 2 bits | 0b00 = single width,<br>0b01 = double width                                                                       |

| P1/P3 Connector<br>Size             | 1              | 5:4             | 2 bits | 0b00 = LPC only,<br>0b01 = HPC only,<br>0b10 = HSPC only,<br>0b11 = P1:HSPC + P3:HSPCe                            |

| P2/P4 Connector<br>Size             | 1              | 3:1             | 3 bits | 0b000 = LPC only,<br>0b001 = HPC only,<br>0b010 = HSPC only,<br>0b011 = P2:HSPC + P4:HSPCe,<br>0b111 = not fitted |

| Clock Direction                     | 1              | 0               | 1 bit  | Defines direction of CLKx_BIDIR<br>0b0 = from Mezzanine to Carrier<br>0b1 = from Carrier to Mezzanine             |

| P1 Bank A<br>Number Signals         | 2              | 7:0             | 8 bits | = number needed                                                                                                   |

| P2 Bank A<br>Number Signals         | 3              | 7:0             | 8 bits | = number needed                                                                                                   |

| P1 Bank B<br>Number Signals         | 4              | 5:0             | 6 bits | = number needed                                                                                                   |

| P2 Bank B<br>Number<br>Signals[1:0] | 4              | 7:6             | 2 bits | = number needed                                                                                                   |

| P2 Bank B<br>Number<br>Signals[5:2] | 5              | 3:0             | 4 bits | = number needed                                                                                                   |

| P1 GBT Number<br>Transceivers[3:0]  | 5              | 7:4             | 4 bits | = number needed                                                                                                   |

| P1 GBT Number<br>Transceivers[5:4]  | 6              | 1:0             | 2 bits | = number needed                                                                                                   |

| P2 GBT Number<br>Transceivers       | 6              | 7:2             | 6 bits | = number needed                                                                                                   |

| Max Clock for<br>TCK                | 7              | 7:0             | 8 bits | = clock in MHz                                                                                                    |

#### Possible IPMI Support for FMC modules on MTCA.4 systems

#### **FMC FRU content**

#### **Board info and Product info:**

Information about board name, manufacturer, serial number, part number FRU\_ID,.

|                  | : at offs=264, len=21<br>: DMCS<br>: FMC_LB<br>: 0000<br>: 0000<br>: LB_F               |

|------------------|-----------------------------------------------------------------------------------------|

| Manufacturer(04) | : at offs=285, len=90<br>: DMCS<br>: FMC_LB<br>: 00<br>: 000000000000000000000000000000 |

#### 21/25

#### **Possible IPMI Support for FMC modules on MTCA.4 systems**

#### FMC FRU content:

#### MultiRecord Area (single-width module)

#### DC Load/Output Records (Min, Nominal, Max voltage):

VADJ (Most important), 3P3V, 12P0V, VIO\_B\_M2C,

VREF\_A\_M2C, VREF\_B\_M2C

#### FMC unique info:

Module width, Connector type, number of used I/Os per bank, number of GBT Transceivers, Max clock for TCK

Multirecord Area: Record Checksum OK Record Checksum OK FMC unique record -subtype 7 --version 3 --modulesize Single-width ---P1ConnSize LPC ---P2ConnSize None ---P1Bank\_A\_NumberSignals 21 ---P1Bank\_B\_NumberSignals 0 ---P2Bank\_A\_Numbersignals 0 ---P2Bank\_B\_NumberSignals 0 ---P1\_GBT\_Number 0x0 ---P2\_GBT\_Number 0x0 --MaxClockForTCK 10 MHz

Multirecord Area: Record Checksum OK Record Checksum OK DC LOAD record: -Output P1\_VADJ -Nominal Voltage 2.5V --Max Neg Voltage 2.4V -Min Neg Voltage 2.6V -Minimal Current 10mA -Maximal Current 100mA Multirecord Area: Record Checksum OK Record Checksum OK DC LOAD record: --Output P1\_3P3V -Nominal Voltage 0.0V --Max Neg Voltage 0.0V --Min Neg Voltage 0.0V -Minimal Current OmA -Maximal Current OmA Multirecord Area: Record Checksum OK Record Checksum OK DC LOAD record: ---Output P1\_12POV -Nominal Voltage 12.0V -Max Neg Voltage 11.0V -Min Neg Voltage 13.0V -Minimal Current 10mA Maximal Current 500mA

22/25

#### **First Implementation in Hardware**

- Simple test implementation of IPMI support for FMC module on HVC-50 AMC board

- Special MMC firmware tricks MCH into thinking that connected FMC module is RTM

#### **First Implementation in Hardware**

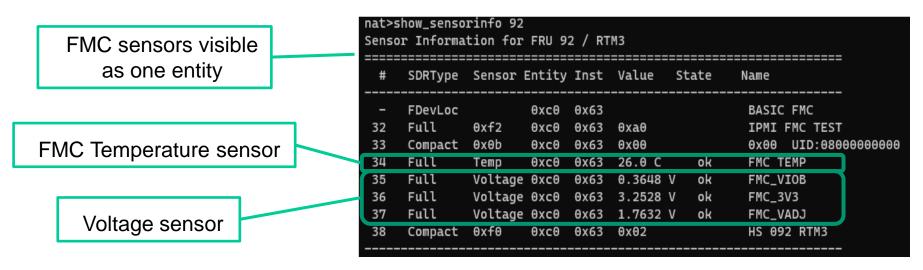

- MMC provides FRU and sensors from FMC to MCH

- MCH reads FMC FRU and displays created sensors

- System can read temperature of FMC module and enable fans if it will be required

FMC Sensor Information in MCH

## Summary

- Support for 4 FMC modules on a single AMC/RTM pair is feasible

- Update of MTCA.4.1 including the latest VITA 57.X revisions is required

- Single FRU and up to 2-3 sensors could be easily obtained

- Support from MCH is need for additional FRUs: 2-3, and

- 4-5 if we decide (but full MTCA.4 chassis could have 48 FRUs more)

# Thank you for your attention