# Hybrids – where the trouble meets or: walking the critical path

Katja Klein 1. Physikalisches Institut B, RWTH Aachen

14th Terascale Detector Workshop 24th of February, 2022

### Outline

- What are hybrids?

- Examples of hybrids

- Example 1: front-end hybrids

- for CMS Outer Tracker 2S modules

- Example 2: service hybrids

- Example 3: ATLAS hybrids for ITk strip modules

- Selected challenges

- Problem 1: challenging PCB specifications

- Problem 2: lamination and fold-overs

- Problem 3: number of variants

- Problem 4: external dependencies

- Problem 5: system issues

- Problem 6: limited market

- Problem 7: total volume

- Problem 8: quality assurance

- Problem 9: procurement

- Problem 10: schedule

- Conclusions

Focus mainly on CMS tracker hybrids, some informations on ATLAS ITk hybrids (thanks to Dennis Sperlich!)

### What are Hybrids?

#### Hybrid integrated circuit

From Wikipedia, the free encyclopedia

A hybrid integrated circuit (HIC), hybrid microcircuit, hybrid circuit or simply hybrid is a miniaturized electronic circuit constructed of individual devices, such as semiconductor devices (e.g. transistors, diodes or monolithic ICs) and passive components (e.g. resistors, inductors, transformers, and capacitors), bonded to a substrate or printed circuit board (PCB).<sup>[1]</sup> A PCB having components on a Printed Wiring Board (PWB) is not considered a true hybrid circuit according to the definition of MIL-PRF-38534.

- In particle physics, in particular trackers, we usually mean

- a multi-layer Printed Ciruit Board (PCB)

- typically with high line density ("High Density Interconnect", HDI)

- often being flexible ("flex") or flex-rigid

- carrying passive components (resistors, capacitors, connectors, ...)

- and active components (readout chips, power chips, ...)

- typically also integrating mechanical components (e.g. laminated onto a stiffener)

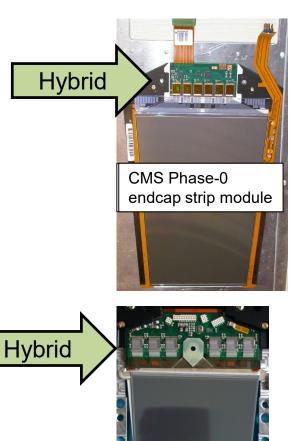

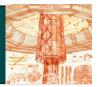

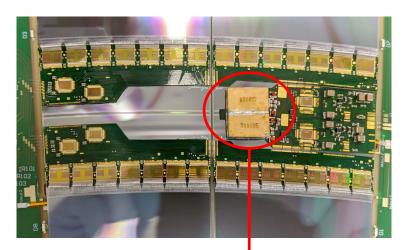

### Example 1: CMS Outer Tracker 2S Front-End Hybrid

• Strip-strip (2S) sensor module, for r > 60cm

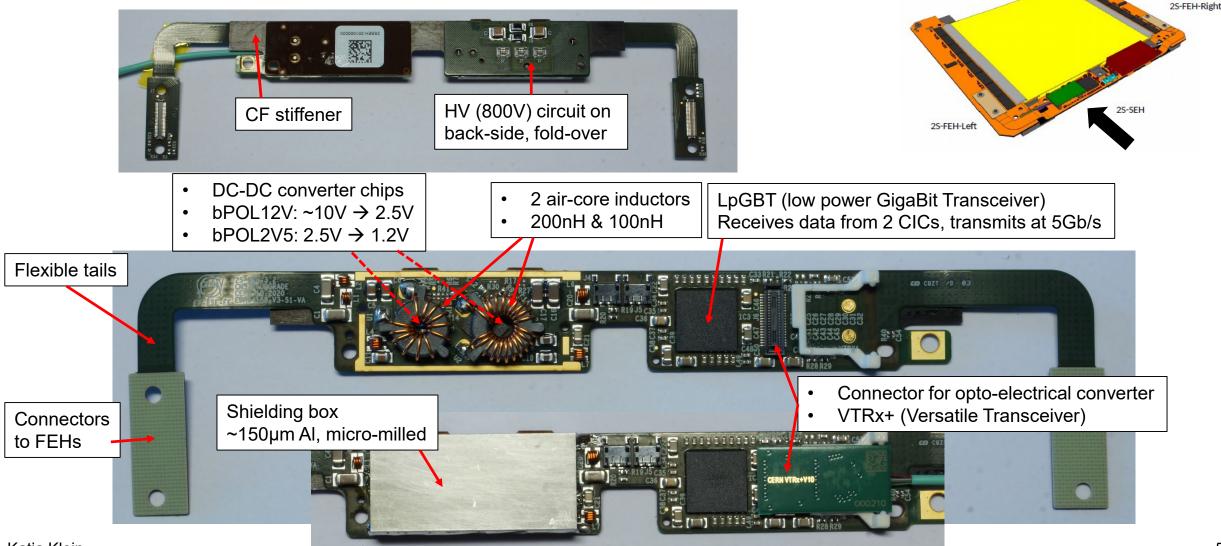

## Example 2: CMS Outer Tracker 2S Service Hybrid

• Strip-strip (2S) sensor module, for r > 60cm

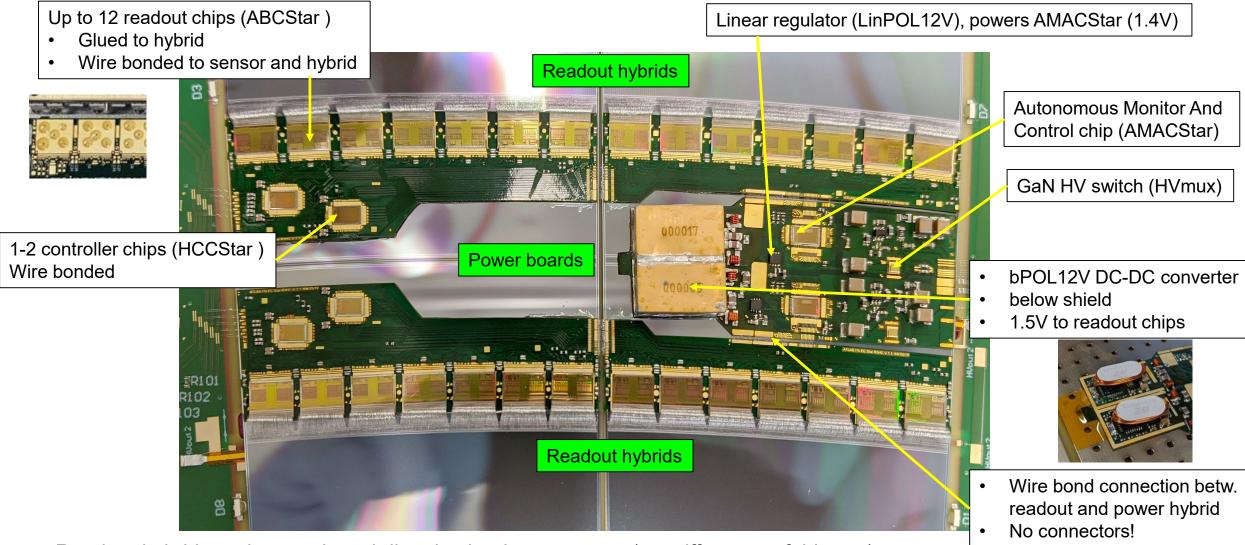

### Ex. 3/4: ATLAS Strip Tracker Readout & Power Hybrids

Readout hybrids and power board directly glued onto sensor (no stiffener, no fold-over)

Katja Klein

- Typical specifications from CMS; ATLAS ("A") hybrids are less demanding:

- 4-5 (A: 4) copper layers, with thickness of 9-12μm for inner layers and 12-23.1μm for outer layers (A: ~25μm)

- Line density: track width and spacing down to 45µm / 45µm (A: 75µm / 100µm)

- Micro-vias (contacts between layers): laser-drilled and copper-filled with drill diameter down to 25-50µm (A: 100µm) and 110µm pads

- Solder mask registration error < 20µm in x and y

- High speed differential pairs with  $90\Omega \pm 10\%$

- Thickness uniformity: thickness between ±10% of mean (A: ±40µm)

- Flatness: bow < 200µm wrt flat table

- Wire bond pads (e.g. 120µm x 300µm) with tolerance +10µm and -5µm

- Bump bond pads with 250µm pitch

- Tight **bend** with ~500µm bending radius

Soldermask 20 µm MAX

Top Copper 12 µm to 23 µm

Blind Via

Polyimide 12 µm

Adhesive 12 µm MIN 15 µm MAX

L3 Copper 12 µm MAX

Buried Via

Polyimide 25 µm

L2 Copper 12 µm MAX

Blind Via

Polyimide 25 µm

Blind Via

Polyimide 12 µm MAX

Blind Via

Polyimide 12 µm MAX

Soldermask 20 µm MAX

Blind Via

. . . . .

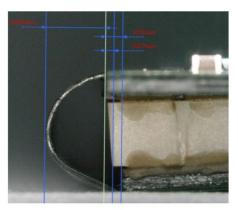

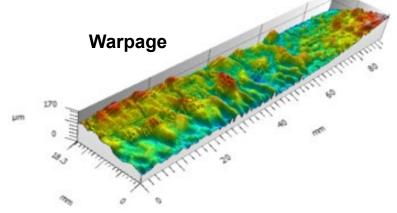

#### **Problem 2: Lamination**

Bow

- CMS hybrids need to **be laminated** (= glued) onto a **carbon fiber stiffener**

- Wire and/or bump bonding → assembly needs to be flat → no bow, no warpage, no delamination!

- Hard glue resulted in bow due to CTE<sup>1</sup> mismatch between CF and flex board

- Soft glue resulted in warpage due to insufficient adherence

- Systematic and lengthy R&D campaign launched

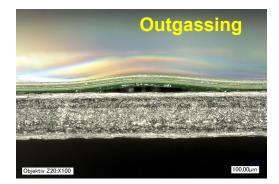

- Outgassing of CF during reflow → CF needs special treatment: post-curing at 185°C and sand scrubbing

- Bow can be eliminated with "CTE compensator layer" on back side of CF stiffener (fiberglass reinforced polyimide foil)

- Assembly stays flat, but flex circuit is stretched  $\rightarrow$  compensation in layout or solder stencil

- Different companies chose different solutions, partly still a concern today

Katja Klein

#### Compensator (bubbles from outgasing)

<sup>1</sup>CTE = coefficient of thermal expansion

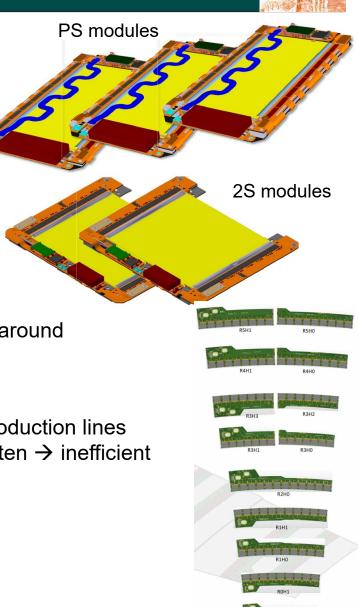

### **Problem 3: "Zoo" of Variants**

#### ATLAS has 20 variants

- Barrel: 2 readout hybrids and 1 power board

- Endcap: 13 readout hybrids and 4 power boards

- CMS has 15 variants (and we do not even have endcap modules!)

- 5 types: 2S FEH, PS FEH, 2S SEH, PS Power Hybrid, PS Readout Hybrid

- Left and right sides, and 2 (3) sensor spacings in 2S (PS) modules

#### Consequences:

- Design changes to be propagated to many variants → tedious and slow design turnaround

- All variants need to be prototyped and tested → expensive, time consuming

- Manufacturing jigs at companies, test equipment etc. needed for all variants

- All variants must be produced in parallel during mass production, to feed module production lines and to enable integration → companies need to switch between variant/type very often → inefficient

#### **Problem 4: External Dependencies**

- Dependency on active components, partly from the experiment, partly common projects by CERN electronics:

- E.g. 2S module: CBC, CIC, LpGBT, VTRx+, bPOL12V, bPOL2V5

- Final versions of many chips still not available today or just very recently

- Early prototypes had to use pre-decessors (GBT, VTRx, FEAST DC-DC) and even commercial DC-DC chips

→ Performance not necessarily fully representative of final components! (see later)

- → Very significant re-design needed for final chips (different chip pinout, size, package, routing (ABCStar) etc.)

- Dependency on DAQ firmware and software

- Development is a R&D project also and proceeds in parallel  $\rightarrow$  bugs, missing functionalities, instabilities....

- Dependency on module design, assembly, performance (and even sub-structures)

- Module assembly and testing follows hybrid prototyping with considerable delay  $\rightarrow$  feedback comes late

- Examples: flexible tails too stiff, noise issues ....

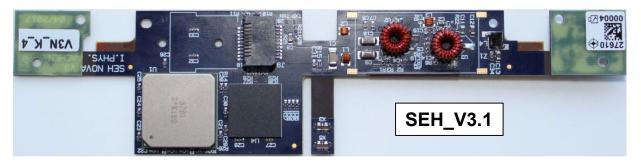

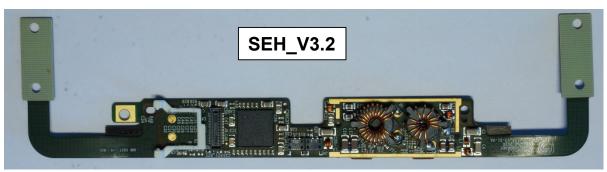

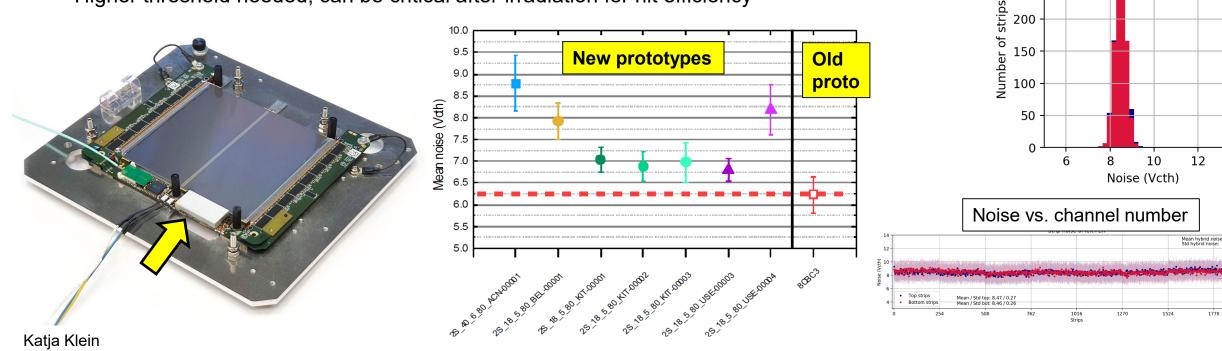

#### Problem 5: System Issues | CMS

- 2S modules carry 2 DC-DC converters, in a two step scheme

- Switching noise, radiated and conducted → filtering of output voltages and electro-magnetic shielding

- Early prototype modules (FEAST, commercial DC-DC) showed excellent noise behaviour

- Recent modules (bPOL12V, bPOL2V5) show up to 30% higher noise!

- Noise increased on all channels, flat noise distribution

- Higher threshold needed, can be critical after irradiation for hit efficiency

14

Noise histogram

300

250

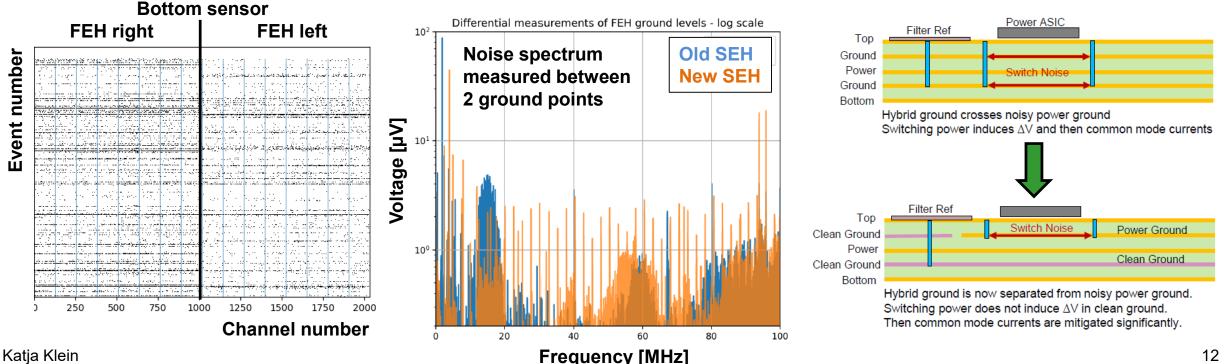

#### Problem 5: System Issues | CMS

- Strong indications for **common mode noise**

- Dozens of **grounding variations** tried improvement insufficient and difficult to implement .

- Different biasing and powering schemes investigated  $\rightarrow$  bypassing DC-DC converters restores noise level!

- **Higher harmonics in noise spectrum** more pronounced then in earlier SEH version

- Investigations on coupling mechanism still ongoing

- Changes on hybrid level under discussion, e.g. introduction of a "clean ground" in SEH

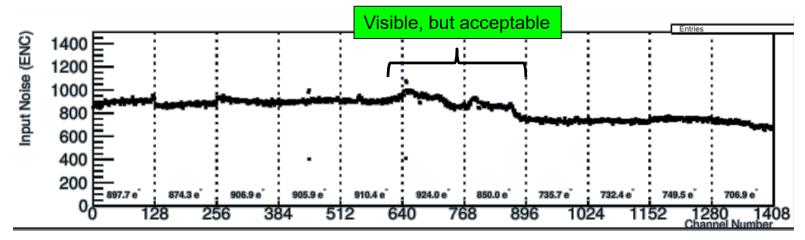

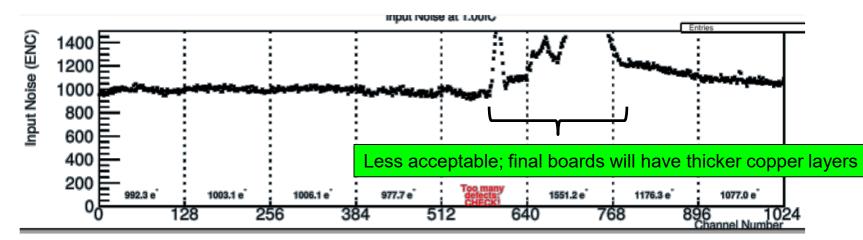

#### Problem 5: System Issues | ATLAS

- Noise increase observed below DC-DC converter

- Depends on details: orientation of the coil, copper thickness

- Mostly acceptable, to be checked with final power boards

DC-DC converter sits on top of the sensor (example picture, module not used for the plots)

#### **Problem 6: Limited Market**

- For state of the art hybrids as needed in CMS, the market is very limited (and the companies know!)

- A lot of steps that are **non-standard in industry**

- Lamination to carbon fiber stiffeners, fold-over

- Many manual steps

- Usually two companies involved flex manufacturer and assembly company

- Flex manufacturer: ~ 3-4 companies (3 in Switzerland; all mid-sized at least the core site)

- Assembler: comparable number, but less well defined set

- Little competition  $\rightarrow$  high prices

- Even the best companies struggle with the specialized and complicated processes

- Prototyping phase to gain experience and to "qualify" → very difficult to change horses

#### **Problem 7: Total Volume**

- CMS (ATLAS) needs in total ~ **45 000 (50 000) hybrids**

- Estimated peak rate during CMS series production: ~2500 hybrids / month → 125 hybrids / day

- Puts demanding requirements on **production capacity** of PCB manufacturer and especially of assembler

- Very challenging for quality assurance (QA) at company and in the experiment → very high throughput needed

- High pressure to provide feedback to companies quickly enough to stop production in case of serious problems

- For illustration: any task taking 1 minute / hybrid (e.g. packaging) leads to 31 days or 94 8-hour shifts

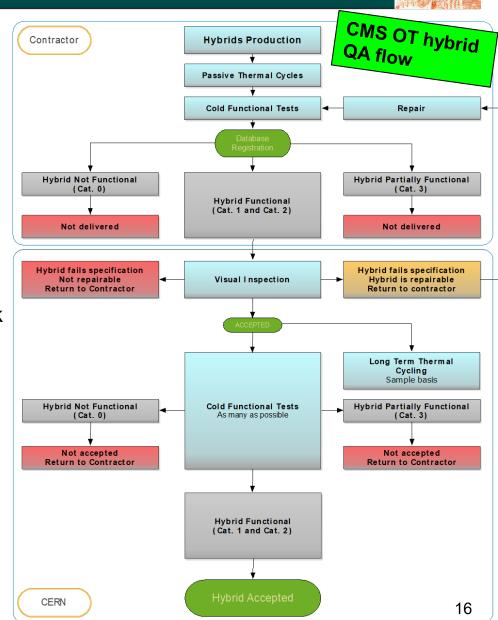

#### **Problem 8: Quality Assurance (QA)**

- QA is a significant challenge:

- **Completeness**: spot production issues, reliability issues, performance issues

- High throughput: quick feedback for production, large quantities to handle (~2500 hybrids / month)

- Two main pillars:

- Visual inspection under a microscope for every hybrid time and man power intense

- Functional testing technically complicated, many aspects to check

- QA happens at two places:

- At the contractor includes X-rays, passive thermal cycling

- In the collaboration distributed or centrally (CMS: mainly CERN)

- Development of test procedures and test systems is a major task

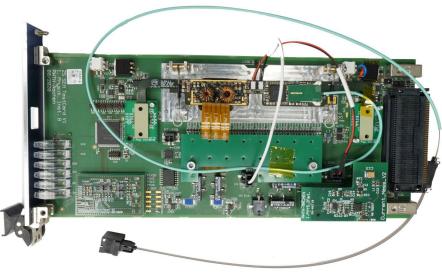

#### **Problem 8: Quality Assurance (QA)**

- CMS has developed a crate-based multiplexed test system, to be used at the companies and in the collaboration

- Each main hybrid type has its own test card: 5 complex test cards needed

- Test data lines, clock, resets, slow control, I2C, low and high voltage ...

- ATLAS has a conceptually similar system, but needs to wire bond to test cards

- Crates will be operated in **climatic chamber**, at room temperature and at -35°C

- Cards must survive temperature & plugging cycles → dedicated test campaign

Considerable development, mainly on the shoulders of the hybrids teams

- Needs to run stably and be usable by a non-expert → GUI needed

- Per hybrid ~1-6 min testing and ~2-4 min mounting + unmounting

- 125 hybrids / day  $\rightarrow$  8h / day spend just on mounting + unmounting!

#### 5 test

ATLAS test system for power boards

#### **Problem 9: Procurement**

- General CMS considerations:

- Consortia of assembly company (=our contract partner) and flex manufacturer  $\rightarrow$  avoid ping-pong between companies

- Work with suitable companies from the beginning and qualify them during prototyping

- At least two consortia during mass production to avoid risk of single source (and share volume)

- CERN procurement rules demand an "Invitation to Tender" for > 200 kSFr (easily fulfilled), preceded by market survey

- CMS did a market survey in 2012-2016

- 42 companies invited, 17 companies answered, 3 companies qualified one of them declined later  $\rightarrow$  2 left

- Invitation to Tender is being prepared

- Fully open since market survey has expired (!), everybody can bid  $\rightarrow$  eligibility critera to be carefully formulated

- 160 pages Technical Specification document

- Specifies whole project, including QA, acceptance criteria, documentation, ...

- A mistake or oversight can cost money or time

#### **Problem 10: Schedule**

- Hybrids are usually accumulating delays:

- Hybrids are at the end of a food chain: delays in chip development and prototyping propagate directly

- Technical issues, production-related issues, failed batches etc. happen and cannot (all) be anticipated

- Last component where changes are still possible when sensors and chips already in production

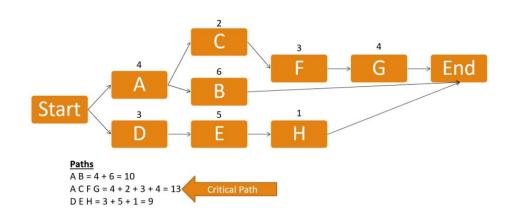

- "Critical path" = series of tasks that drive the schedule if not finished on time the whole project cannot finish on schedule

- The critical path usually moves from ASICs to hybrids [to modules] to integration

- It is normal and almost unavoidable that the hybrids are on the critical path for a significant time, up to almost the end of hybrid production

- A lot of other projects can happily sail in the shadow

#### Conclusions

- In silicon modules, sensors and ASICs receive most attention

- While hybrids are "just interconnects" they enable state of the art silicon modules

- Hybrid design and production are highly challenging

- Troubles with hybrid production have been experienced in many past tracker projects

- Also today it is a continuous struggle

- ATLAS and CMS tracker hybrids for Phase-0 have worked very well

- It's a long run, but I am confident that we will again succeed