Tomasz Jezynski for the LLRF - Team

- Background & PICMG xTCA for Physics Initiative

- LLRF system for EU-XFEL

- xTCA Crate

- Boards Development@DESY & Industry Developments to new Physics Standards

- Summary Conclusions

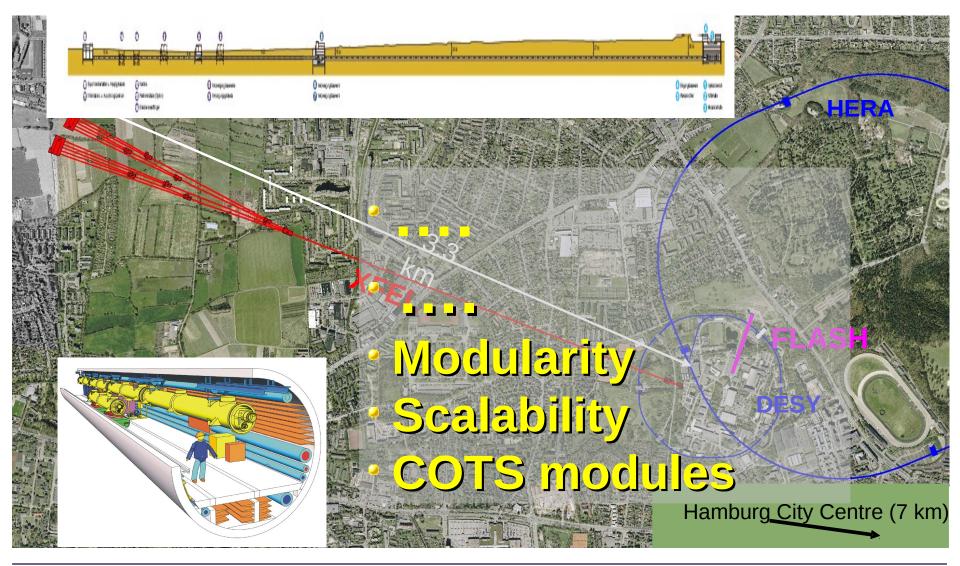

European XFEL

### **Background & PICMG xTCA for Physics Initiative**

## <u>SLAC</u>

- ILC Snowmass 2005

- Proposed ATCA as model for ILC controls and beamline instrumentation systems (85% uptime is required) R&D programs at SLAC for I&C, magnet power supply systems, modulators, etc.

### <u>DESY</u>

Proposals for ATCA (LLRF) and  $\mu\text{TCA}$  (Tunnel Controls) under XFEL

## **XFEL** Background & PICMG xTCA for Physics Initiative

- ATCA Workshops: FNAL 2007 and Dresden 2008

- Formation of new PICMG standards collaboration for Physics May 09

#### <u>Lab members</u>

- Founding Members: DESY, FNAL, IHEP, SLAC

- Additional Lab Members: IPFN Lisbon, ITER, CERN

#### Industry Members

Founding Members: Cypress Point Systems, Performance Technologies, Triple Ring Technologies Additional Members: ~43 companies total

#### Working Groups:

- Hardware Committee

- Software Committee

## **Background & PICMG xTCA for Physics Initiative**

## Micro TCA<sup>TM</sup>

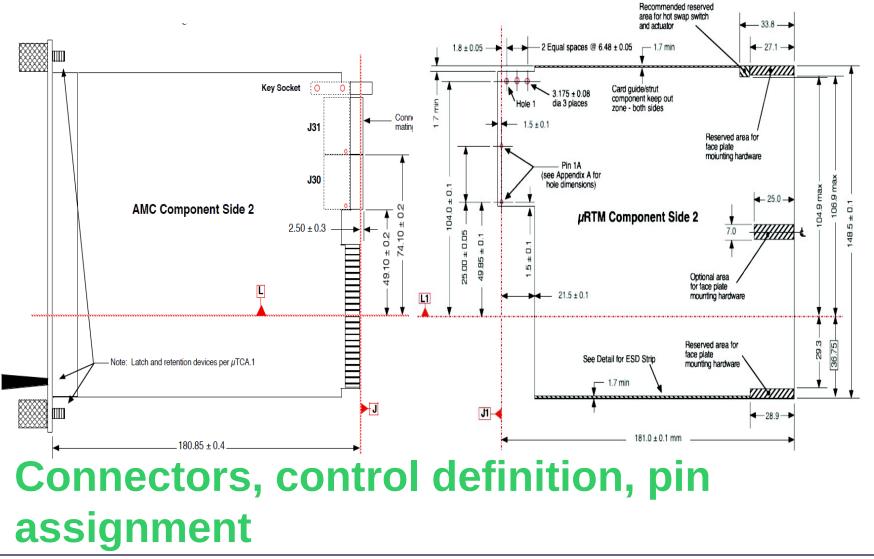

#### PICMG® Specification MTCA.4 R 1.0 Draft 0.9xh

#### MicroTCA Enhancements for Rear I/O and Precision Timing

14 July 2011

For Member Review Only - Do Not Claim Compliance To or Distribute This Draft Specification

Open Modular Computing Specifications

Advanced TCA®

PICMG<sup>®</sup> 3.8 Draft RC1.0 for Revision 1.0

#### AdvancedTCA Rear Transition Module Zone 3A

For Adoption Ballot only Do Not Claim Compliance To or Distribute this Draft Specification

26 July 2011

Open Modular Computing Specifications

### Background & PICMG xTCA for Physics Initiative

LLRF Workshop 2011, 18.10.11 Tomasz Jezynski, DESY

European

💽 🗰 🎼 🛞 🧖

HELMHOLTZ

ASSOCIATION

#### **Background & PICMG xTCA for Physics Initiative**

HELMHOLTZ

ASSOCIATION

(ISE)

System Architecture and Hardware Development for the LLRF System for EU-XFEL using  $\mu$ TCA.4

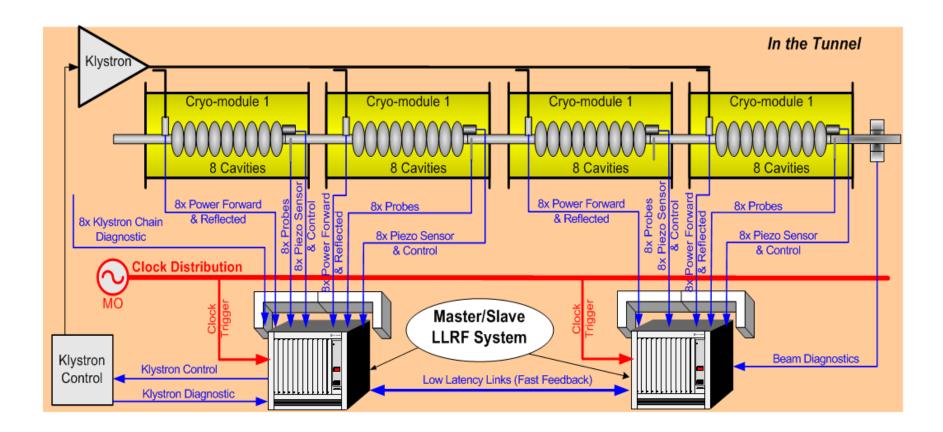

## **XFEL** LLRF Requirements and Motivation

## LLRF system for EU-XFEL

European

XFEL

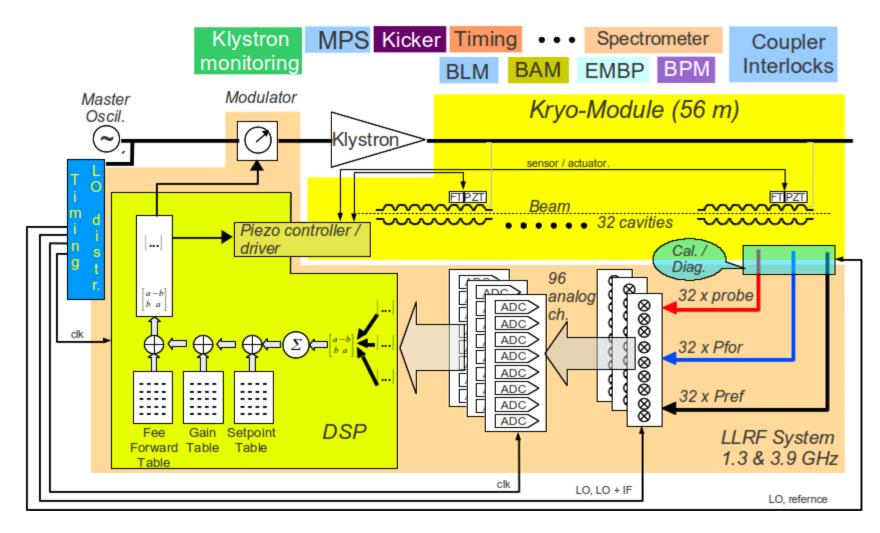

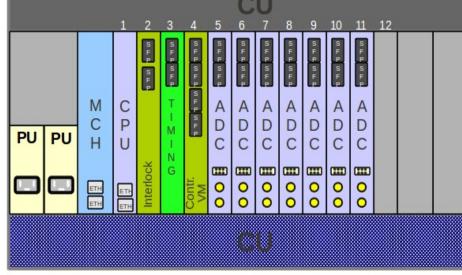

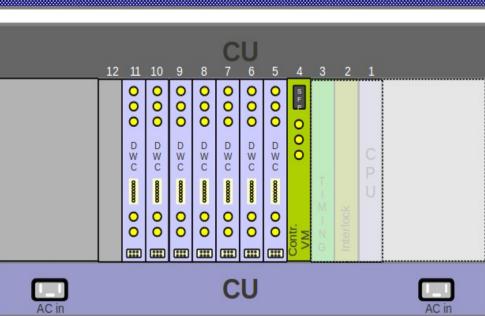

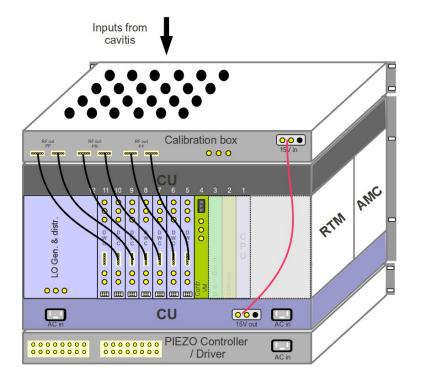

## Down-converters - RTM INTERLOCK (AMC + RTM)

- ADC AMC

- IQ DETECTORS

- MODULATOR (RTM)

- DSP (AMC)

- TIMING (AMC)

- MCH • CPU (AMC)

- POWER SUPPLY

- CRATE

European

XFE

LLRF system for EU-XFEL

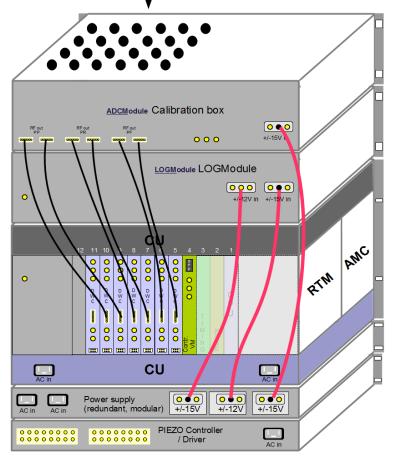

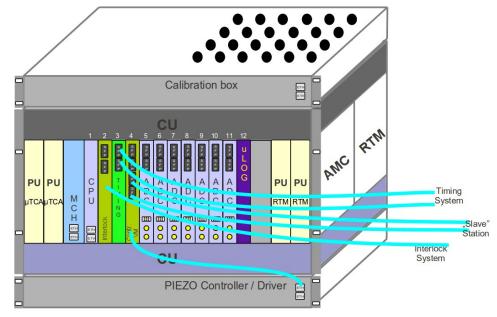

## **XFEL** LLRF system for EU-XFEL

# 12

## **XFEL** LLRF system for EU-XFEL

# Many RF cables for LO distribution

# Fibers between boards in the crate

LLRF Workshop 2011, 18.10.11 Tomasz Jezynski, DESY

RTM

Interlock

System

Timina

System

BBF

"Slave" Station

13

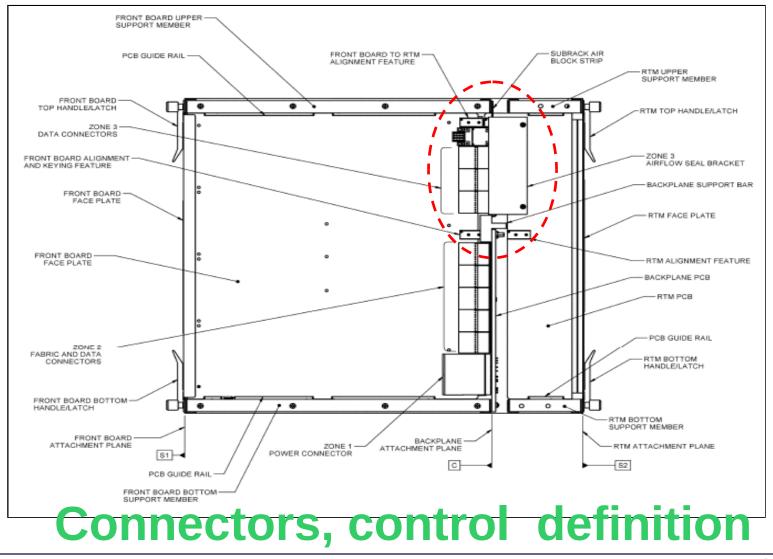

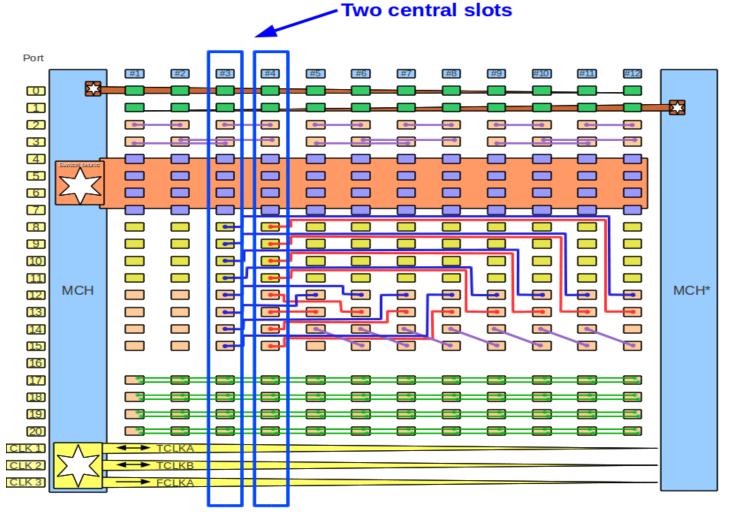

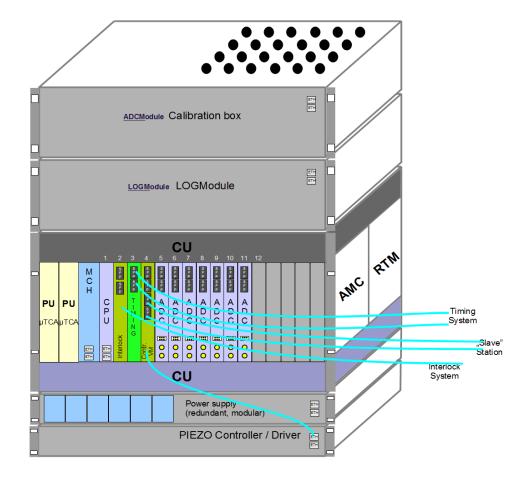

## **XFEL XTCA Crate - LLRF Backplane**

**Star configuration : Controller to IQ detectors**

LLRF Workshop 2011, 18.10.11 Tomasz Jezynski, DESY

HELMHOLTZ

14

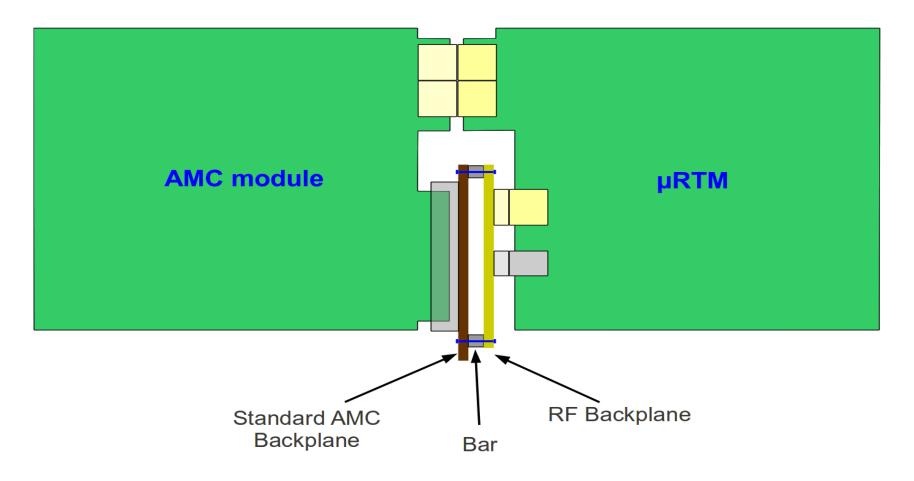

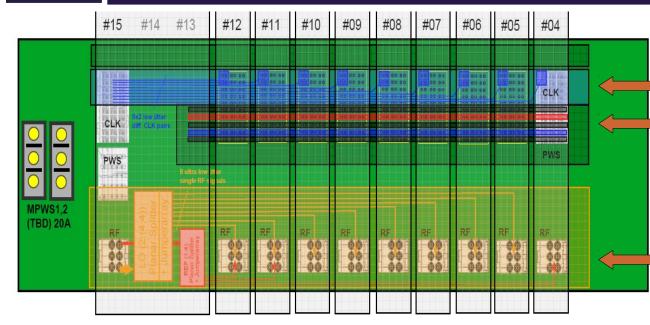

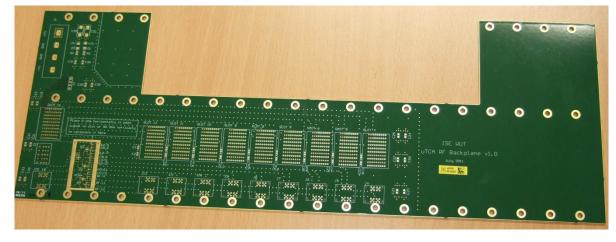

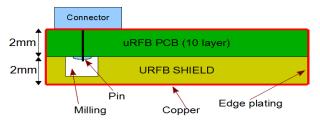

## **XFEL XTCA Crate – RF Backplane**

#### FRONT

REAR

## **XFEL XTCA Crate – RF backplane**

Low jitter clock distribution < 200fs (e.g. ADC-Clocks)

Independent redundant power supplies (e.g. +15V, -15V)

Low jitter RF-signals <10fs (e.g. LO-Distribution)

# 16

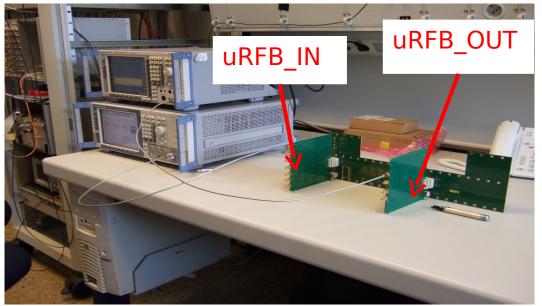

## **XFEL** RF Backplane Test Setup

#### <u>RF loss (worst case):</u>

- LO distribution, 14 dB (11.1 dB splitter)

- RF distribution, 9.6 dB (7.4 dB splitter)

<u>Clock jitter:</u> - 80-110fs (significant loss in uRFB\_IN test board)

#### <u>Crosstalks:</u>

- no crosstalk between RF and LO lines were observed on the level of -90 dB (measurement equipment limitation)

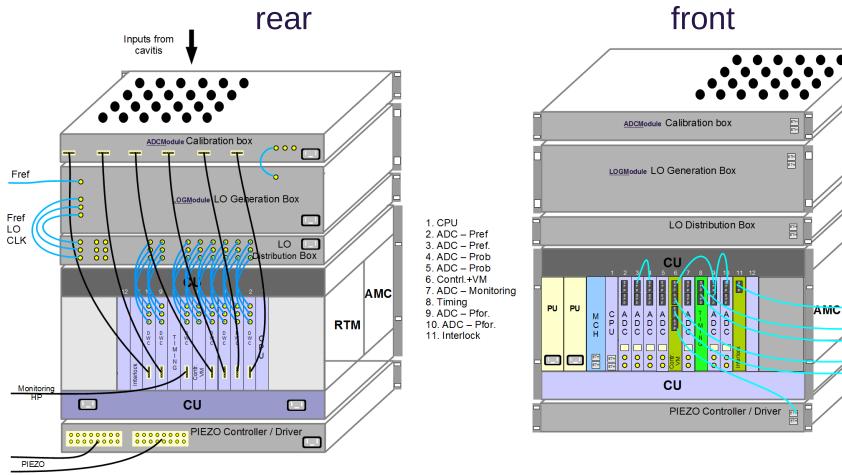

#### LLRF in xTCA Crate

Inputs from cavitis

European

rear

front

# **XFEL XTCA Crate – µLOG**

#### uLOG : RTM low jitter signal generation

LURFaWorkstopp200111,1301091111 FrankszudozignSkESDESY

18

# **XFEL** LLRF in xTCA Crate

front

#### rear

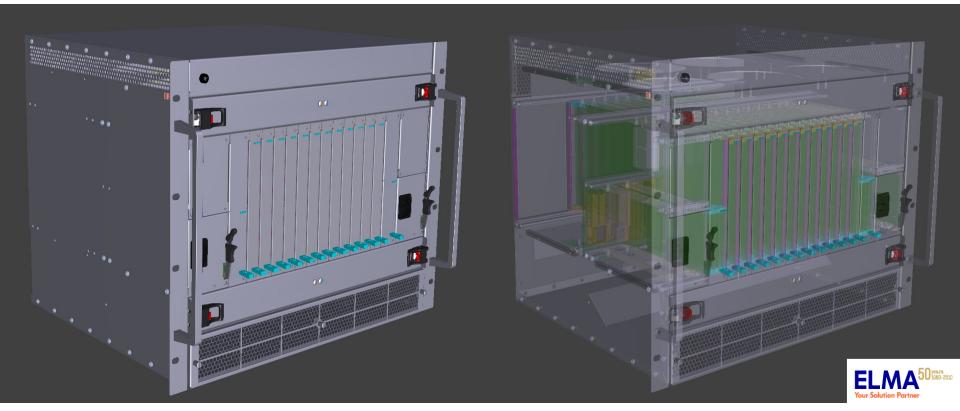

# XFEL XTCA Crate

Courtesy: ELMA

#### European XFEL

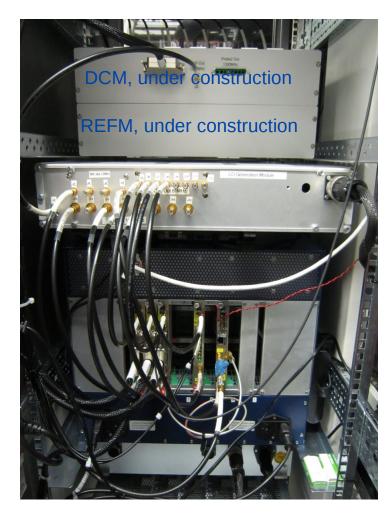

### Status 2011: FLASH injector prototype system

#### UTCA Prototype Front view

uTCA Prototype Rear view

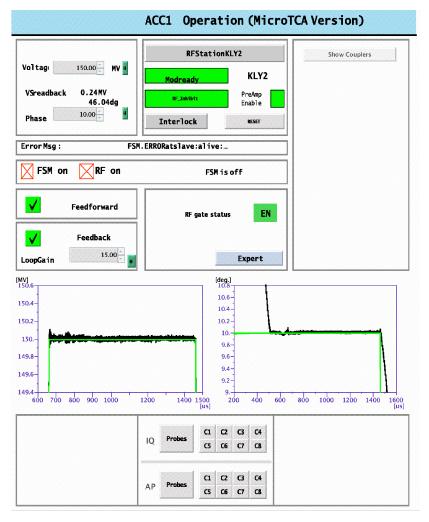

### **Beam operation using the uTCA-platform**

#### FLASH operation :

European

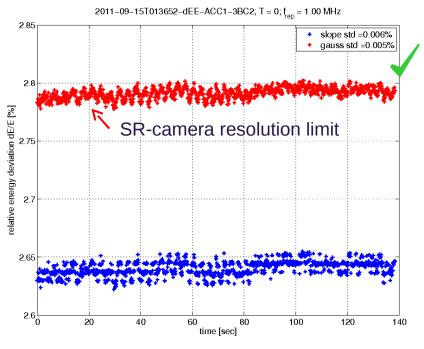

#### On-crest energy stability :

22

Energy stability dE/E=5E-5.

23

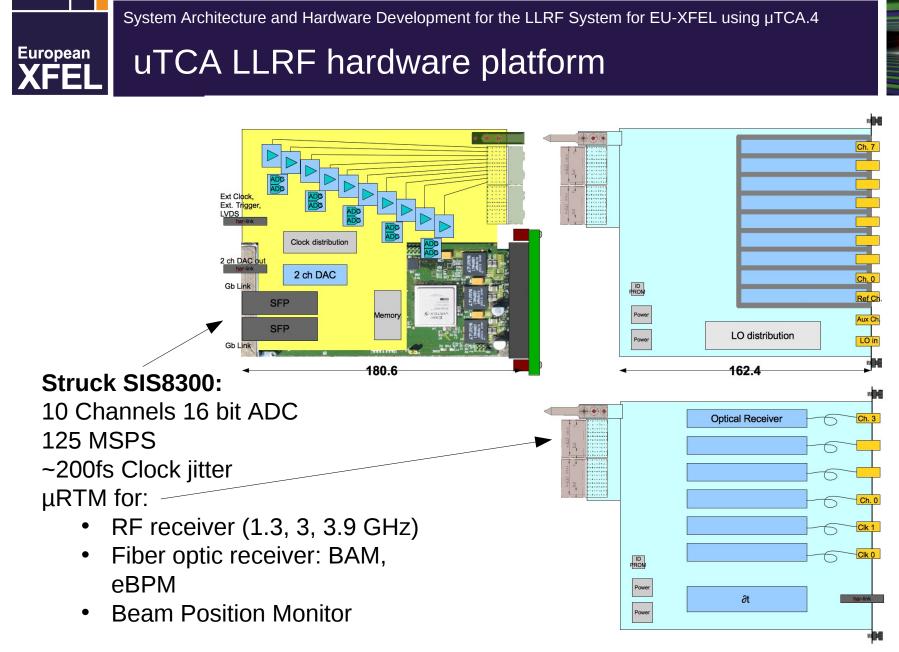

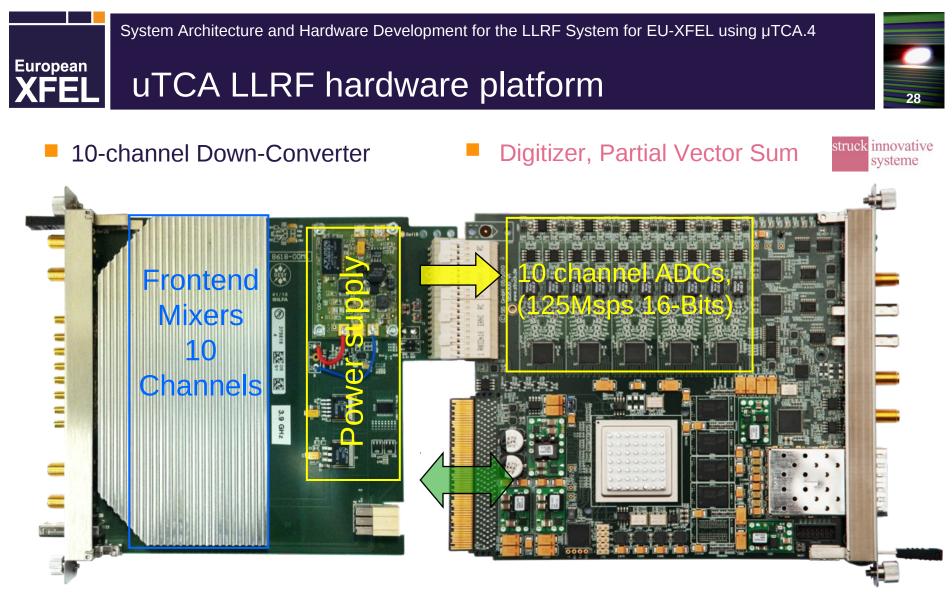

## uTCA LLRF hardware platform

## uTCA LLRF hardware platform

Clock and trigger OUT

Clock and data Fiber optic IN

Development of a ps stable timing system

- Clock, trigger, interlock and event distribution

- Fiber optic links (3.5 km), 1.3 GHz telegrams

- Goal: < 5 ps jitter, 1.54 ns trigger resolution</p>

- Drift compensation on ps level

European

System Architecture and Hardware Development for the LLRF System for EU-XFEL using  $\mu$ TCA.4

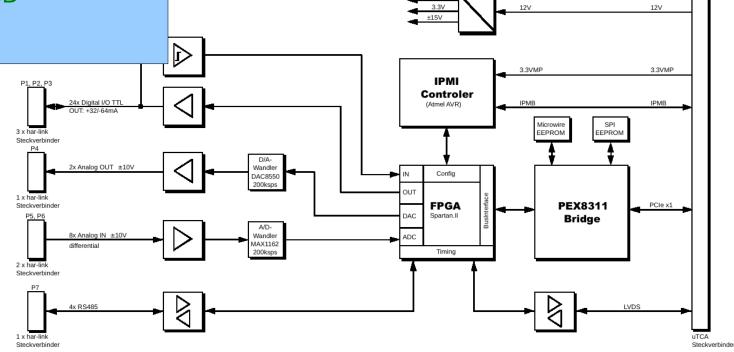

uTCA LLRF hardware platform

# . using μT

#### A,D I/O

European

- 8 ch ADC 200kHz

- 2ch DAC

- 24 I/O

- 4 RS485

- 1 lane PCle

#### Available from ESD

LLRF Workshop 2011, 18.10.11 Tomasz Jezynski, DESY

ASSOCIATION

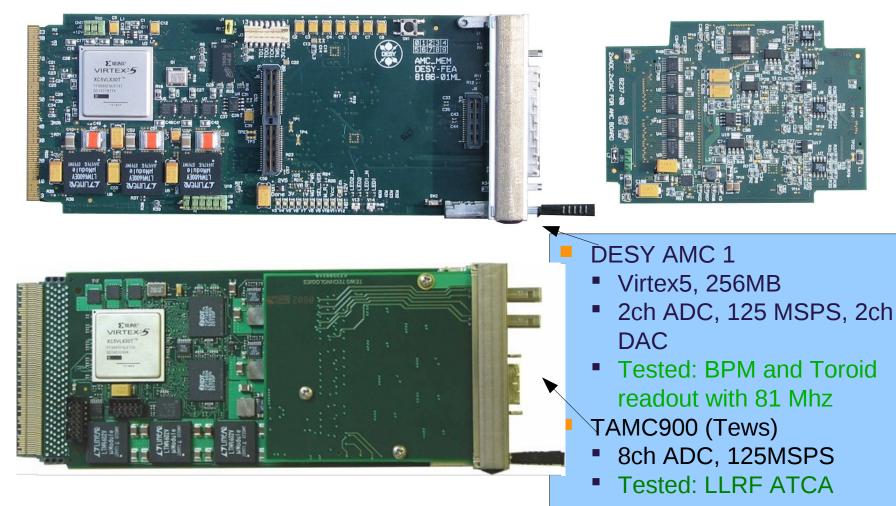

**XFEL** uTCA LLRF hardware platform

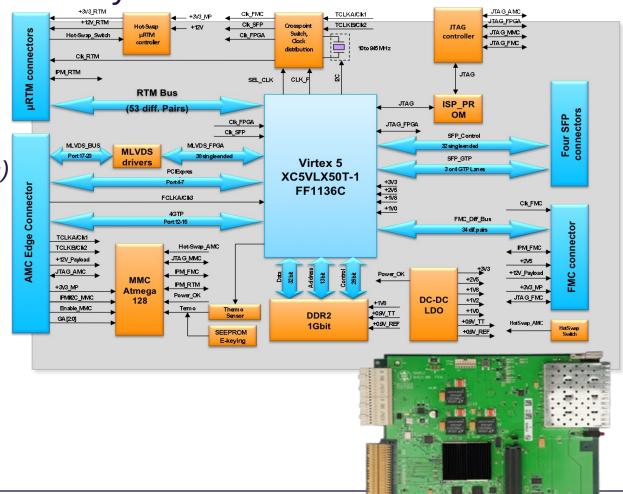

## Digital I/O AMC with a Virtex 5 FPGA, 4 fiber optical links, FMC slot, memory and clock distribution.

\* MPS

(Machine Protection System)

- \* Beam Loss Monitors

- \* Coupler Interlock

- \* Photo-diode readout

27

- 10 channel field detection (1.3GHz, 3.0GHz, 3.9GHz)

- 10 channel ADCs (125Msps, 16-Bits)

- FPGA partial cavity vector sum

- Low latency links via uTCA-backplane

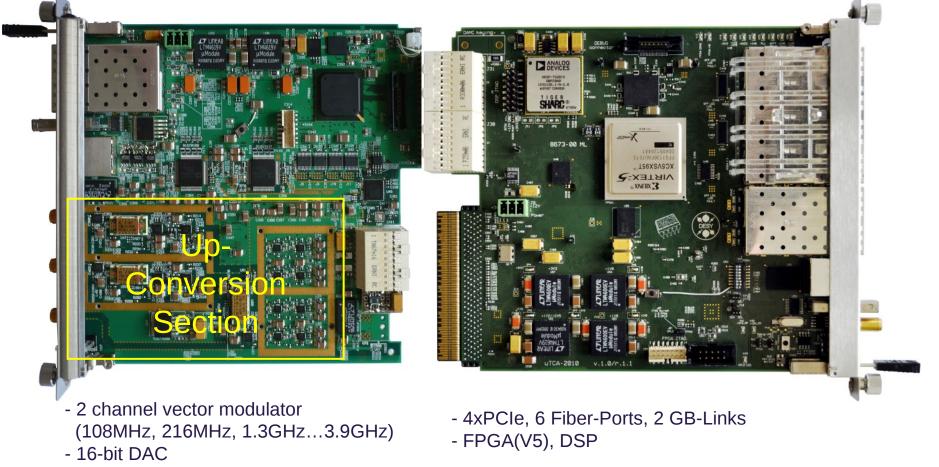

## uTCA LLRF hardware platform

#### Klystron Driver (VM)

#### μTCA Controller (μTC)

LLRF Workshop 2011, 18.10.11 Tomasz Jezynski, DESY

European

XFEI

### Prototype system has been successfully tested

- COTS modules available (almost)

- Big interest from industry partners

- xTCA.4 under consideration by many labs for new project / upgrade (SLAC, CERN, ITER)