# Digital LLRF for Max-IV

Lars Malmgren, Antonio Milan, Robert Nilsson, Angela Salom

Maxlab, Lund University - National Electron Accelerator Laboratory for Synchrotron Radiation Research, Nuclear Physics and Accelerator Physics

**LLRF 2011** 17-20 October 2011, DESY, Hamburg

# Introduction

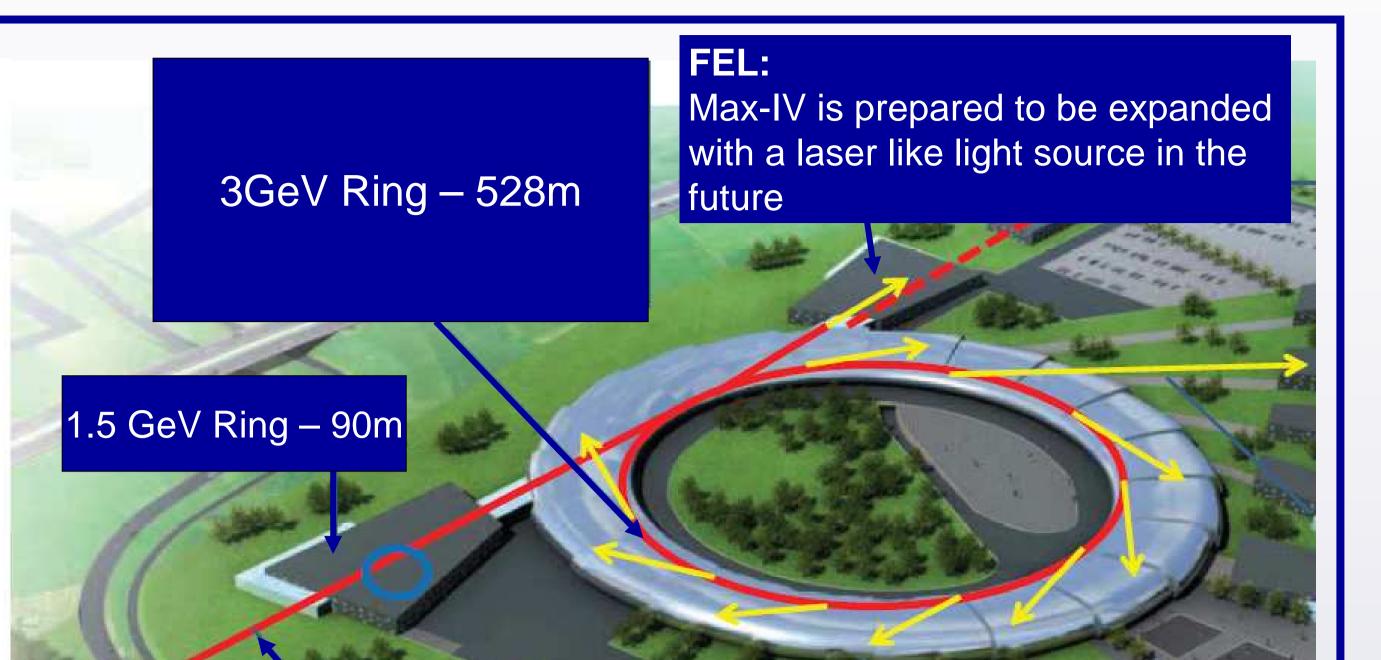

- ✓ Max-IV will be 3<sup>rd</sup> generation synchrotron light source in Lund, Sweden

- ✓ The accelerators of Max-IV will be:

- I Linac 250m injecting in two SR at full energy. Prepared to be expanded with a Free **Electron Laser**

- I.5GeV SR 96m 500mA; full energy injection and top up operation • 3GeV SR – 528m – 500mA; full energy injection and top up operation

- ✓ The characteristics of the RF Stations are:

- 6 RF stations in 3GeV SR; 4 RF Stations in 1.5GeV Ring.

- Components in one RF Station

- One Cavity: Capacitive load type and running at 100MHz

- Two Tetrodes of 60kW each

- One Hybrid combiner to provide 120kW

- One Circulator

- One 120kW Load

# Linear Accelerator – 250m

## LLRF Conceptual Design

#### **Main Characteristics**

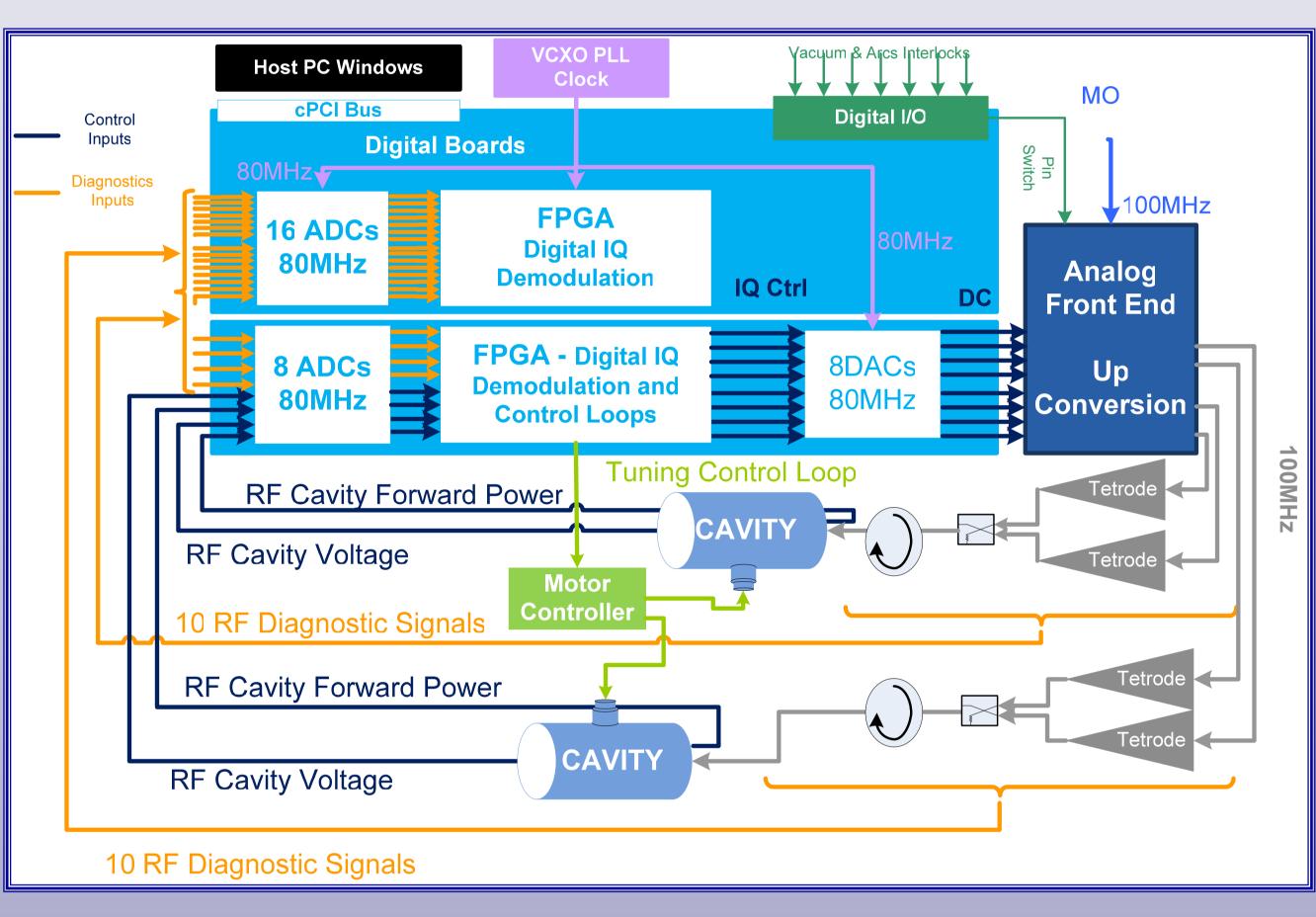

Design based on ALBA LLRF Systems

I LLRF system to control 2 cavities

#### **Extra Utilities**

Automatic conditioning

Fast Interlocks utilities (vacuum, arcs and reflected) power)

- Fast and slow diagnostics

- Automatic startup

- Landau Cavity Tuning

#### **Loops Requirements**

|                   | Resolution         | Bandwidth | Dynamic<br>Range |

|-------------------|--------------------|-----------|------------------|

| Amplitude<br>Loop | < 0.5% rms         | < 10kHz   | 30dB             |

| Phase<br>Loop     | < 0.5º rms         | < 10kHz   | 360°             |

| Tuning            | < ± 1 <sup>0</sup> | < 1kHz    | < ± 75°          |

#### <u>Hardware</u>

<u>cPCI Commercial Boards (VHS-ADAC from Lyrtech)</u>

Loops Board: 8 ADCs 14bits 105MHz; 8DACs 14Bits 480MHz; Virtex-4 FPGA; 128MB RAM; GPIO 32 bits

Diagnostics/Interlocks Board: 16 ADCs 14bits 105MHz; Virtex-4 FPGA; 128MB; GPIO 32 bits

#### **Timing System**

Commercial PLL Board (TI: CDC7005-EVM) with 80MHz VCXO locked with Master Oscillator (100MHz)

#### Analog Front Ends for Up-Conversion

Up-Conversion: DC signals IQ modulated with Master Oscillator signal (100 MHz) using an IQ quadrature modulator from mini-circuits.

BNC Tests Points accesible in front panel to monitor main RF signals using a scope

## First High Power tests with beam in Max-III

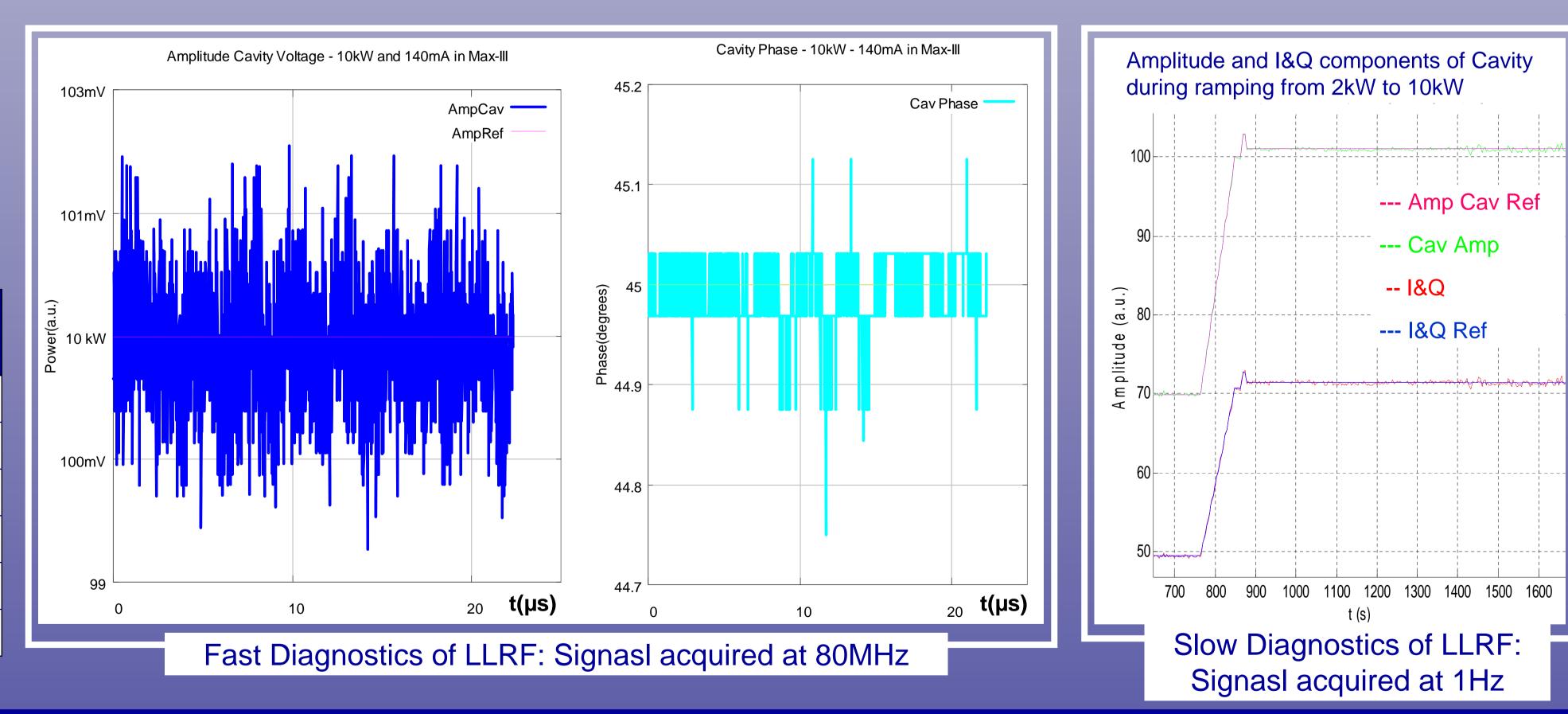

✓ First LLRF Prototype was tested at high power and with beam in Max-III.

✓ Amplitude, phase and tuning loops working under specifications

✓ Fast and slow diagnostics tested

✓ Local control system integrated in Tango and tested

|                    | Loop resolution<br>at 2kW | Loop resolution at 10kW |

|--------------------|---------------------------|-------------------------|

| I&Q Cavity Voltage | 0.12 % rms                | 0.14 % rms              |

|                    | 2mVpp                     | 2.5mVpp                 |

| Amplitude Voltage  | 0.48% rms                 | 0.5% rms                |

|                    | 2.5mVpp                   | 3mVpp                   |

| Phase              | 0.24º rms                 | 0.3° rms                |

|                    | 0.3ºpp                    | 0.5°pp                  |

Next Steps

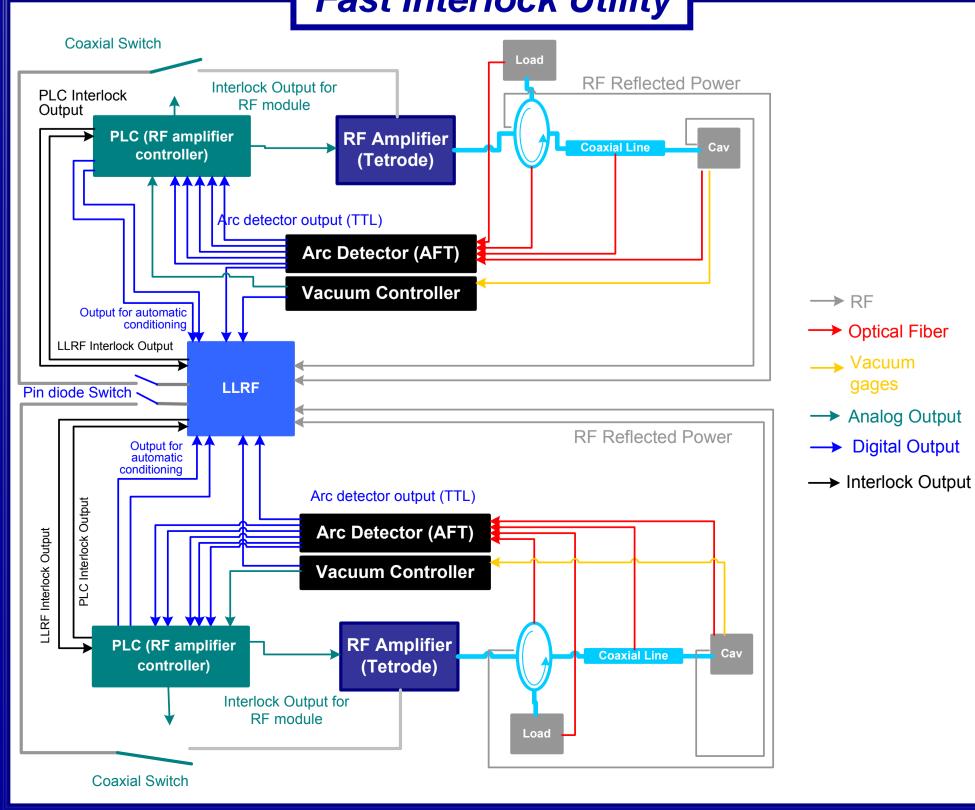

✓ Implementation of Fast Interlock Utility: RF Drive cut in less than 10µs when interlock condition happens

✓ Automatic Conditioning

✓ Landau cavity tuning

Extra diagnostics integration

✓ Automatic startup

✓ LLRF Series production (2013)

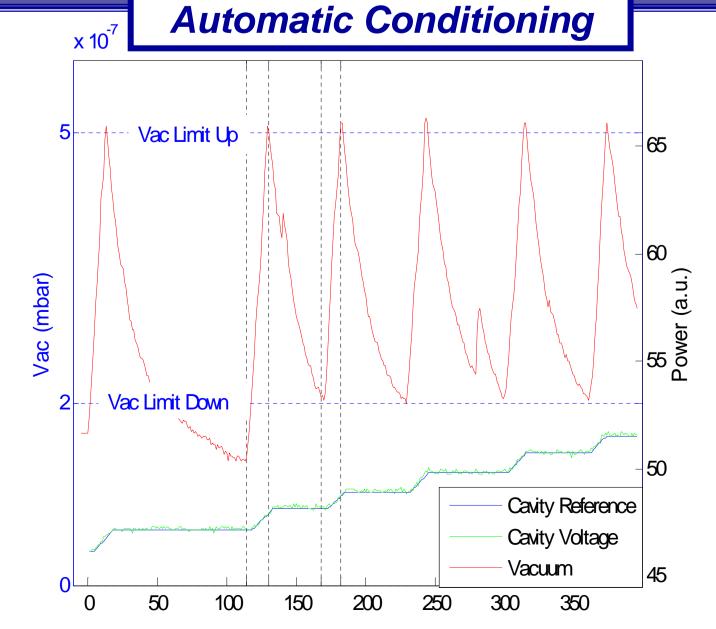

•RF Drive Square modulated: Amplitude and Duty Cycle adjusted by operator •Vacuum < Limit Down  $\rightarrow$  Amplitude/Duty Cycle Increases/Decreases ■Vacuum > Limit Up → Amplitude/Duty Cycle remains constant until vacuum is below limit down

(Data From ALBA Cavities Conditioning)