Marcel Trattner

#### Current Developments in Big Data Computation

#### Gen-Z & Compute Express Link

## **Agenda**

- Introduction in Memory-Based Computing

- Gen-Z

- Compute Express Link

- Combination of both standards

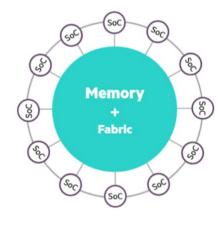

#### **Memory-Based Computing**

- Goal is to break through the memory wall

- Memory is in the center of the architecture instead of the processor

- Reduces overhead, when a SoC has to request more resources from another node

From processor-centric computing...

...to Memory-Driven Computing

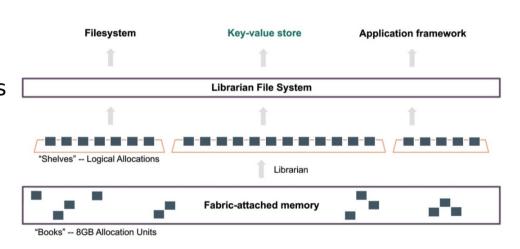

# Sandbox and the Librarian File System

- HPE Sandbox implements the concept of memorybased computing

- Fabric Attached Memory is the distributed pool of memory

- Librarian File System manages the memory

- Gen-Z is the protocol for communication between devices

## Sandbox and the Librarian File System

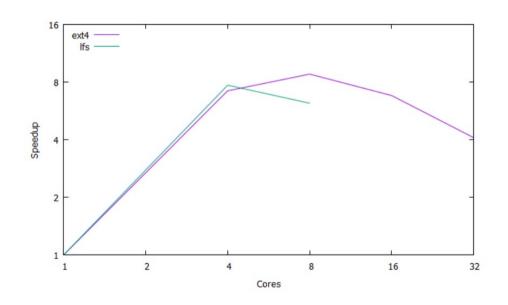

- Speedup for astronomical framework CASA

- Input data held on regular ext4 file system and the LFS

- Program shows slowdown on ext4 when executed with more cores

- Program crashes when data lies on the LFS and uses more than 8 cores

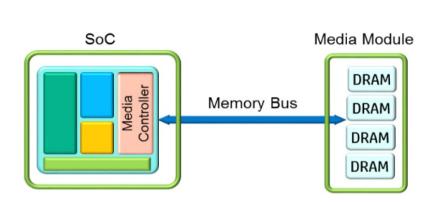

#### **Gen-Z Open Standard**

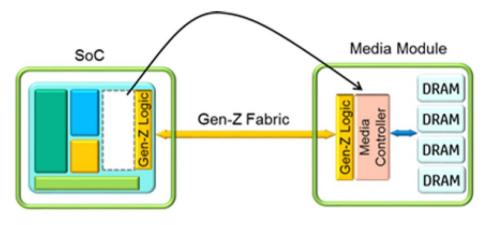

Traditional Design keeps the media controller with the CPU

Outsourcing of the media controller to the media module, i.e. DRAM

#### **Gen-Z Memory Fabric**

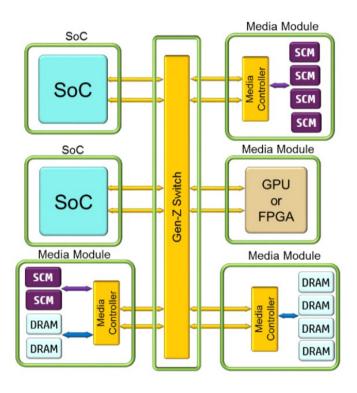

- Connection of the components through the Gen-Z Switch

- Increased modularity and therefore better scalability

- Creates a memory fabric in which the memory can be treated as a pool

- Peer-to-Peer connection, other than the tree-like topology of PCIe

- Fast connection through support of optical wiring

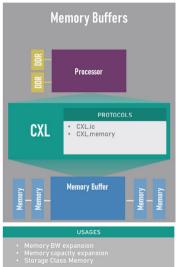

## **Compute Express Link**

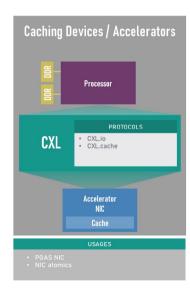

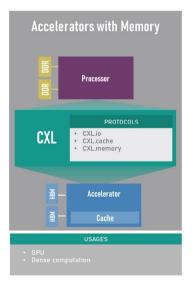

Three protocols for different use-cases:

CXI in - CXI mem - CXI cache

- Accelerators without memory

- Accelerators with memory

- Memory extension

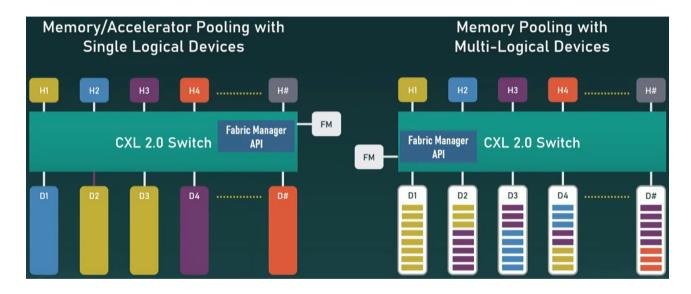

#### **CXL 2.0**

- Devices can be assign to hosts according to individual needs

- Partitioning of devices into Multi-Logical Devices

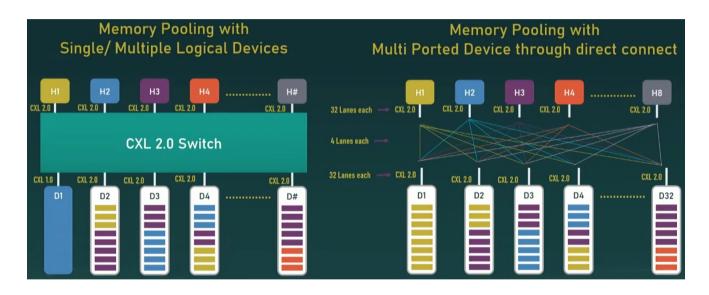

#### **CXL 2.0**

- Combination of Single and Multiple Logical Devices in one system

- Direct connection from hosts to devices possible

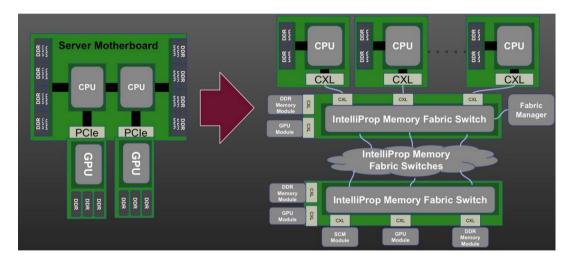

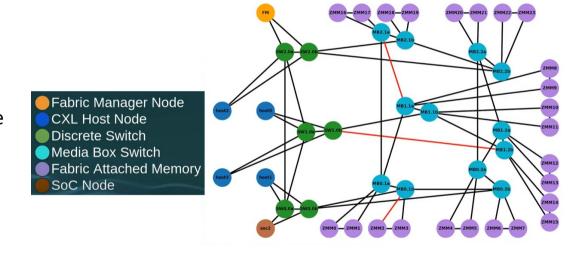

## **IntelliProp Demo SC21**

- Presentation of the company IntelliProp

- Combination of CXL with Gen-Z

- Disaggregation of the server architecture

- Connecting computing nodes to memory through Gen-Z fabric

- CXL is in the hosts and everything outside is Gen-Z

## **IntelliProp Demo SC21**

- Fabric Manager manages the topology of the system

- Connecting CPUs through multiple switches to memory

- Alternative routes available

- Components can be added or removed without problems

- The fabric manager registers disconnects or newly established connections

## Bildquellen

- https://www.gazettabyte.com/home/2021/12/24/data-centre-disaggregation-with-gen-z-and-cxl.html

- https://www.youtube.com/watch?v=sCQHxe72kuw

- https://www.youtube.com/watch?v=FaIK\_SFe\_i8

- https://www.hpe.com/us/en/newsroom/blog-post/2017/05/memory-driven-computingexplained.html

- https://genzconsortium.org/wp-content/uploads/2018/05/Gen-Z-Overview-V1.pdf

- https://www.computeexpresslink.org/\_files/ugd/0c1418\_14c5283e7f3e40f9b2955c7d0f60bebe.pdf

- Elsa Buchholz. "Untersuchung eines astronomischen Workflows im memory-based Computing". MA thesis. University of Applied Sciences, 2020.

University of Applied Sciences

www.htw-berlin.de