# MAX IV activities LEAPS-Innov WP7: Data reduction and compression

Zdenek Matej, May 2022

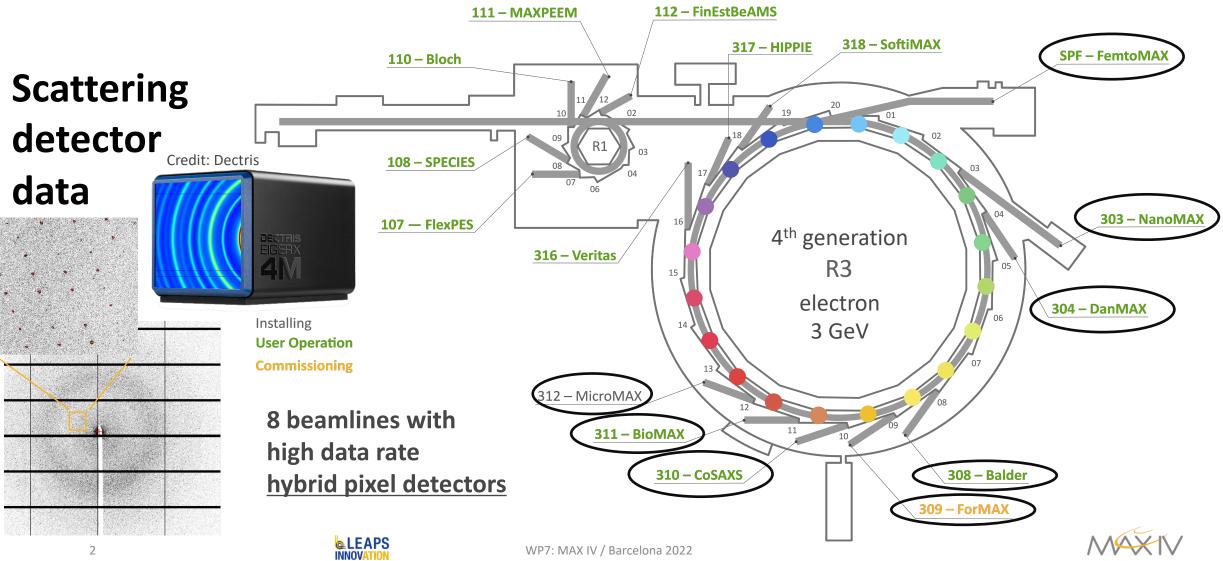

## **MAX IV synchrotron lab**

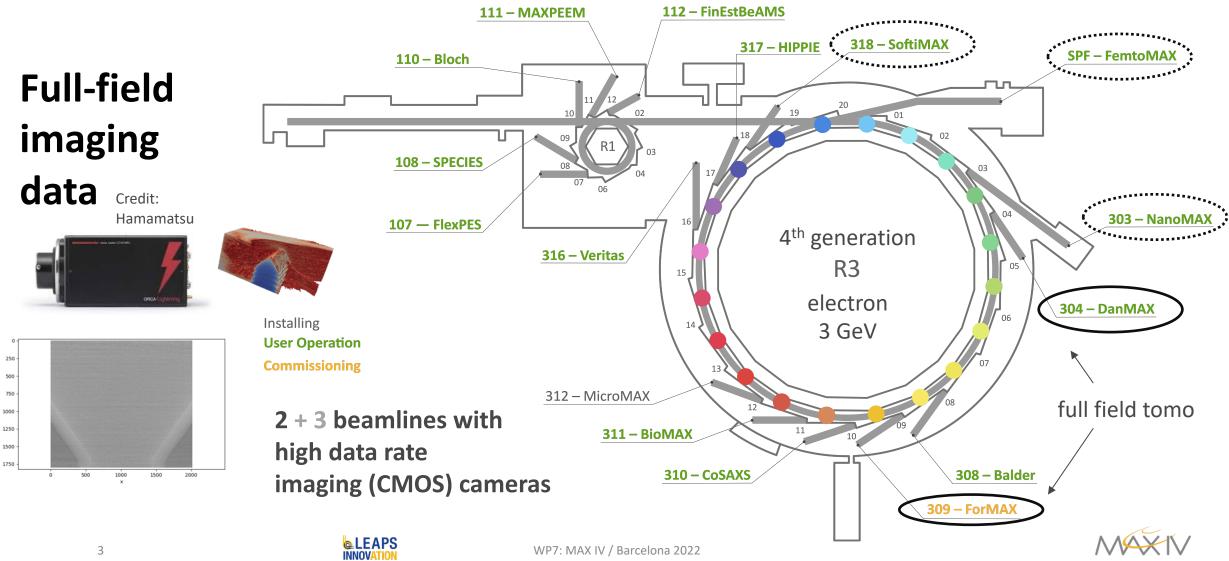

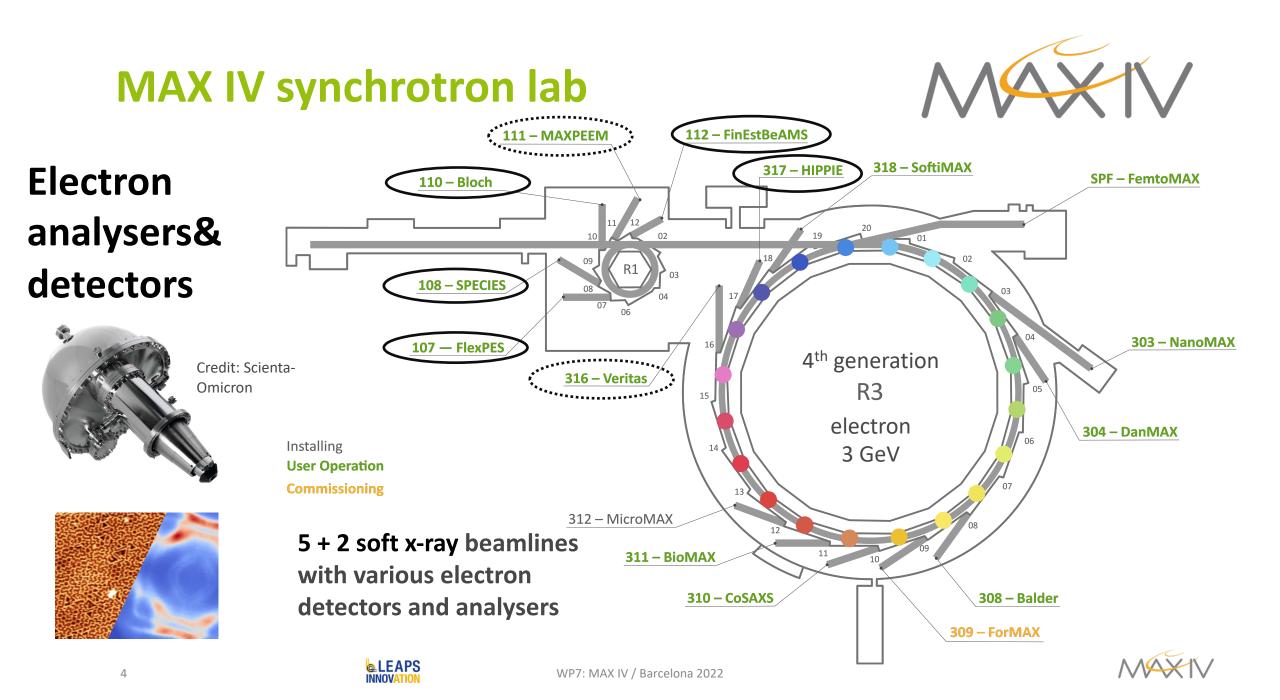

## **MAX IV synchrotron lab**

## **MAX IV participants**

Clemens – background in physics and XFEL; detectors. And pipelines for hard X-ray scattering beamlines

Michele –background in detectors at XFELs, expertise in CMOS cameras

Samuel – (former) student

lsak – junior member, machine learning & Al

physics and detectors. Deployment and control of detectors.

Soft X-ray contact – new hire, background

in physics and high perforce computing

Paul – background in particle

Zdenek – x-ray diffraction and scattering, imaging, scientific sw for FPGAs

2y position (?) – compression, DaTaSTAMP project

Darren – coordination and organization

WP7: MAX IV / Barcelona 2022

## **Activities**

#### in brief

- hybrid-pixel scattering detectors

- covered by bslz4

- from beginning HDF5

- DAQ systems evolving from filewriters, Lima<sup>1</sup>, ZMQ-receivers, k8s infrastructure

- on-the-fly data processing: simple TOT to energy conversions etc.

- special FPGA based DAQ for JungFRAU project from PSI

- prototyping data reduction on FPGAs AZINT

- cpu-AZINT for scattering beamlines (by Clemens)

- XPCS pipeline (Clemens)

- imaging (CMOS) cameras

- electron spectroscopy detectors

- decompression on hardware compute accelerators

## **Activities** in brief

### hybrid-pixel scattering detectors

- imaging (CMOS) cameras

- no compression solution in place (?) for non-full-field imaging techniques (~ detectors at 4) beamlines)

- 2 beamlines (0.75b full-field tomography)

- coming this summer/autumn

- data reduction: requirements for on the fly tomography reconstructions (talk by Christian (PSI))

- interest in general compression

- electron spectroscopy detectors

- decompression on hardware compute accelerators

# Activities

### • hybrid-pixel scattering detectors

- imaging (CMOS) cameras

- electron spectroscopy detectors

- HDF5-project for Scienta detectors

- new contact in Scientific sw

- decompression on hardware compute accelerators

# Activities

- hybrid-pixel scattering detectors

- imaging (CMOS) cameras

- electron spectroscopy detectors

- decompression on hardware compute accelerators

- on GPUs/lz4: Samuel was trying to follow the development at ESRF

- on FPGAs/lz4: investigation of possibilities

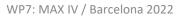

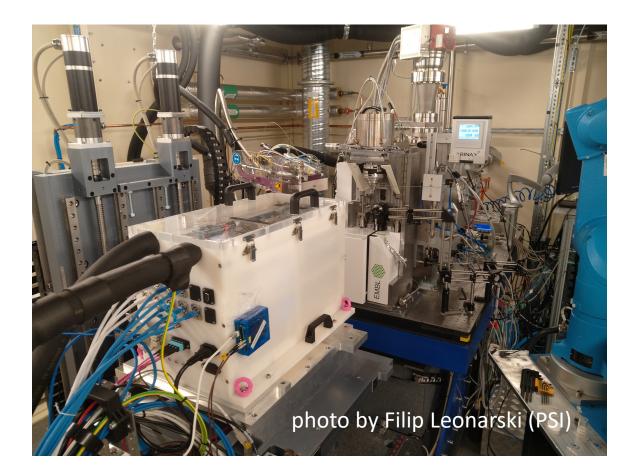

# Jungfraujoch (PSI) at MAX IV

#### **BioMAX beamline**

### 4 Mpix at 2kHz

- FPGA & GPU & CPU data

- processing

- bs on FPGA and lz4 at CPU

## **Data reduction on FPGAs**

#### **AZINT bincount – on Intel FPGAs with OpenCL**

|                                          | 385A                    | 520N-MX                | comment                                      |

|------------------------------------------|-------------------------|------------------------|----------------------------------------------|

| size                                     | medium                  | large                  |                                              |

| FPGA                                     | Aria 10 GX              | Stratix 10 MX          | Bittware / Nallatech                         |

| process                                  | 20 nm                   | 14 nm                  |                                              |

| memory                                   | 2xDDR3                  | 2xHBM2                 |                                              |

| QSPF                                     | 2x10/40 Gbs             | 4x100 Gbs              |                                              |

| framework                                | OpenCL                  | OpenCL                 | Credit: Bittware                             |

| processing pipelines                     | 32                      | 32                     | gitlab.com/MAXIV-SCISW/compute-fpgas/bincoun |

| ALUTs utilization                        | 45%                     | 40%                    |                                              |

| RAMs utilization                         | 60%                     | 25%                    | fp32 (fp64 possible), 8k bins                |

| frequency / ideal (MHz)                  | <b>205</b> / 240        | <b>360 /</b> 480       |                                              |

| host-to-device bandwidth                 | 4.7 GB/s                | 5.6 GB/s               | x8 PCIe Gen3, can handle 4.5M x 500 Hz 🗹     |

| processing (virtual) pixel rate          | 5.7 Gpix/s <sup>*</sup> | 8.9 Gpix/s             | allows pixel-splitting = 3 🔽                 |

| *comparable to NVIDIA V100 (~ 6<br>LEAPS | 5 Gpix/s, 12 nm process | S)<br>LEAPS Innov 2022 |                                              |

#### summary/interest

- hybrid-pixel scattering detectors

- quality of results of AZINT pipelines

- XPCS pipelines

- decompression on hardware compute accelerators

- Iz4 on GPUs and FPGAs

- imaging (CMOS) cameras

- data reduction: on the fly tomography reconstructions