# **Overview of MicroTCA usage at European XFEL**

Bruno Fernandes Fast Electronics Team Leader EEE Group

Hamburg, 7<sup>th</sup> December 2022 11<sup>th</sup> MicroTCA Workshop for Industry & Research

#### **XFEL Overview**

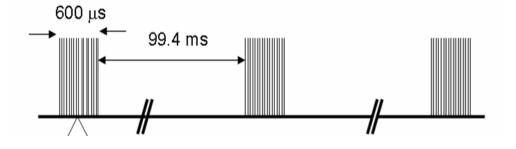

The European XFEL generates up to 2700 X-Ray pulses

- Inter pulse separation of 220 ns

- Train repetition of 10 Hz

- 3 beamlines, 6 instruments

- ► 2 more beamlines are planned

First user operation started in September 2017

# **MicroTCA in XFEL**

- MicroTCA platform is the key component for

- Timing distribution (both in and outside the crate)

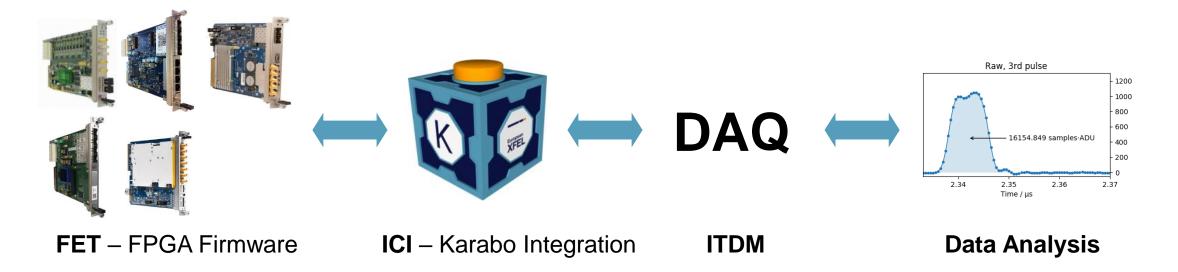

- Digitizer raw and process data

- Detector triggering and synchronization

- At photon beam lines, experiments and related laboratories at XFEL are ~60 MicroTCA crates (more already planned)

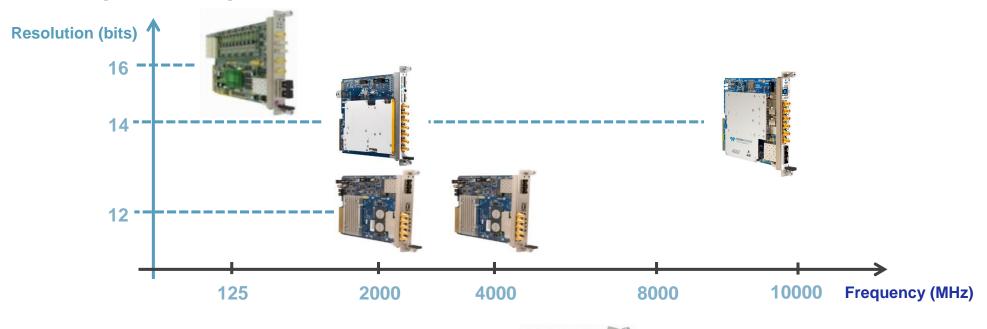

- 300 fast data channels (SIS8300, 16 bit @ 125MHz)

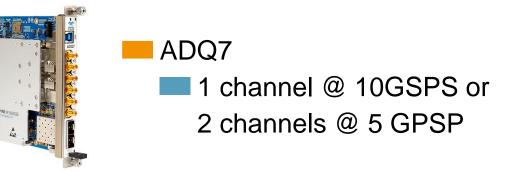

- 108 high speed data channels

- ► ADQ412, 12 bit @ 2 GHz

- ► ADQ14, 14 bit @ 1 GHz

- XFEL will continue to grow (SASE4 and 5, new instruments)

- On Call Duty has significant low activity when compared to other groups

- This year the team received 19 calls, of which only 1 was a 'real' hardware issue

- Some systems have been working reliably for **5 years now**

- Stability of MicroTCA and XFEL's FPGA solutions

4

# MicroTCA @ XFEL in 2022

- MicroTCA setups mostly remain static

- Restructuring of the team and Institute priorities

- Review of data acquisition and processing workflow

- Evaluation of other FPGA platforms

# **CPU installation/maintenance with Foreman and Puppet**

- OS installation + Puppet via network

- New CPU shows up on Network

- Foreman install OS and configures target Puppet Manifest

- Puppet guarantees that CPUs have the same environment

- Monitor Host resources

- This solution as proven very successful for maintenance, testing and migration of our MicroTCA CPUs

- Roll out of updates/bug fixes

- Management of hosts groups

- MicroTCA hosts have increasingly more specific configurations

- Next step is FPGA/MCH management

#### **XFEL's integrated digitizers**

Update of XFEL Simulink library

## **FPGA** processing algorithms

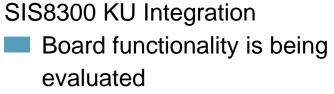

#### Peak Integration

- User definition of integration value

- Based on user threshold value

- Baseline per trace or pulse

- Virtual ADC channels (add/subtraction of raw data)

- Based on Bunch Pattern decoding

Automatic Peak Integration

Conditional and Dynamic Trigger

VETO decision for 2D Detectors

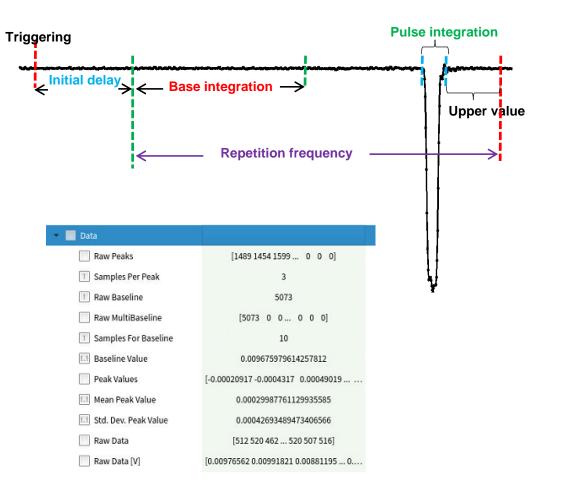

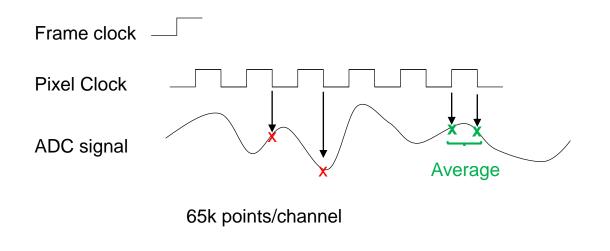

#### SIS8300 firmware for pnccd Detector

- Dedicates firmware for pnccd Detector setup

- 2x SIS8300 board with data from 10 channels

- Reduced amount of data

- Allows for Raw Data, sampling of only falling/rising edge or average

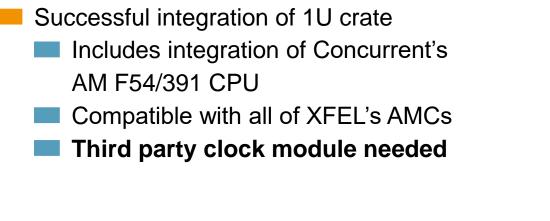

## nVent's 1U Crate

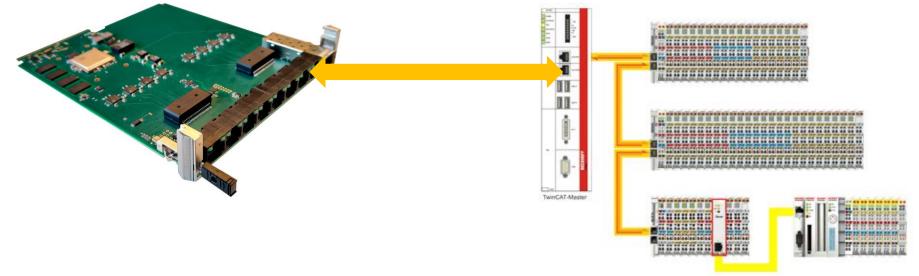

#### **NAT Ethercat AMC**

**EtherCat AMC** solution from N.A.T. for communication with the PLC hardware

- Uses Zynq UltraScale+

- Direct communication of Information (TrainID, Beam Modes...)

- Use of FPGA processing to communicate PLC actions

Bunch Pattern decoder information

Syncronization of PLC equipment with Timing System

#### **Questions?**

Fast Electronic Team

```

F. Babies

```

I. Soekmen

H. Habibullah