https://www.desy.de/

#### Thin, Precise, Fast

#### Ways Towards the Ultimate Silicon Sensor

#### Faster, Harder, Scooter Scooter, 2009 Ways Towards the Ultimate Silicon <del>Sensor</del> Detector

#### The Ultimate Silicon Sensor: A Detector-On-Chip System

S. Spannagel - Terascale Detector Workshop - Thin, Precise, Fast

#### The Ultimate Silicon Sensor: A Detector-On-Chip System

#### The Question Is What Is The Question Scooter, 2009 Requirements Differ...

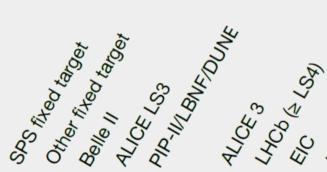

### The Landscape of Future Colliders & Upgrades

- European Strategy Update evaluated possible directions for particle physics

- ECFA published Detector R&D Roadmap to structure development of detectors & technology

- Higgs boson plays unique role in extending knowledge

2030-2035

- Address questions within SM, provide sensitivity to new physics

- Precision measurements required

< 2030

2040-2045

> 2045

ECFA Detector R&D Roadmap

**European Strated**

2035-2040

S. Spannagel - Terascale Detector Workshop - Thin, Precise, Fast

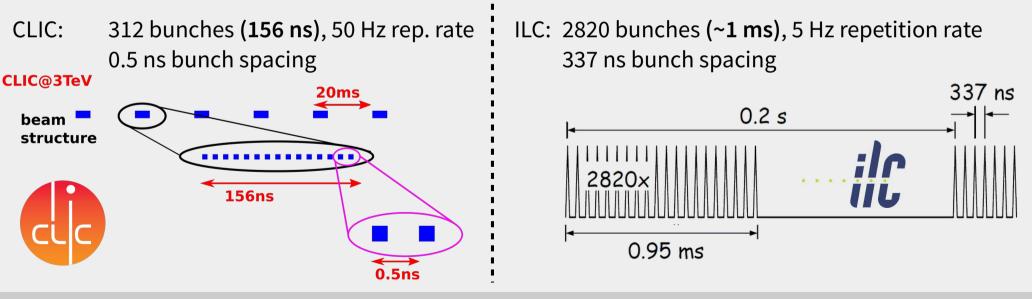

### Challenges at Linear Colliders

- High precision, low material, radiation hardness less of an issue

- Adjustable cms energies emphasis on different components

- LC operate in bunch trains with low duty cycle: trigger-less, frame-based readout architecture possible

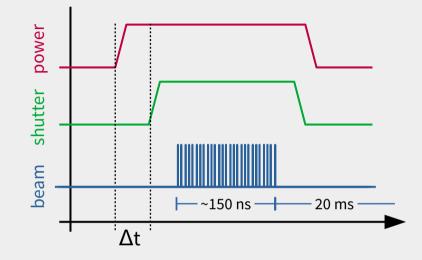

### Linear Colliders: Power Pulsing

• LC have very low duty cycle, for CLIC < 0.01 ‰

- Save power by switching to lower-power idle state between bunch trains

- Analog power pulsing: Multiplex DACs of amplifiers, discriminators between ON and OFF state

- **Digital power pulsing**: e.g. by gating clock to pixel matrix

• Allows to significantly reduce overall heat dissipation, reduce requirements on cooling capacity, material, ...

## **Challenges at Circular Lepton Colliders**

Precision requirements similar to linear colliders, however...

- Continuous beams (no bunch trains); bunch spacing down to 20 ns

- Power management and cooling (no power pulsing)

- Physics events at up to 100 kHz

- Fast detector response ( $\leq 1 \mu$ s) to minimize dead-time and pile-up

- Strong requirements on front-end electronics and DAQ systems

• At the same time: low material budget! Minimize electronics, cables, cooling, ...

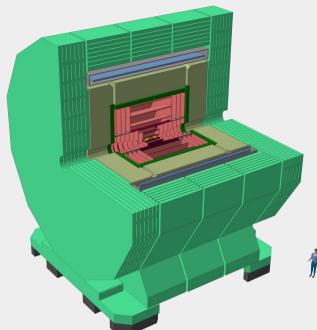

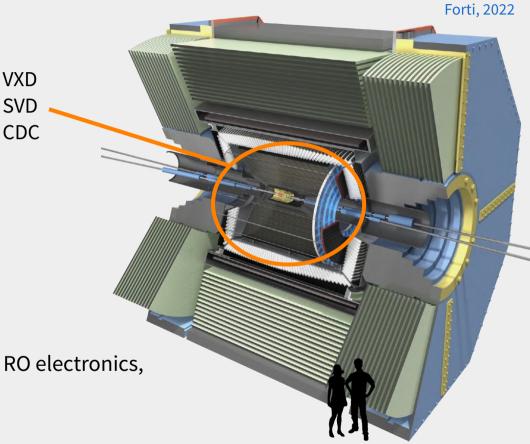

### Belle II Upgrades

- Currently luminosity limited by

- beam-beam effects,

- Beam lifetime,

- injection backgrounds

- Upgrade detectors for

- better resilience against backgrounds,

- improved performance

- Many Upgrade ideas currently discussed:

- "adiabatic improvements", replacement of RO electronics, entirely new sub-detectors, ...

- Upgrade proposals with MAPS, e.g. OBELIX

#### Silicon Detector Requirements at Lepton Colliders

- Precision measurements especially demanding on vertex & tracking detectors

- Momentum resolution

- Impact parameter resolution –

- Time resolution

- large lever arm, minimum scattering

- high resolution, min. scattering, small radii

- fast sensor response, large S/N

|                         | Lepton Colliders                | (HL-) LHC (ATLAS/CMS)  |                                                        |  |  |

|-------------------------|---------------------------------|------------------------|--------------------------------------------------------|--|--|

| Material budget         | < 1% X <sub>0</sub>             | 10% X <sub>0</sub>     |                                                        |  |  |

| Single-point resolution | ≤ 3 µm                          |                        | ~ 15µm                                                 |  |  |

| Time resolution         | ~ ps – ns                       |                        | 25ns                                                   |  |  |

| Granularity             | ≤ 25 µm x 25 µm                 |                        | 50µm x 50µm                                            |  |  |

| Radiation tolerance     | $< 10^{11} n_{eq}^{2} / cm^{2}$ |                        | O(10 <sup>16</sup> n <sub>eq</sub> / cm <sup>2</sup> ) |  |  |

| Duty cycle              | < 0.01 ‰ @ ~ms (linear)         | 100 % @ ~ns (circular) | 100 % @ 25ns                                           |  |  |

#### **Opportunities in Small-Scale Experiments**

- Many non-accelerator (or small accelerator) based experiments planned •

- Several will require silicon detectors (e.g. LUXE) •

- Requirements differ significantly, no funding for dedicated R&D •

< 2025 > 2035 2025-2030 2030-2035 ECFA Detector R&D Roadmap

#### The Ultimate Silicon Sensor: A Detector-On-Chip System

#### And No Matches Scooter, 2013 New Technologies for the "Ultimate" Sensor

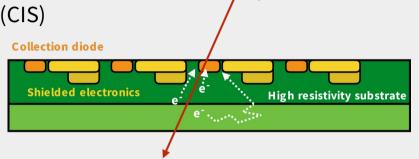

#### Monolithic Active Pixel Sensors

- Electronics & sensor in the same wafer

- Produced in commercial CMOS imaging processes (CIS)

- Fully integrated: amplification, discrimination & readout

- Shield electronics via additional implants

- Large-scale manufacturing simplified compared to hybrids

- No bump bonding required

- No limitation on minimum pitch size

- Design can be very intricate

- Sensor: electric field complex

- ASIC design, process limitations, ...

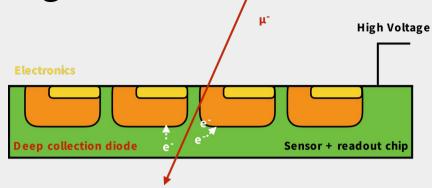

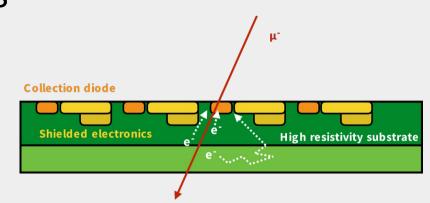

μ-

- Different approaches

- Deep collection diode surrounding electronics

- Separate shielding & collection diode

#### Large & Small Electrode Designs

- Shield electronics via deep collection diode around electronics

- Allows high bias voltage to be applied

- Fast & large signal, large depletion volume

- Challenge: large collection diode leads to

- large input capacitance

- increased power consumption

- Electronics outside charge-collection well

- Requires high-resistivity material (e.g. epitaxial layer) to allow depletion

- Small collection diode leads to small capacitance

- Challenge: effect of p-well potential on electric field / charge collection

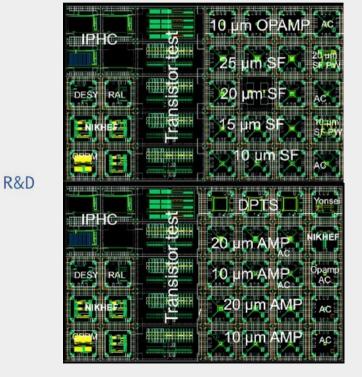

#### Many Technologies, Many Chips

- Started with 350nm process, now at 180nm 130nm technologies

- Many successful chips designed & produced over last few years

- First large-area detectors built in HEP

- Many spin-offs for applications outside HEP (medical, space)

- So far: no single prototype satisfies *all* requirements!

List by no means exhaustive, chips not to scale...

Kremastiotis et al., 2020

Pernegger et al., 2021

IPHC, 2021

Bespin, 2023

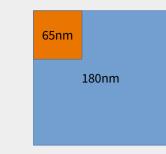

#### 65nm CMOS Imaging Technology Node

- MAPS design in 65 nm CMOS imaging process first application in HEP

- Higher logic density → reduced pixel pitch

- Lower analog/digital power consumption

- Large 300 mm wafers

Timing resolution

- International collaboration for common submissions to foundry, organized through CERN EP R&D programme

- Goal: explore new technology in terms of

- Scalability

- wafer-scale sensors through stitching

- through sensor layout optimization

- Position resolution through increased granularity

MLR1 reticle

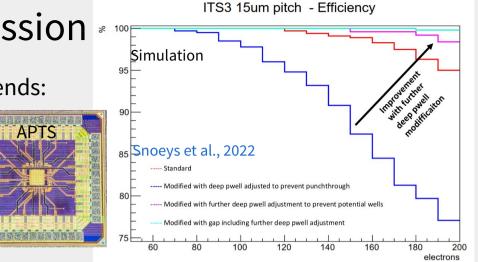

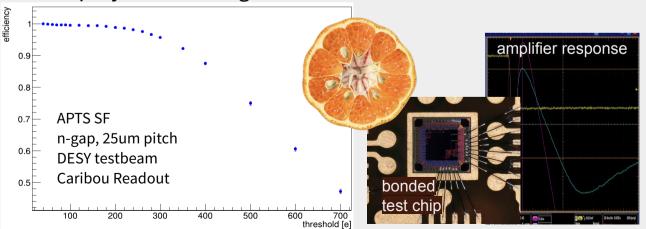

## (Some) Results from First Submission

- Many test chips for pixel characterization & front-ends: APTS, DPTS, CE65, DMLR1

- Enormous effort from many groups to characterize different pitches, front-ends

- Validation of process modifications in 65nm

- "Tangerine" Helmholtz Innovation Pool project for next-generation silicon detectors

- Focus: fast pixel front-end (ns timing, with ToT and ToA)

- Sensor charact. with APTS chip

- Sensor simulations with TCAD & Allpix<sup>2</sup> MC

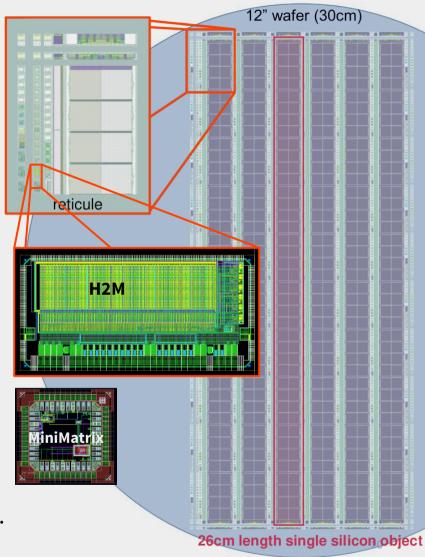

#### Second Submission Taped Out

- ALICE ITS3: wafer-scale stitched sensor MOSS

- Learn stitching, yield, defects masking

- Study power schemes, leakage, spread, noise, speed

- H2M Hybrid to Monolithic (DESY, CERN, IFAE)

- Full-matrix chip following digital-on-top design

- Port full hybrid feature set to monolithic chip

- Timepix-like architecture, different modes (ToT, ToA, ...)

- Expected back from foundry end of April 2023

- This isn't the end have not yet found the holy grail: Analog circuitry doesn't scale, very thin active region, ...

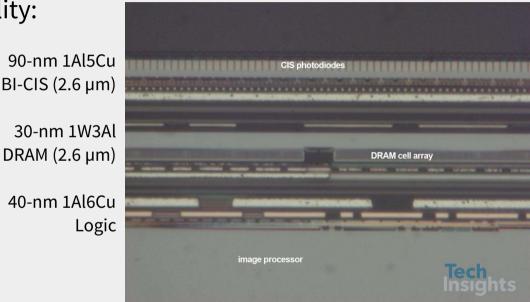

- 3D Integration / Wafer-Wafer Bonding

- Hybrid approach to separate functionality:

- CIS process: sensor & amplifier

- CMOS process: digital logic, readout

- Bonding & thinning at wafer level can be expensive for prototyping

- Popular in industry, e.g.

- Sony IMX400 for Cell Phones

20 Million 1.22-µm Pixel @ max. 1 kfps

• More flexibility on digital circuitry, but might come with higher power dissipation

# How Much Is The Fish Submission?

- "CMOS sensors are cheap and production is scalable" yes and no

- Initial cost of small technology nodes very expensive (mask production, ...)

- Multi-project wafer runs (MPWs) not always available, prototypes require engineering runs

- Scaling for final production indeed scales better than e.g. bump bonding

- Same issues of course also apply to CMOS readout ASICs

- General issue: single-vendor problem

- Processes & designs specific to individual vendors

- Also true for specialty foundries (LGADs, current sensors)

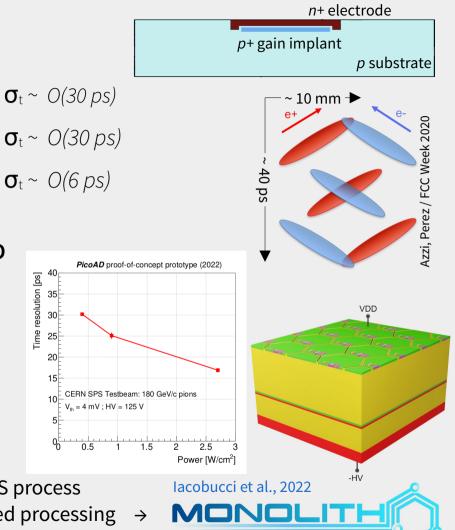

### **Picosecond Timing**

- Timing information for pile-up mitigation

- PID for heavy flavor physics, CP violation, B physics •

- Chromatization:  $\sqrt{s}$  depends on longitudinal bunch pos.  $\mathbf{\sigma}_{\rm t} \sim O(6 \, ps)$

- Dedicated timing detectors with LGAD sensors / UFSD •

- Low gain  $(x10-30) \rightarrow$  fast-rising pulse enables timing

- Dedicated timing layers: additional material

- Integration into MAPS detectors: 4D measurements

$\leftarrow$

180nm commercial CMOS process 130nm BiCMOS, dedicated processing

[sd]

resolution

ime

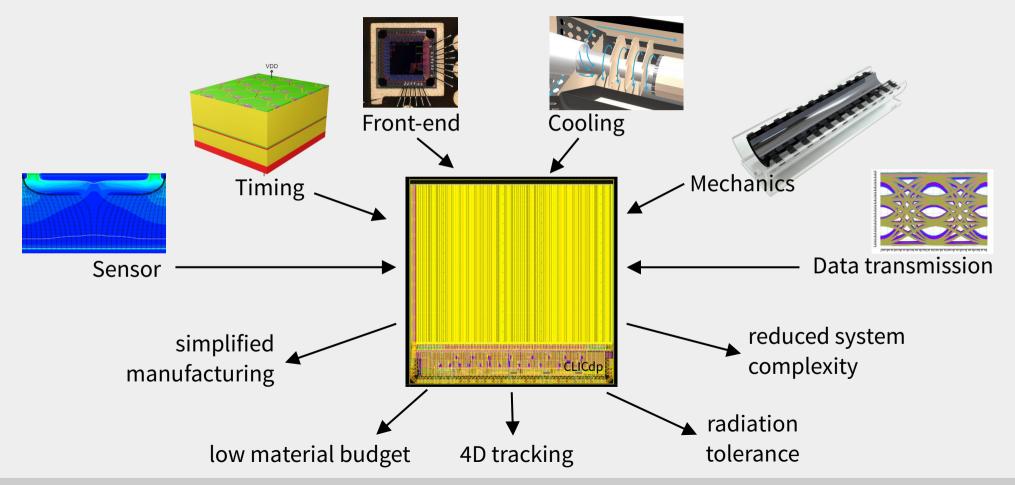

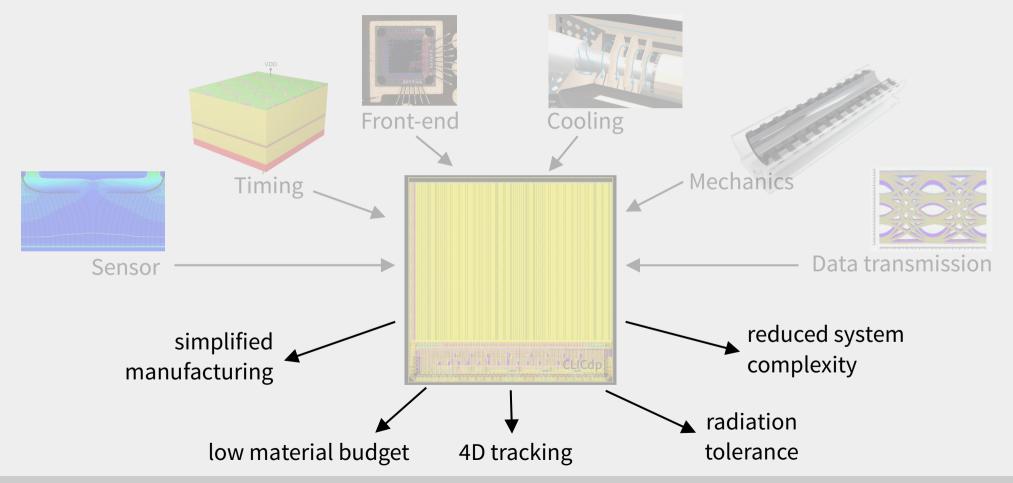

#### The Ultimate Silicon Sensor: A Detector-On-Chip System

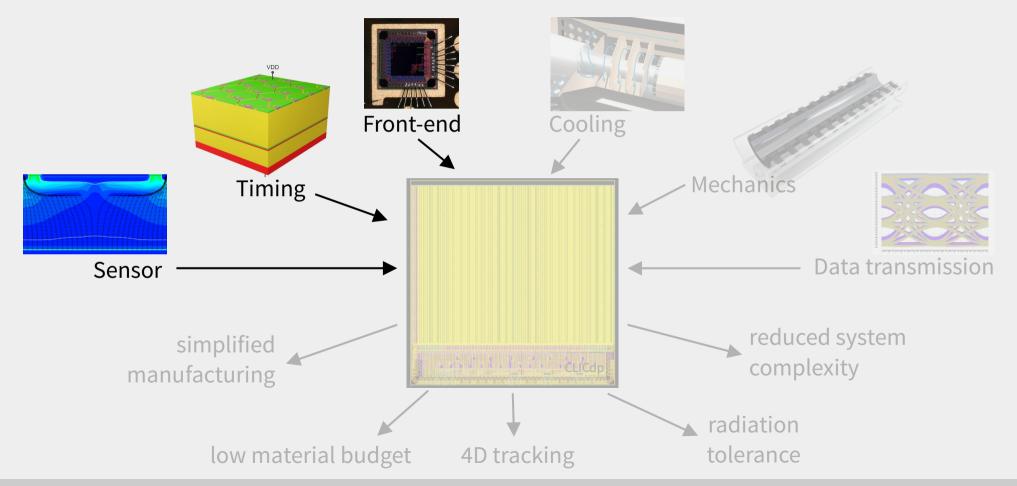

#### **Liquid Is Liquid** Scooter, 2019 Considerations for Cooling, Mechanics & Data Transmission

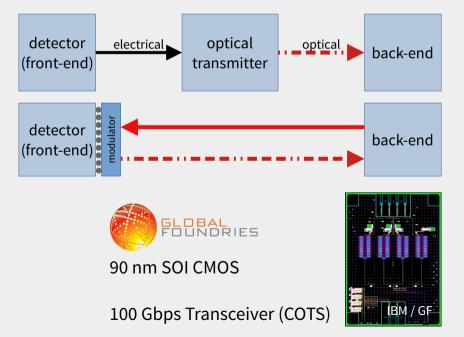

# I Want You To Stream – Data Transmission

• Bandwidth & power consumption of data transmission critical for future experiments:

~ Gb/s

$\frac{1 \, cm^2 \text{chip area}}{(15 \, \mu \, m)^2 \text{pixel pitch}} \ge 450 \, kPix \rightarrow 450 \, kPix \cdot 20 \, \text{bit} \cdot 10^{-5} \text{occupancy} \simeq 90 \, b \rightarrow \frac{90 \, \text{bit}}{20 \, ns} \ge 4.5 \, Gb \, s^{-1} cm^{-2}$

- Currently: Electrical transmission off-chip, conversion by optical transmitters

- Limited bandwidth

- Driving signals is power consuming ~ *pJ/bit*

- Additional material, electromagnetic interference, ...

- Silicon Photonics: external laser, modulation on ASIC

- Increased bandwidth >> 10 Gb/s

- Energy efficient, only modulation << pJ/bit

- 3D integration with MAPS

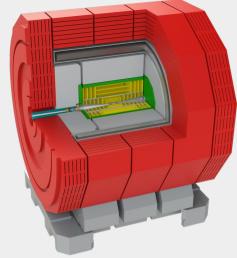

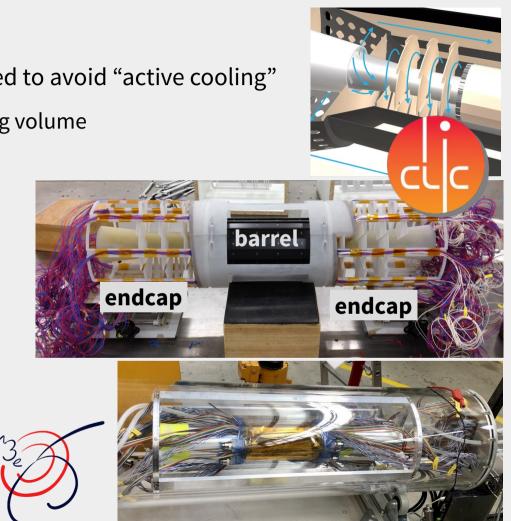

#### Forced Gas Flow Cooling

- To drastically reduce material budget, we need to avoid "active cooling"

- Cooling with forced gas flow through tracking volume

- Remove material for piping, coolant, thermal connectors, ...

- Demands reduction of heat dissipation

- Example: CLIC Vertex Detector

- Cooled with forced air flow

- Spiral vertex disks direct air

- Example: mu3e Detector

- Cooled with helium flow

S. Spannagel - Terascale Detector Workshop - Thin, Precise, Fast

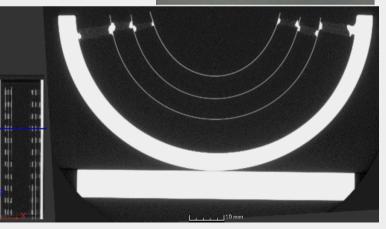

# Mind The Gap – Fully-Active Detectors

- "Remove everything that doesn't look like a sensor"

- Below 50 µm thickness silicon becomes flexible

- Bending wafers into cylinders adds stability

- Building half-shells from full-wafer sensors

- ALICE started R&D effort for ITS3 upgrade

- Monolithic CMOS pixel detectors

- Wafers thinned & bent

- Held in place by low-density carbon foam spacers

Šuljić, 2020

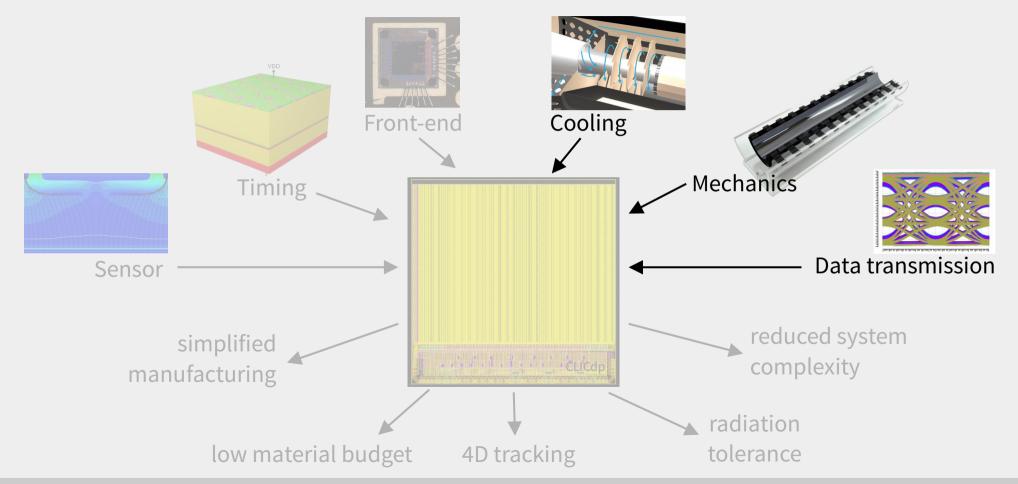

# The Only One – The Ultimate Silicon Detector

- The ultimate silicon sensor will be a **detector-on-chip system**.

- Requirements for future lepton collider experiments similar:

- Very low material budget

- High position & time resolution

- Monolithic Active Pixel Sensors matured in past years

- Many new prototypes & full detectors

- Move to smaller technology nodes on the way

- Considerations for future developments: cost, 3D integration, timing

- Sensor is always part of a system

- Data transmission power reduction, bandwidth increase with silicon photonics

- Cooling with forced gas flow to minimize material power dissipation critical

- Far future: Radiation hardness industry is developing processes for wide-bandgap semiconductors

32

|                      |                                                                             |                                                                                                                                    | < 2030 | 2030-<br>2035 | 2035-<br>2040 | 2040-<br>2045 | > 2045 |

|----------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|---------------|---------------|--------|

| Solid<br>state DRDT  | DRDT 3.1                                                                    | Achieve full integration of sensing and microelectronics in monolithic CMOS pixel sensors                                          |        |               |               | •             |        |

|                      | DRDT 3.2                                                                    | Develop solid state sensors with 4D-capabilities for tracking and calorimetry                                                      |        | •             |               | •             |        |

|                      | DRDT 3.3                                                                    | Extend capabilities of solid state sensors to operate at extreme fluences                                                          |        |               |               | •             |        |

|                      | DRDT 3.4                                                                    | Develop full 3D-interconnection technologies for solid state devices in particle physics                                           |        | •             | •             | •             |        |

| Electronics DRDT 7.3 | Advance technologies to deal with greatly increased data density            |                                                                                                                                    |        |               |               |               |        |

|                      | <b>DRDT 7.2</b>                                                             | Develop technologies for increased intelligence on the detector                                                                    |        |               |               |               |        |

|                      | <b>DRDT 7.3</b>                                                             | Develop technologies in support of 4D- and 5D-techniques                                                                           |        |               |               |               |        |

|                      | DRDT 7.4                                                                    | Develop novel technologies to cope with extreme environments and required longevity                                                |        |               |               |               |        |

|                      | Evaluate and adapt to emerging electronics and data processing technologies |                                                                                                                                    | •      |               | •             |               |        |

| DRDT 8               | DRDT 8.1                                                                    | Develop novel magnet systems                                                                                                       |        |               |               |               |        |

|                      | <b>DRDT 8.2</b>                                                             | Develop improved technologies and systems for cooling                                                                              |        | -             |               |               |        |

| megration            | DRDT 8.3                                                                    | Adapt novel materials to achieve ultralight, stable and high precision mechanical structures. Develop Machine Detector Interfaces. |        |               | •             |               |        |

|                      | DRDT 8.4                                                                    | Adapt and advance state-of-the-art systems in monitoring including environmental, radiation and beam aspects                       |        |               | •             |               |        |