## Dynamische Re - Konfiguration eines FPGAs mittels internem Kontroller

SEI - Tagung an der GSI Frühjahr 2011

Quelle: Bild: ESA – Erprobungssatelliten im Weltall

#### Überblick

- Einleitung

- Motivation und Stand der Technik

- Realisierung

- Dynamische Re Konfiguration des FPGAs

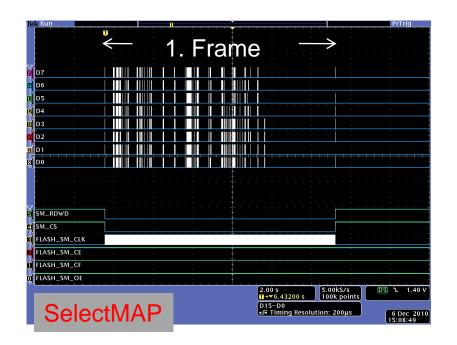

- SelectMAP

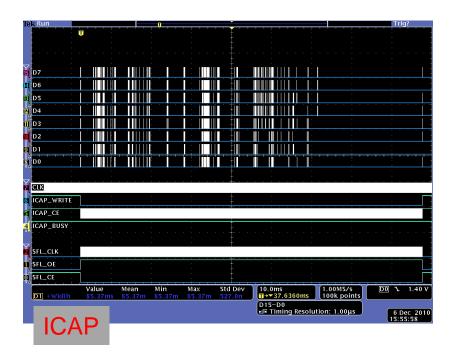

- ICAP

• Ergebnisse und Ausblick

#### **DSPS** (Digitale Signalverarbeitungssysteme)

JÜLICH FORSCHUNGSZENTRUM

Wir entwickeln und erstellen umfassende elektronische Systeme und Lösungen für wissenschaftliche Instrumente, wobei Signal- und Bildgebende Systeme auf fliegenden Trägern im Vordergrund stehen.

#### **Projekte:**

GLORIA: Ziel ist es erstmals ein detailliertes

globales Bild des Tropopausen-

bereichs zu liefern.

Kompsat-3A: Entwicklung einer Infrarot Detektor

Ausleseelektronik zum Einsatz auf

einem Satelliten.

Was muss beachtet werden um Elektronik im Weltraum einzusetzen?

#### Randbedingungen und Störeinflüsse im Weltraum

- Vibrationen und Beschleunigungen bei der Startphase der Trägerrakete

- Temperaturschwankungen (120 C bis -80 C) aufgrund von Sonnen- und Schattenzyklen im Orbit

- Vakuum (Problem: z.B. Aufplatzen von Kondensatoren, Abführen von thermischer Energie)

- 100%ige Funktion → eingeschränkter Zugriff von der Bodenstation

- Höhere Strahlungsmengen im Vergleich zu Erde (hoch energetische Teilchenstrahlung)

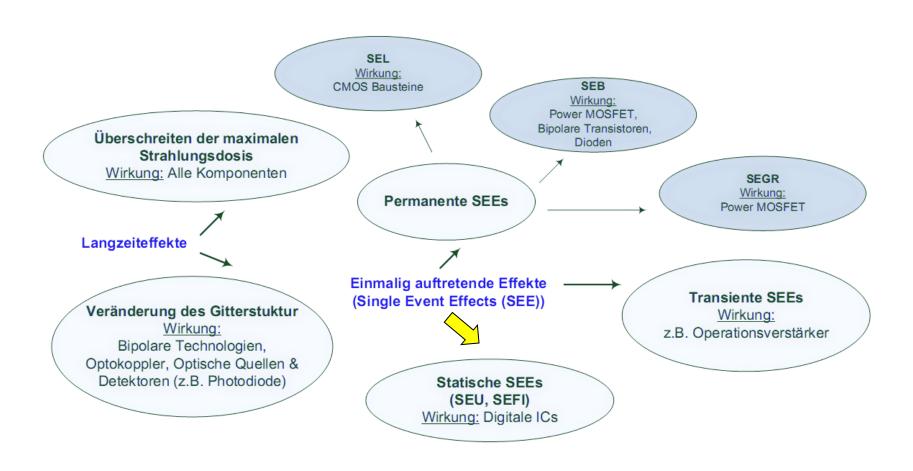

Wie wirkt die Teilchenstrahlung auf die Elektronik?

#### **Einleitung: Effekte durch Teilchenstrahlung**

#### Wie oft tritt ein SEU auf?

Quelle: Joshua D. Engel, Michael J. Wirthlin, Keith S. Morgan, Paul S. Graham, ed., Predicting On-Orbit Static Single event Upset rates in Xilinx Virtex FPGAs, Los Alamos National Laboratory, 2006. LA-UR-06-8178.

#### Einleitung: Auftrittswahrscheinlichkeit von SEUs

#### Beispiel eines Virtex-II (2V6000) FPGAs

| Orbit  | Altitude<br>(km) | Inclination (degrees) | Upset Rate (SEU/device/day) | MTBF<br>(Time/Event) |

|--------|------------------|-----------------------|-----------------------------|----------------------|

| LEO    | 400              | 51.6°                 | 0.67                        | 1.5 days             |

| LEO    | 800              | 22.0°                 | 9                           | 2.7 hrs              |

| Polar  | 833              | 98.7°                 | 6                           | 4 hrs                |

| Const. | 1,200            | 65.0°                 | 25                          | 58 min               |

| GEO    | 36,000           | 0.0°                  | 0.47                        | 2.1 days             |

Quelle: XILINX- Defense & Aerospace Presentation - www.xilinx.com/publications/prod\_mktg/MilAero.pdf

#### **Einleitung: Stand der Technik**

- Einsatz von Strahlungsfesten Bauteilen

- Teuer

- Evtl. Qualifikation von Bauteilen erforderlich

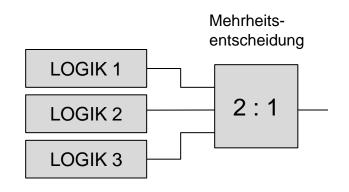

- TMR Triple Module Redundancy

- Dreifache Implementierung der FPGA Logik

- Mehrheitsentscheider an den Ausgängen

- Fängt nur ein SEU auf

#### Aktuelle Lösungsansätze:

- Sicherung der FPGA Konfiguration

- → Periodisches Auffrischen der Konfiguration

## Realisierung

#### Realisierung: Dynamische Re - Konfiguration

#### Was gibt es für Re – Konfigurationstechniken?

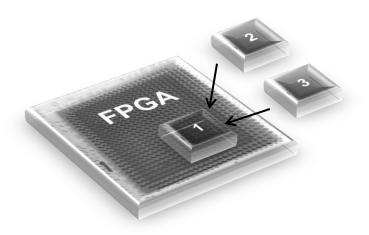

Partielle dynamische Re - Konfiguration

**Komplette dynamische** Re - Konfiguration

=> Komplette dynamische Re - Konfiguration

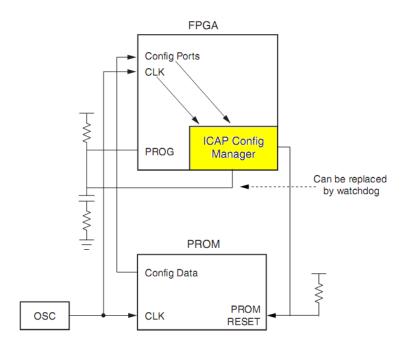

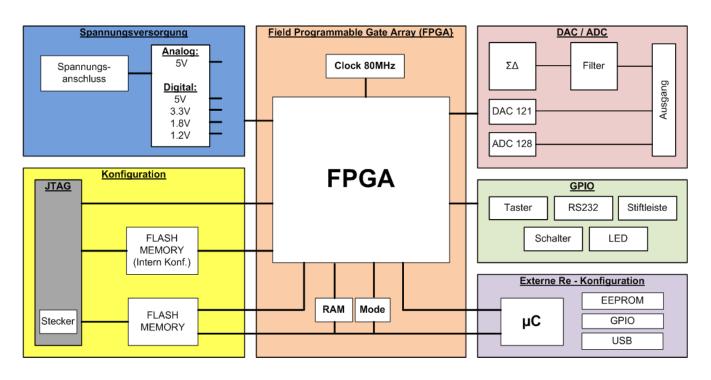

## Realisierung: Externe / Interner Konfigurationskontroller

#### Mögliche Schnittstelle

SelectMAP Schnittstelle

**ICAP Schnittstelle**

#### Externe Konfiguration (ext. µC)

#### Xilinx XQR18V04 Xilinx QPro Radiation-Tolerant **XQR17V16** Virtex-II FPGA Radiation-Hardened DATA[0:7] DATA[0:7] Configuration **CCLK CCLK** Controller CF PROG B CE RDWR B OE/RESET\_B CS B DONE INIT\_B BUSY

#### **Interner Konfigurationskontroller**

Quelle: XILINX- Carl Carmichael, Chen Wei Tseng - XAPP989 - Correcting Single-Event Upsets with a Self-Hosting Configuration Management Core 21.Februar 2011 Folie 10

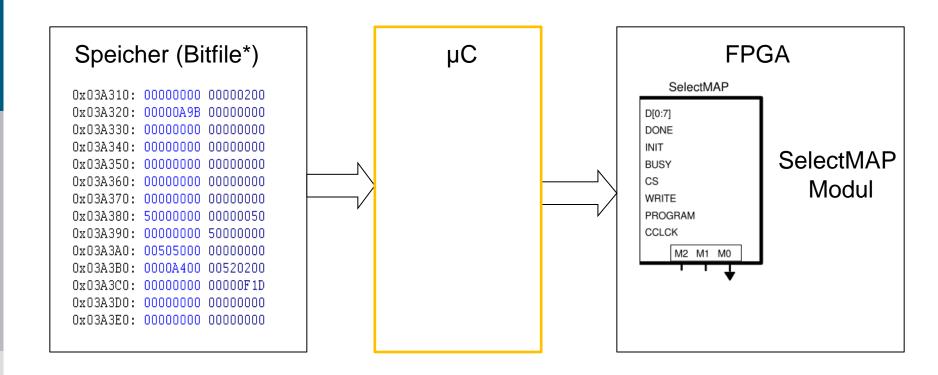

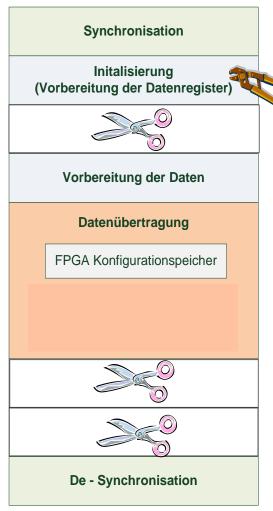

### Realisierung: Re – Konfiguration mittels µC & SelectMAP JÜLICH

#### **Nachteil:**

externer µC → Anfällig gegen Störeinflüsse

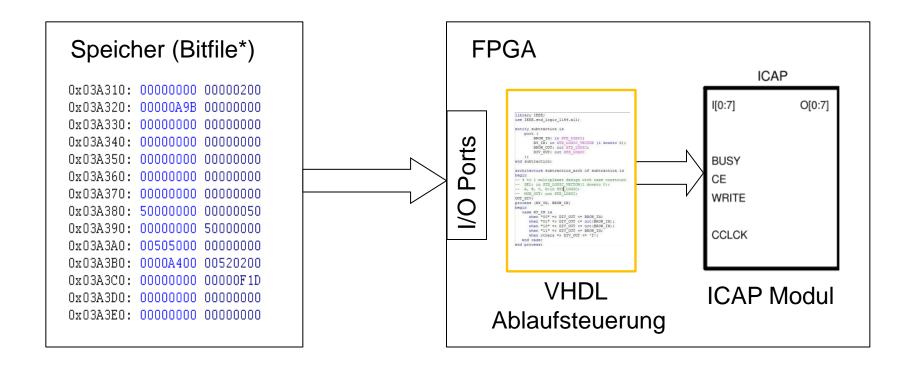

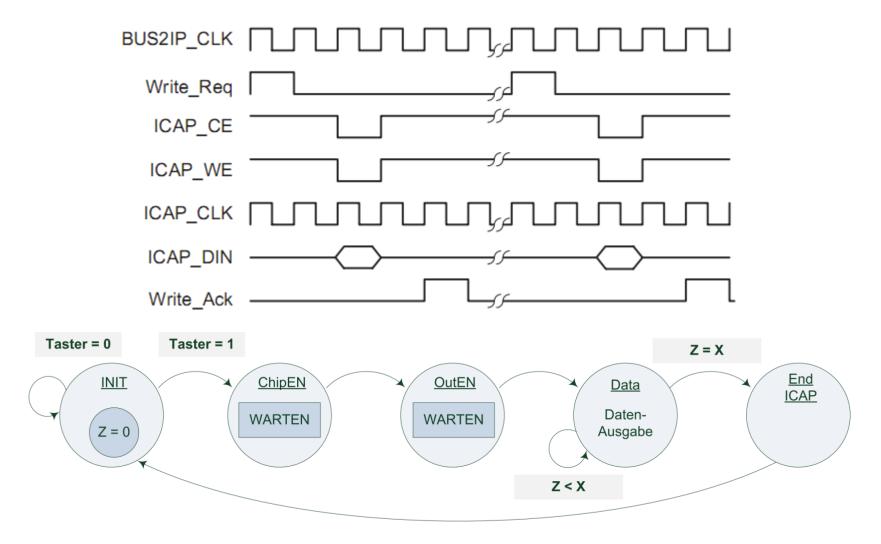

#### Realisierung: VHDL Statemachine fürs ICAP

Folie 12

#### Realisierung: VHDL Statemachine fürs ICAP

Quelle Bild (oben): XILINX - Vince Eck, Punit Kalra, Rick LeBlanc, and Jim McManus – XAPP662 - In-Circuit Partial Reconfiguration of RocketIO Attributes

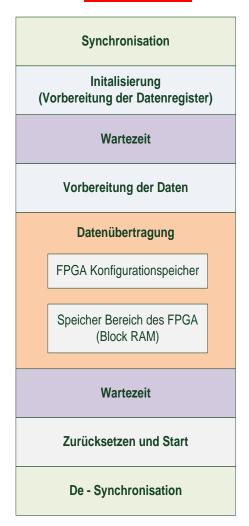

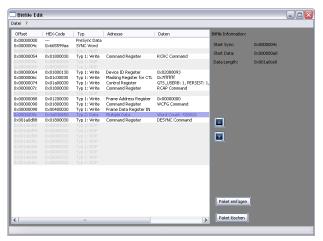

#### Realisierung: Bearbeitung der Binärdatei

#### <u>Binärdatei</u>

#### **Bearbeitung**

#### Binärdatei\*

#### Realisierung: Vorbereitung der SEU Tests

#### **Texteditor**

1. Binärdatei (Lauflicht "links.bit")

2. Binärdatei\*

(Für die Re – Konfiguration "links\_SR.bit")

3. Binärdatei\_SEU ("links\_SEU")

```

0x03A310:

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

```

# Testumgebung

#### Realisierung: Aufbau der Testumgebung

## Messergebnisse

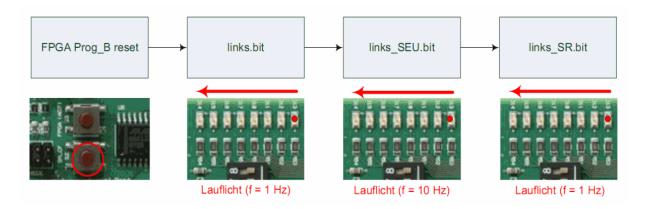

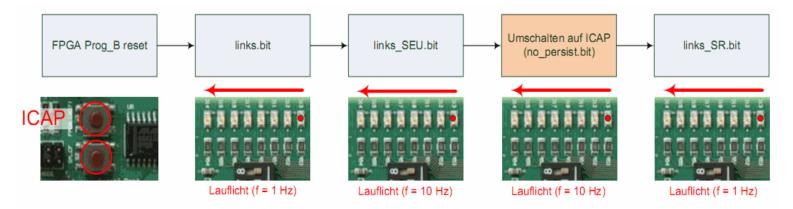

#### Messergebnisse: Test "LAUFLICHT"

#### **SelectMAP:**

#### **ICAP**:

#### Messergebnisse: Dynamische Re - Konfigurierung

#### <u>SelectMAP Schnittstelle:</u>

Externer Mikrokontroller → Speicher Beschränkung → Übertragung von mehreren Paketen → Übertragung im Bereich von mehreren Sekunden

#### **ICAP Schnittstelle:**

Interner Ablaufsteuerung → Re - Konfiguration im Bereich von 85ms

# Zusammenfassung & Ausblick

#### **Zusammenfassung und Ausblick:**

Neue Sicherungstechnologien zum Einsatz eines FPGA im Weltraum wurden erarbeitet:

- Re Konfiguration mittels ICAP

- → Ablaufsteuerung für die ICAP Schnittstelle

- → Softwareoberfläche zur Bearbeitung der Binärdateien

- → Kein externer Mikrocontroller notwendig

- → Dynamische Re Konfiguration in ca. 85ms

- → Ausblick: Implementierung der ICAP Ablaufsteuerung in TMR Technik

- Erweiterung der Software für den Einsatz von Virtex 5 FPGA Bausteinen (Xilinx)

Abschließend möchte ich mich bei Herrn Jano Gebelein und Herrn Norbert Abel von der Universität Heidelberg für die Unterstützung, bei der Anpassung der Binärdatein, bedanken.

#### Vielen Dank für Ihre Aufmerksamkeit!

Haben Sie noch Fragen?

m.dick@fz-juelich.de