### PETRAIV. NEW DIMENSIONS

## **DAMC-X3TIMER**

Update of the development

Hendrik Lippek in behalf of the PETRA IV Timing & synchronisation project team (WP2.09) Hamburg 07.12.2023

HELMHOLTZ

12th MTCA Workshop for Research and Industry

DESY.

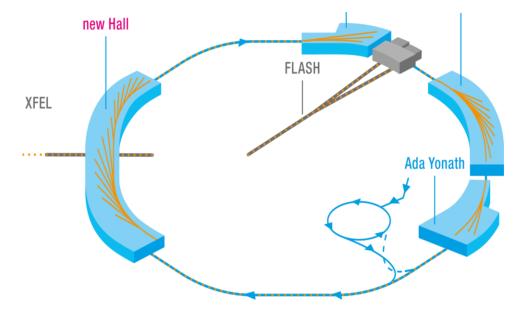

### **PETRA IV Overview**

#### **PETRA IV Highlights**

- 4<sup>th</sup> Generation Light source

- Iow emittance: hor. 10-30 pm rad, vert. < 10 pm rad</p>

- > 500 MHz + 1.5 GHz RF

- timing / brightness mode: 80 / 1600 Bunches

- Injector chain with

- LINAC II, PIA + (new) DESY IV booster synchrotron

- LPA for 6 GeV "Moonshot" into PETRA IV option

- 30 Beamlines in 4 Experimental Halls

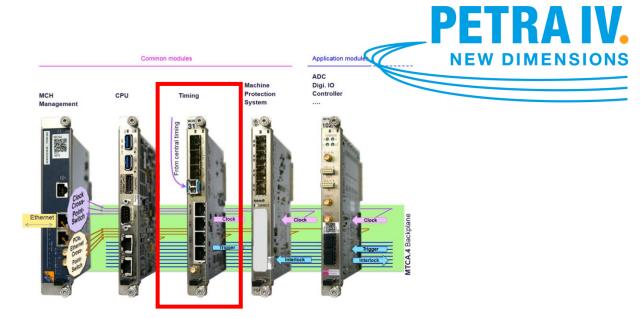

#### Timing System development for PETRA IV

- MicroTCA.4 components will replace existing PETRA III hardware for controls and diagnostics

- A new MTCA based timing distribution hardware replaces the old system based on VME, SEDAC, 19" standards

- Make use of experience from well-established Timing System concepts as utilized at the FLASH and European XFEL facility

- Keep the design flexible to enhance functionality during lifecycle of PETRA IV

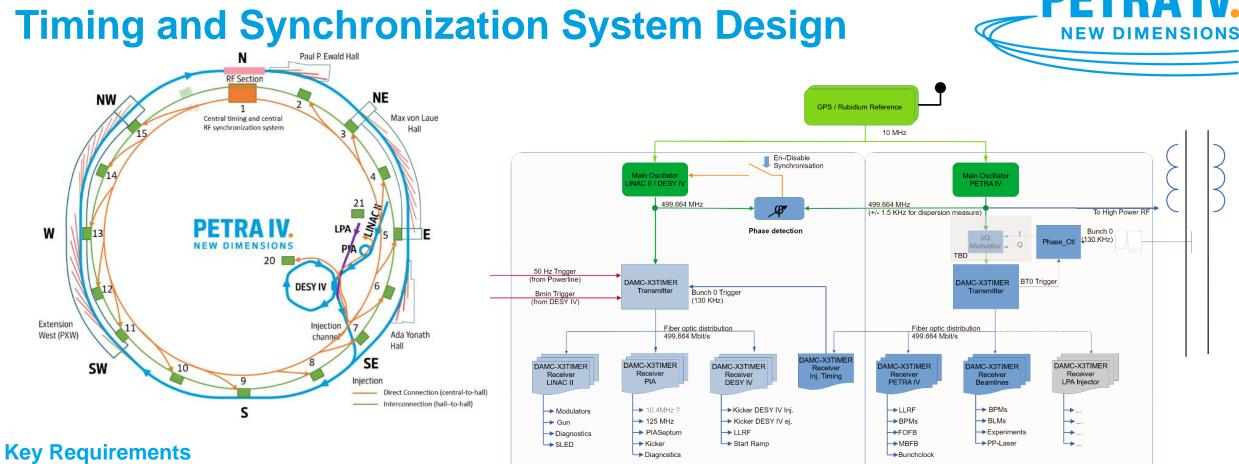

Injection Timing

- Ney Nequirements

- Distributing a continuous RF reference signal

- Provide low jitter clocks (e.g. for ADC sampling)

- Provide continuous timing signals & trigger events

- Provide beam-synchronous data as:

- Timestamp / revolution counter

- Beam mode / bunch pattern

- bunch currents

Common hardware for timing transmitter and receiver

PETRA IV Timina

- Dedicated fiber optic distribution with drift compensation

- Common timing system for accelerator and beamlines

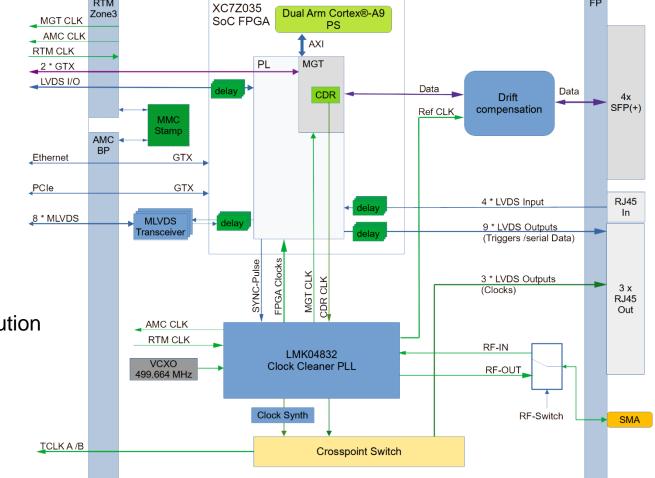

### **DAMC-X3TIMER Block Design**

#### **Front Panel**

- SFP  $\geq$

- SMA  $\geq$

- RJ45  $\geq$

- RJ45  $\geq$

- USB  $\triangleright$

- timing signal distribution

- RF-Input / RF-Output

- LVDS Out (Triggers, CLK, Data)

- LVDS In (Sync signal, Trigger)

- Debug/JTAG

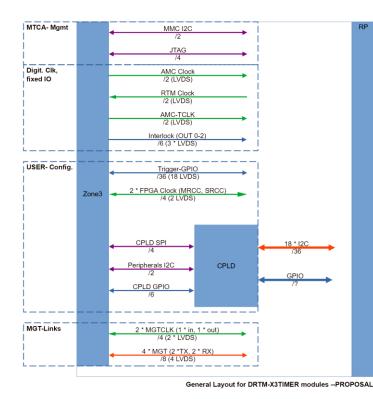

#### **AMC** - Backplane

- PCle  $\succ$

- Ethernet  $\triangleright$

- TCLK A/B  $\geq$

- Port 17-20

- IPMI to MMC  $\geq$

- Communication to MTCA-CPU

- For Zynq SoC PS

- clock distribution

- M-LVDS Trigger/Clock/ Data distribution

- Management, Firmware update

#### RTM Zone 3 (Class D1.1)

- MGT lanes  $\geq$

- > LVDS

- > SPI / I2C

- timing signal distribution

- Trigger / Clocks / Data

- for peripherals configuration

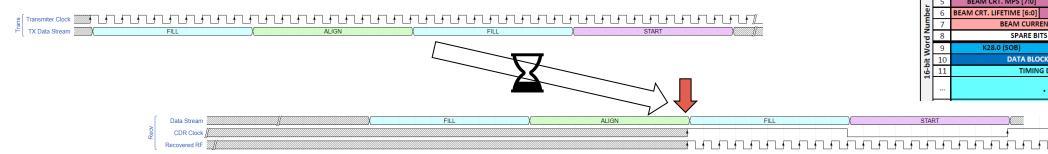

### **Transmitter – Receiver concept**

#### **Transmitter**

- Generates RF synchronous Datastream

- Encodes timing information into data frame

- Aligns Datastream (K28.5) to the beam (Bunch 0 marker)

- 8B/10B extended transmission over MGT transceivers

- Active drift compensated distribution path

#### Receiver

- Recovers Clock from Datastream in MGT

- Jitter Cleans CDR Clock with dual loop PLL

- > Alignment:

- Decodes Alignment characters (K28.5) in the data

- Align LMK04832 output Clock phases

- Distributes RF derived divider clocks

- Delivers decoded Trigger signals

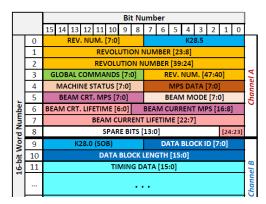

#### Timing Data Frame @~500 MHz (3840 bits x ~130.1 kHz)

Courtesy of V. Andrei

DESY. Update on the DAMC-X3TIMER Development | Hendrik Lippek | 12th MTCA Workshop for Research and Industry, 07.12.2023

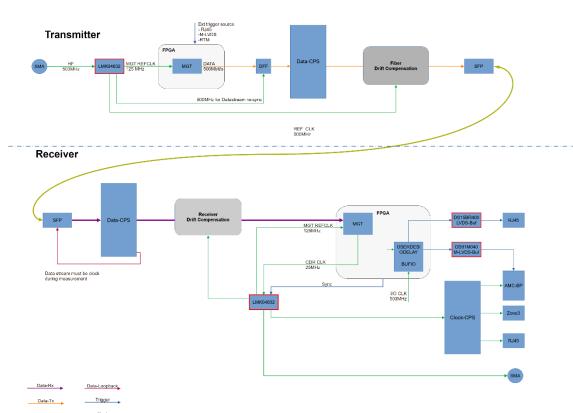

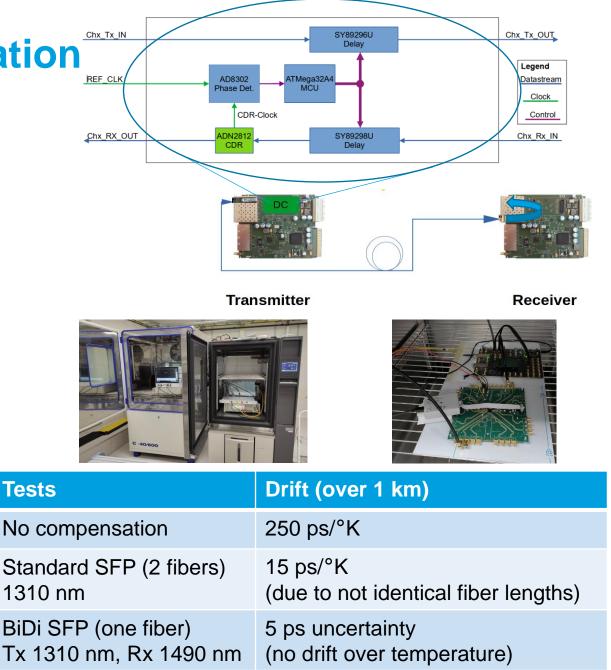

### **Transmitter: Fiber Drift Compensation**

#### Active drift compensation on Transmitter side

- Detect phase differences between local reference and recovered clock from looped back data stream

- Sets delays to keep the phase relation constant

- separate module option to keep Receiver BoM cost low

- receivers or applications with no critical drift requirements

#### Drift stability tests with x2timer hardware

Environmental chamber tests were used to investigate clock and trigger signal drifts over variation on temperature and humidity. Two aspects were investigated:

#### Drifts on optical fiber and active drift compensation

- ➤ Test setup

- 2 x2timer Transmitter & Receiver

- > 1 km of optical fiber as signal path

- Standard SFP Transceiver

- > vs. wavelength multiplexing BiDi SFP Transceiver

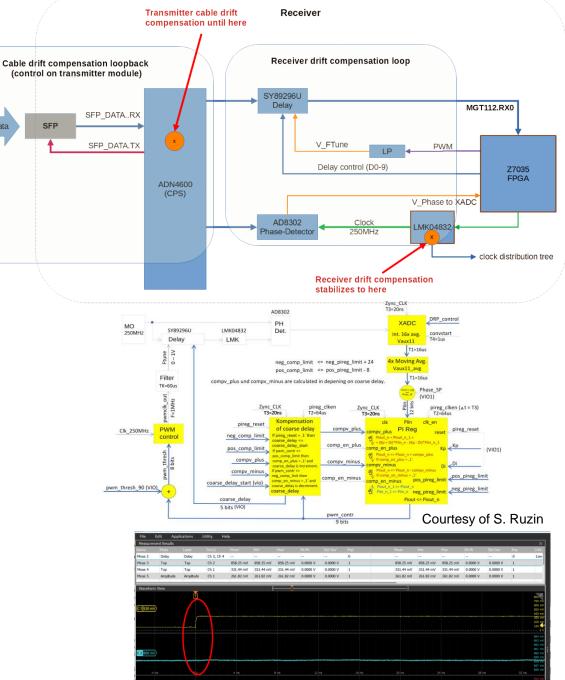

### **Receiver: Active Drift Stabilization**

#### Why do we need more stabilisation?

- Thermal drifts in the compensation loop are compensated well

- > There is still drift in the out of loop components

- Dividers /Crosspoint-Switches /FPGA

- Temperature changes by MTCA Fan activities have a big influence on AMC temperature and component drifts

#### What can we do?

- Room / Rack / Crate level

- temperature & humidity controlled electronics room

- Use (water)-cooled Racks

- Set Crate to steady air stream configuration

#### PCB level

- Reduce amount of critical components

- LMK04832 contains also divider, delay and multiplexer

- Cleaned up clock and data distribution path

- Receiver drift compensation

- Compensates drift in FPGA CDR and clock cleaner

- Optional on board temperature regulation

- Control temperature of critical IC components

- Local FET based heating loop

500MBit/s Data

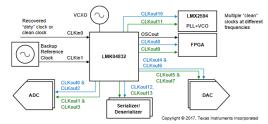

### **Clock jitter cleanup**

#### Clock Cleaner (TI LMK04832)

- Dual loop PLL

- PLL1: custom VCXO (KVG V7221-EP-LF)

- PETRA: 499.6643 MHz +/-100 ppm

- Can be customized to Acc Frequencies

- PLL2: internal VCO

- 3 Clock inputs (RF, CDR, Aux)

- internal output dividers

- Digital output delays

- programmable output levels (LVDS, LVPECS, CMOS,..)

#### **Test Setup**

- RF-Generator (R&S SMA100A)

- Transmitter: DAMC-FMC1Z7IO (With SFP-FMC)

- Receiver: Trenz TE0745 Evaluation board

- Fiber connection:

- ➤ 1 KM single mode

- BiDi SFP Modules Tx 1310 / Rx 1490 nm

- > 50 GS/s Oscilloscope with Jitter & phase noise analyzer

Simplified Schematic

| Option            | Description                  | Phase noise*     |

|-------------------|------------------------------|------------------|

| No jitter cleaner | Clock from CDR               | 45 ps            |

| Single loop       | LMK04832 internal VCO only   | 1-3 ps           |

| Dual loop         | custom VCXO and internal VCO | 397 fs           |

|                   |                              | *100 Hz – 10 MHz |

### **RTM Interface**

#### Zone 3 (RTM-Connector)

RTM Class D1.1

- > 3 Clocks (AMC- /TCLK out, RTMCLK in)

- > 18 Trigger outputs

- 2 FPGA Clocks (Clock capable I/O)

- > SPI / I2I / GPIO / JTAG

### ➢ 2 MGT (TX, RX, REFCLK)

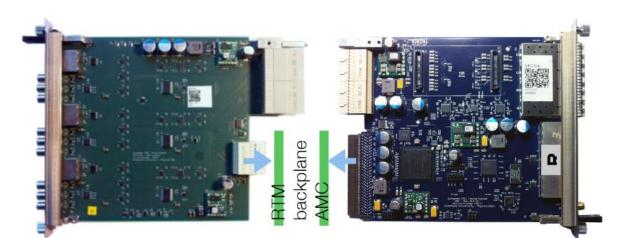

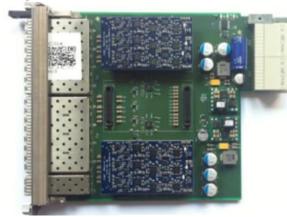

#### **RTM types**

- Rear panel interfaces

- ≻ LEMO

- SMA Clock output (with LNA)

- > LVDS

- > Optical

- > NIM?

- RF-Backplane interface

- Clock distribution

- Functional

- Programmable delay line

- SFP Fanout module

Pictures from x2timer RTM modules

### **Summary**

Improvements in the DAMC-X3TIMER design:

Jitter reduction by using a clock cleaner

#### > Better drift stability

- Usage of BiDi SFP/SFP+ transceivers

- Receiver drift compensation

- Thermal stabilization of board components

#### Enhanced onboard processing capabilities

- Real-time bunch delay calculation

- Local control servers

- Flexible configuration of peripherals

## More flexibility by the use of in-house software & firmware framework solutions

- Interfacing to various control systems

- Modular firmware for easy portability

# DOOCS. Fred Firman France france vork

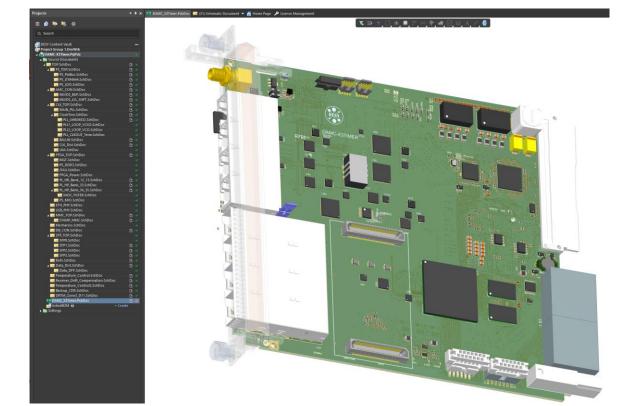

#### **Schematics**

48 Pages of schematics compete

#### PCB

- Board shape designed

- Connectors placed

- Main components placed

- FPGA SoC and peripherals routed

- Power supplies placed and routed

#### **Production**

- Components checked for availability

- Main components ordered & stocked

- > In contact with assembly companies

- First Prototype production planned in early 2024

#### Thank you for your attention!

#### Contact

**DESY.** Deutsches Elektronen-Synchrotron

Hendrik Lippek MSK

www.desy.de

hendrik.lippek@desy.de

DESY.

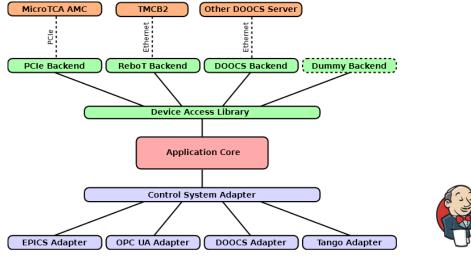

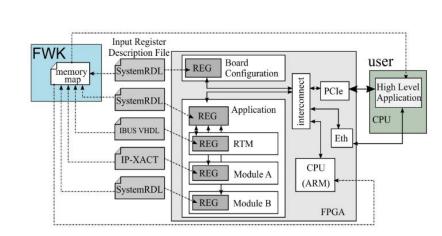

### **Firmware Framework & software interface**

#### **MSK firmware framework**

- Generic framework for various (Xilinx) FPGAs

- Maintained by MSK firmware group

- Register maps for software interface

- Supports also ARM core interface for SoC devices

- Middle layer to abstract hardware and control system

- Supports multiple controls systems

- Uses Xilinx xdma driver to access FPGA via PCIe

- Support to run on (Zynq) ARM cores in preparation

- Public available: https://github.com/ChimeraTK

### **WSK** GitLab