## FCC-ee vertex simulations ... and more!

Vertex Detector Discussion Meeting at DESY

#### **Armin Ilg**

University of Zürich

06.05.2024

## FCC-ee detector concepts

CLD: CLIC-Like Detector [1, 2].

- ILC  $\rightarrow$  CLIC  $\rightarrow$  FCC-ee ( $\rightarrow$   $\mu$ Col)

- Si vertexing and tracking

- Highly-granular ECAL and HCAL, CALICE-like

- Solenoid coil outside calorimeter system

IDEA: Innovative Detector for  $e^+e^-$ Accelerators [3, 4].

- Si vertexing

- Drift chamber (down to 1.6% X/X0, dN<sub>ion.</sub>/dx)

- Si wrapper with timing

- Dual-readout calorimeter with preshower

- Solenoid coil inside calorimeter system

Experiment with highly GRanular calorimetry Read-Out (M. Aleksa).

- Si vertexing and drift chamber

- Highly granular noble liquid ECAL, Pb/W+LAr or W+LKr

- ECAL and solenoid coil in same cryostat

- CALICE-like or TileCal-like HCAL

####

CLD: CLIC-Like Detector [1, 2].

- ILC ightarrow CLIC ightarrow FCC-ee (ightarrow  $\mu$ Col)

- Si vertexing and tracking

- Highly-granular ECAL and HCAL, CALICE-like

- Solenoid coil outside calorimeter system

IDEA: Innovative Detector for  $e^+e^-$ Accelerators [3, 4].

- Si vertexing

- Drift chamber (down to 1.6% X/X0, dN<sub>ion</sub> /dx)

- Si wrapper with timing

- Dual-readout calorimeter with preshower

- Solenoid coil inside calorimeter system

Experiment with highly GRanular calorimetry Read-Out (M. Aleksa).

- Si vertexing and drift chamber

- Highly granular noble liquid ECAL, Pb/W+LAr or W+LKr

- ECAL and solenoid coil in same cryostat

- CALICE-like or TileCal-like HCAL

## FCC-ee detector concepts + variations (RICH, crystal ECAL, ...) University of Zurich

CLD: CLIC-Like Detector [1, 2].

- ILC ightarrow CLIC ightarrow FCC-ee (ightarrow  $\mu$ Col)

- Si vertexing and tracking

- Highly-granular ECAL and HCAL, CALICE-like

- Solenoid coil outside calorimeter system

IDEA: Innovative Detector for  $e^+e^-$  Accelerators [3, 4].

- Si vertexing

- Drift chamber (down to 1.6% X/X0, dN<sub>ion.</sub>/dx)

- Si wrapper with timing

- Dual-readout calorimeter with preshower

- Solenoid coil inside calorimeter system

Experiment with highly GRanular calorimetry Read-Out (M. Aleksa).

- Si vertexing and drift chamber

- Highly granular noble liquid ECAL, Pb/W+LAr or W+LKr

- ECAL and solenoid coil in same cryostat

- CALICE-like or TileCal-like HCAL

#### University of FCC-ee detector concepts + variations (RICH, crystal ECAL, ...)

Not only do all Higgs factories foresee silicon pixel sensors for the vertex detectors, they all foresee specifially Depleted Monolithic Active Pixel Sensors (DMAPS) calorimetry Read-Out (M. Aleksa).

- ILC  $\rightarrow$  CLIC  $\rightarrow$  FCC-ee ( $\rightarrow$  $\mu$ Col)

- Si vertexing and tracking

- Highly-granular ECAL and HCAL. CALICE-like

- Solenoid coil outside calorimeter system

- Si vertexing

- Drift chamber (down to 1.6% X/X0,  $dN_{ion}/dx$ )

- Si wrapper with timing

- Dual-readout calorimeter with preshower

- Solenoid coil inside calorimeter system

- Si vertexing and drift chamber

- Highly granular noble liquid ECAL, Pb/W+LAr or W+LKr

- ECAL and solenoid coil in same cryostat

- CALICE-like or TileCal-like **HCAL**

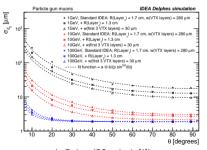

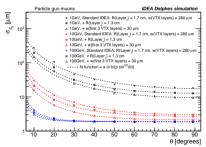

## FCC-ee vertex detector layouts

See August's talk tomorrow for detailed discussion on FCC-ee vertex requirements

**CLD** → Rescaled CLICDet vertex detector

- $r_{min} = 13 \text{ mm}$ , vertex system until r = 112 mm, z = 300 mm

- Three double-layer barrel layers and disks

- No engineering studies since CLICDet developments

**IDEA** → New vertex detector layout

F. Palla, see talk at FCC US week at BNL

- $r_{min} = 13.7$  mm, vertex system until r = 315 mm, z = 930 mm

- Three single-layer barrel layers

- Two outer barrel layers and three disks

- Engineered design, integrated into MDI

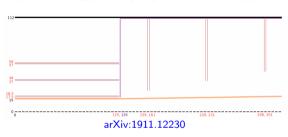

## FCC-ee vertex detector layouts

See August's talk tomorrow for detailed discussion on FCC-ee vertex requirements

$CLD \rightarrow Rescaled CLICDet vertex detector$

**IDEA** → New vertex detector layout

- arXiv:1911.12230

- $r_{\min} = 13 \, \text{mm}$ , vertex system until  $r = 112 \, \text{mm}, z = 300 \, \text{mm}$

- Three double-layer barrel layers and disks

- No engineering studies since CLICDet developments

- F. Palla, see talk at FCC US week at BNL

- $r_{\min} = 13.7 \, \text{mm}$ , vertex system until  $r = 315 \, \text{mm}$ .  $z = 930 \, \text{mm}$

- Three single-layer barrel layers

- Two outer barrel layers and three disks

- Engineered design, integrated into MDI

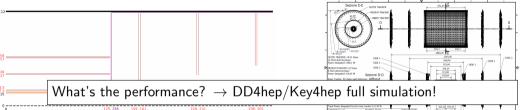

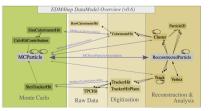

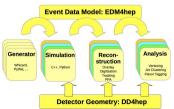

## The common software vision: Key4hep

Key4hep is a huge ecosystem of software packages adopted by all future collider projects, complete workflow from generator to analysis

- Event data model: EDM4hep for exchange among framework components

- Podio as underlying tool, for different collision environments

- Including truth information

- Data processing framework: Gaudi

- Geometry description: DD4hep, ability to include CAD files

- Package manager: Spack: source /cvmfs/sw.hsf.org/Key4hep/setup.sh

#### CLD vertex detector full simulation

#### Detector model in k4geo

- Linear collider reconstruction (iLCSoft/CLICPerformance)

- Can generate EDM4hep output using k4MarlinWrapper

Access to all LC tools: PandoraPFA, LCFI+, etc.

Updated CLD vertex (G. Sadowski, 7th FCC Physics Workshop)

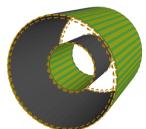

CLD vertex barrel

CLD endcap and vertex barrel

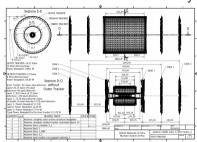

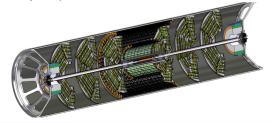

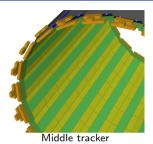

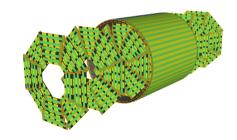

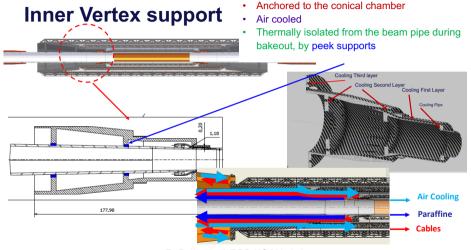

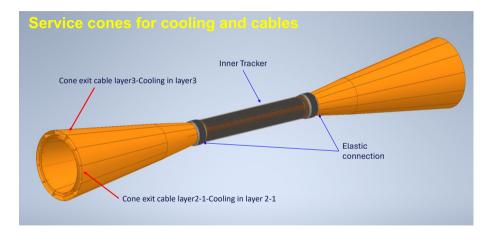

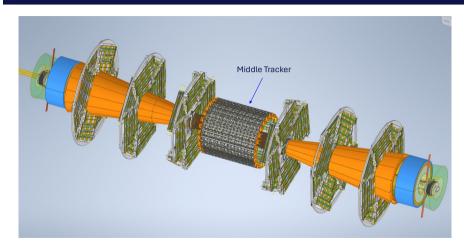

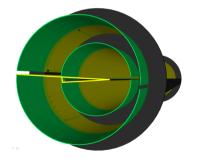

## IDEA vertex detector: Design

Vertex detector by INFN Pisa (more details in F. Palla's talk at 2nd FCC US Workshop), support tube by INFN-LNF, holding lumical, vertex and beam pipe (more on MDI in M. Boscolo's talk)

Vertex outer barrel and vertex disks using quad ATLASPix3 DMAPS with  $150\times50~\mu\text{m}^2$  pixels, water-cooled

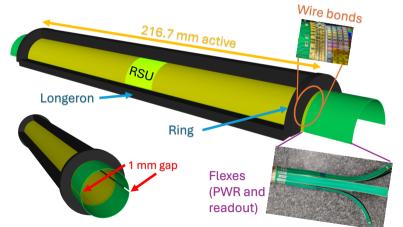

#### Vertex inner barrel

- $r_{min} = 13.7 \text{ mm}$ , 2 mm to beam pipe (can we go closer?)

- Correct material stack, flexes, end-of-stave hybrid, insensitive sensor areas (2 mm)

- Proxy volume for stave holding structure

- Support structure CAD model can be imported (more details in backup), service cones missing

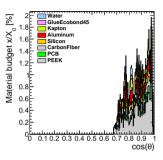

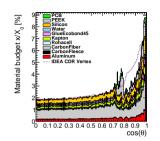

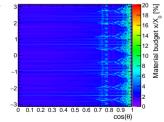

- Material budget in line with 0.3% per layer at  $cos(\theta) = 0$  (CDR assumption)

First laver

Vertex inner barrel, without support

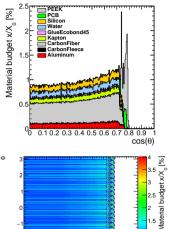

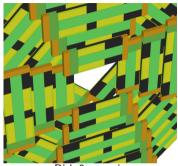

#### Vertex outer barrel

- Correct material stack, correct description of ATLASPix3 insensitive peripheries

- Proxy volumes for truss structure and cooling pipes

- Proxy volume for end-of-stave holder (orange, material budget contribution optimised with F. Palla)

- Still significant contribution

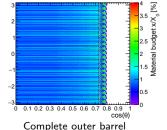

Complete vertex outer barrel system

#### Vertex disks

- Correct placement of all modules in r and z

- Missing vertex disk global support

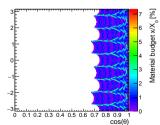

- Very uneven  $x/X_0$  distribution

Disk 0

Disk 0 zoom-in

Complete vertex disks system

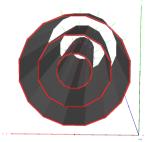

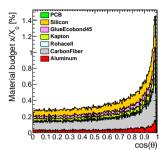

## Complete system

Complete vertex system

- Material budget comparable with CDR estimate

- First working version on k4geo, update imminent with some fixes (getting rid of last overlaps)

- Plan to include last missing volumes using DDCAD

- Look at all material budget evaluations as a lower limit, there's always gonna be more added! (e.g off-detector cabling)

- ullet No drift chamber tracking available yet o instead use CLD and iLCSoft reconstruction

- Frankenstein approach: Remove CLD vertex detector (and a couple of Inner Tracker layers and disks) and instead insert IDEA vertex, run CLD full simulation

- Results foreseen for FCC Week next month

- How can we further improve vertex detector performance?

## Sensor-only vertex detector

#### DMAPS in 65 nm TPSCo process

- More logic per cm<sup>2</sup>

- ullet Lower power consumption o Air cooling

- Enables 12" wafers  $\rightarrow$  Wafer-scale bent sensors!

## Sensor-only vertex detector

#### DMAPS in 65 nm TPSCo process

- More logic per cm<sup>2</sup>

- ullet Lower power consumption o Air cooling

- Enables 12" wafers  $\rightarrow$  Wafer-scale bent sensors!

Material budget in ALICE ITS2 (left, [7]) and silicon only (M. Mager)

Layer assembly concept for ALICE ITS3 [6]

L. Freitag (BSc. thesis [8])

## Sensor-only vertex detector

#### DMAPS in 65 nm TPSCo process

- More logic per cm<sup>2</sup>

- ullet Lower power consumption o Air cooling

- Enables 12" wafers  $\rightarrow$  Wafer-scale bent sensors!

Layers 2+1

Layer assembly concept for ALICE ITS3 [6]

L. Freitag (BSc. thesis [8])

Material budget in ALICE ITS2 (left, [7]) and silicon only (M. Mager) L. Freit How can such a vertex detector be realised at FCC-ee?  $\rightarrow$  See also here

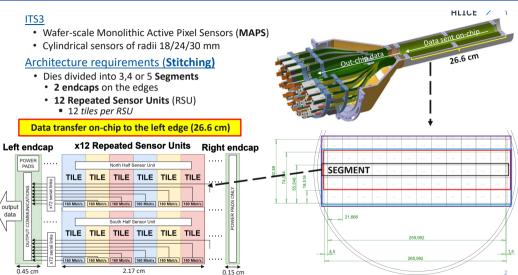

### ALICE ITS3 lavout

M. Rodriguez @ TWEPP 2023

#### Differences between ALICE ITS3 and FCC-ee

- First layer at smaller radius, from 18 to 13.7 mm

- → Mechanically okay, electrically to be demonstrated

- → First layer to use just two segments to reach smaller radius

- $\bullet$  ITS3 readout only in one direction  $\to$  We want to measure forward-backward asymmetries extremely precisely

- → Read and power from both sides where possible

- ITS3 doesn't care too much about forward coverage

- ightarrow We do. down to  $heta=140\,\mathrm{mrad}$

- ightarrow Need to find solution for 3rd and 4th layer! ightarrow Multiple wafer-scale sensors in a row in z

- → Ensure flexes, cables, etc. are not in front of lumical

- ullet ITS3 doesn't care too much about hermeticity o We do.

- → Cannot overlap multiple staves/ladders as in ATLAS/CMS

- $\rightarrow$  Evaluate impact of only  $\sim 95\%$  coverage per layer (chip service region and gap between sensors)

- $\rightarrow$  Increase number of layers from 3 to 4 to ensure at least three hits

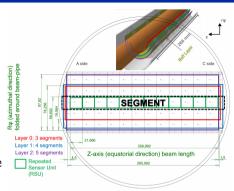

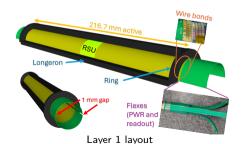

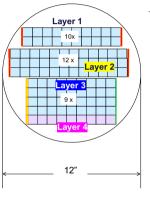

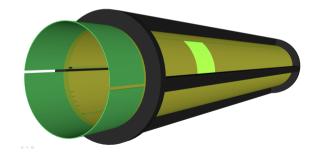

## Ultra-light vertex concept principles

#### Layer 1 and 2

- Coverage down to 125 mrad (155 mrad) for layer 1 (layer 2)

- ullet Gap of 1 mm between half-barrels, layer 2 rotated in  $\phi$  by  $8^\circ$  to avoid overlap with layer 1

- Readout and power from both sides

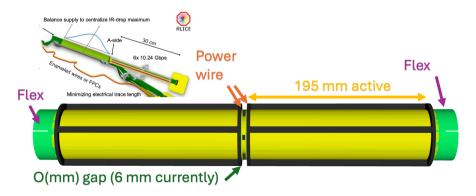

#### Layer 3 and 4

• Two sensors per side, readout only on sides, power on sides and center (power wire)

Layer 1+2

z = region with layer 3 and 4

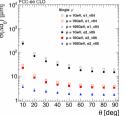

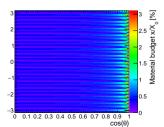

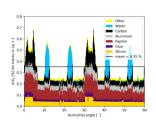

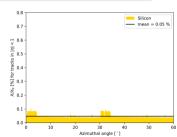

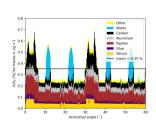

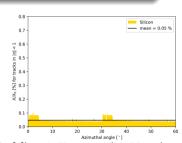

## First material budget evaluation (preliminary!)

Ultra-light layer 1

Ultra-light layer 1 ( $cos(\theta)$  vs.  $\phi$ )

Ultra-light layer 1-4

Material budget reduction of  $\sim$  5, uniform distribution in  $\phi$  except for longeron locations

## UZH current and planned activities

#### MAPS R&D towards FCC-ee vertex detectors

- APTS Source Follower characterisation last year

- Comparing different collection electrode designs

- Studying in-pixel efficiency

- CE-65 characterisation since last year

- → Continue with 65 nm development, hopefully together with many other institutes!

#### FCC-ee detector simulation

- Implemented IDEA vertex detector (and Silicon Wrapper) in DD4hep

- Study IDEA vertex detector performance

- Investigate ultra-light vertex detector concept

- Study beam backgrounds in IDEA vertex

- Started hit digitisation inside Key4hep using Allpix<sup>2</sup>-generated LUT à la M. Bomben

R. Wittwer, TREDI2024

Establishing Swiss FCC initiative, with planned focus on vertex detector development

## Vertex detector discussion points (together with A. Macchiolo)

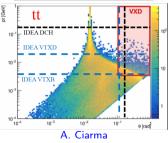

- With trigger ( $\sim$  200 kHz rate) or without? • Problem is incoherent pair background in first vertex layer

- Occ =  $70 \times 10^{-6}$ . 25  $\mu$ m pixels  $\rightarrow$  1 GHz hit rate  $\rightarrow$  with trigger  $O(150 \,\mathrm{Mb/s})$ , without trigger  $O(25 \,\mathrm{Gb/s})$  per  $25.6 \times 6.4 \,\mathrm{mm}^2$  ARCADIA module (see F. Bedeschi)

- Impact on power consumption (→ and material budget)?

- n.b: Safety factor of 5 and cluster size of 3 assumed. L increased since study

- Connected to choice of high vs. low charge sharing sensor

How good should the spatial resolution be? At what cost?

#### Are curved wafer-scale MAPS feasible for FCC-ee?

No show-stopper so far

#### Technologies for ultimate vertex detector performance

- Wireless readout, on-detector intelligence

- Vertex inside beam pipe (ALICE3), but beware of wakefield induced heat!

Table 2: Number of pairs produced per bunch crossing (BX) at the four working points, and maximum occupancy measured in the barrel and endcaps of the vertex detector and tracker (respectively VXDB, VXDE, TRKB, TRKE).

|           |                 | Z    | $\mathbf{w}\mathbf{w}$ | ZH   | tī   |

|-----------|-----------------|------|------------------------|------|------|

| 1         | Pairs/BX        | 1300 | 1800                   | 2700 | 3300 |

| $10^{-6}$ | $O_{max}(VXDB)$ | 70   | 280                    | 410  | 1150 |

| $10^{-6}$ | $O_{max}(VXDE)$ | 23   | 95                     | 140  | 220  |

| $10^{-6}$ | $O_{max}(TRKB)$ | 9    | 20                     | 38   | 40   |

| $10^{-6}$ | $O_{max}(TRKE)$ | 110  | 150                    | 230  | 290  |

# Thanks!

#### References I

- [1] N. Bacchetta, et al., CLD A Detector Concept for the FCC-ee, arXiv:1911.12230 [physics.ins-det].

- [2] D. Dannheim, et al., CERN Yellow Reports: Monographs, Vol 1 (2019): Detector Technologies for CLIC, tech. rep., 2019.

- [3] IDEA Collaboration, G. F. Tassielli, A proposal of a drift chamber for the IDEA experiment for a future e<sup>+</sup>e<sup>-</sup> collider, in Proceedings of 40th International Conference on High Energy physics — PoS(ICHEP2020).

Sissa Medialab. Feb., 2021.

- [4] FCC Collaboration, FCC-ee: The Lepton Collider, The European Physical Journal Special Topics 228 (2019) 261-623.

- [5] S. Amrouche, et al., The Tracking Machine Learning Challenge: Accuracy Phase, pp., 231–264.

Springer International Publishing, Nov., 2019.

https://doi.org/10.1007/978-3-030-29135-8\_9.

- [6] M. Mager, On the "bendable" ALPIDE-inspired MAPS in 65 nm technology, 11, 2021. https://indico.ihep.ac.cn/event/14938/session/6/contribution/196. 2021 International Workshop on High Energy Circular Electron Positron Collider.

- 7] F. Reidt, Upgrading the Inner Tracking System and the Time Projection Chamber of ALICE, Nuclear Physics A 1005 (2021) 121793.

- [8] L. Freitag, Benefits of Minimizing the Vertex Detector Material Budget at the FCC-ee, 2023. http://cds.cern.ch/record/2851362. BSc thesis, presented 01 Feb 2023.

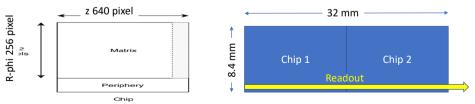

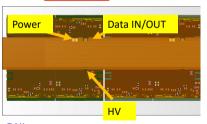

#### Vertex detector module

Istituto Nazionale di Fisica Nucleare

#### Module concept inspired by **ARCADIA** INFN R&D

- Depleted Monolithic Active Pixel Detectors (DMAPS) sensor and back-side processing already tested on silicon

- Pixel size 25x25 µm<sup>2</sup>, 50 µm thick

- Active area 640 pixel (16 mm) in z and 256 pixels (6.4 mm) in  $r-\phi$

- Chip periphery plus an inactive zone: total of 2 mm in  $r \varphi$

- · Chips are side-abuttable in z

## Composed of 2 pixelated parts: total of 8.4 mm $(r - \varphi) \times 32$ mm (z)

- Power budget not established yet: assume (reasonably)  $50 \text{ mW/cm}^2$

F. Palla, see talk at FCC US week at BNL

#### Outer tracker module

- Based on ATLASPIX3 R&D

- DMAPS

- 50 x 150 µm<sup>2</sup>

- Up to 1.28 Gb/s downlink

- TSI 180 nm process

- 132 columns of 372 pixels

- Active (total) length (r-phi x z)

18.6 (21) mm x 19.8 (20.2) mm

- Module is made of 2x2 chips total length:

- size 42.2 mm x 40.6 mm

- Power budget not established yet: assume 100 mW/cm<sup>2</sup>

o Nazionale di Fisica Nucleare

F. Palla , see talk at FCC US week at BNL

F. Palla, 2nd FCC US Workshop

## Data rates issues (see F. Bedeschi talk at 7th FCC Workshop)

- Largest data rates occur at the Z energy

- Expected data rates per BX/module [cluster size 5]

- From machine backgrounds (Incoherent pair creation safety factor of 3) ~ 19 hits/BX/module

- From collisions (200 kHz) ~ average ~<1 hit/BX/module</li>

- Inner layer ~400 MHz/cm<sup>2</sup> → ~25 Gb/s per module

- might be reduced if cluster size is only 2 as measured for many MAPS

- ALICE3 hit rate ~100 MHz/cm² (pixel size 10μm x 10μm)

- 2<sup>nd</sup> layer ~10x less data volume

- Triggered readout: for 200 kHz the data bandwidth per module, rate is only 150 Mb/s

- · Impact on physics?

- All these depend on pixel pitch, thickness, R/O architecture, bias voltage.

- · For a review see M. Winter talk at March 11 meeting

F. Palla, 2nd FCC US Workshop

#### Same reticle for all layers

| Layer | Radius<br>(mm) |  |

|-------|----------------|--|

| 1     | 13.7           |  |

| 2     | 20.23          |  |

| 3     | 26.76          |  |

| 4     | 33.3           |  |

Layer 1&2

Layer 3&4

|                                                | Powe<br>[mV      | 1                            |                  |

|------------------------------------------------|------------------|------------------------------|------------------|

|                                                | Expected 25 °C   | $^{ m Max}_{ m 25^{\circ}C}$ | Max<br>45°C      |

| Left End Cap (LEC)                             |                  | 791                          |                  |

| Active area (RSU)                              | 28               | 44                           | 62               |

| Pixel matrix<br>Biasing<br>Readout peripheries | 15<br>168<br>432 | 32<br>168<br>457             | 51<br>168<br>496 |

| Data backbone                                  | 719              | 719                          | 719              |

Power dissipation in ITS3 (not necessarily the same for FCC-ee)

- RSU~ 50 mW/cm<sup>2</sup> (depends on Temp.)

- LEC ~ 700 mW/cm<sup>2</sup>

#### Differences between ALICE ITS3 and FCC-ee

- First layer at smaller radius, from 18 to 13.7 mm

- Mechanically okay, electrically to be demonstrated

- First layer to use just two segments to reach smaller radius

- Assuming same RSU size (= reticle size of CMOS process of given silicon foundry) of  $19.564 \times 21.666 \,\mathrm{mm}^2$  (in  $r - \phi \times z$ ) then radius would be 12.77 mm.

- Can consider more complex approach using edge reticle pieces to reach any desired radius for the first laver

- Assume perfect reticle size in  $r-\phi$  of 21.02 mm to get to r=13.7 mm for the first layer

Right: exposures on the wafer and resulting circuits (not to scale)

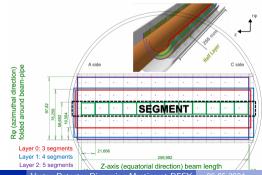

- 10 RSUs and 2 ECs long,  $\theta_{\rm min}=125.8\,{\rm mrad},\ |cos(\theta)|<0.992$  (106.35 mrad assuming 20 mm flex)

- Two half-barrels two segments wide each, 1 mm gap, readout and power from both sides

- 12 RSUs long (limit given 12 inch wafer size), at  $r = 20.39 \,\mathrm{mm}$

- Coverage down to  $\theta_{\rm min} = 155.58 \, {\rm mrad}, \, |cos(\theta)| < 0.991$

- ullet Rotated in  $\phi$  by 8° to avoid overlap with layer 1

- ullet Could slightly twist sensor to minimise gaps in coverage e.g. at z=0, in-between RSUs

- $r = 27.08 \,\mathrm{mm}$ , two sensors per side, with 9 RSUs each

- Coverage down to  $\theta_{\mathsf{min}} = 135.93\,\mathsf{mrad},\, |cos(\theta)| < 0.991$

- Readout on sides, power on sides and center (power wire)

- Same length as layer 3, sensors are five RSUs wide, at r = 33.77 mm

- Simpler mechanical assembly given same length of layer 3 and 4 (sacrificing forward coverage)

- ullet Coverage down to  $heta_{

m min}=168.94\,{

m mrad},\, |cos( heta)|<0.986$

- Gap at z = 0 could be mitigated by having asymmetric design with sensors with 10 and 8 RSUs on the z > 0 and z < 0 sides respectively