#### Source test for pixel single chip detectors - results

Aleksander Gajos, Cracow Daniel Pitzl, DESY

DESY CMS tracker upgrade meeting, 23.8.2011

- pixel cluster analysis

- sensor bias voltage scans

- threshold scan

- plans for the DESY Testbeam

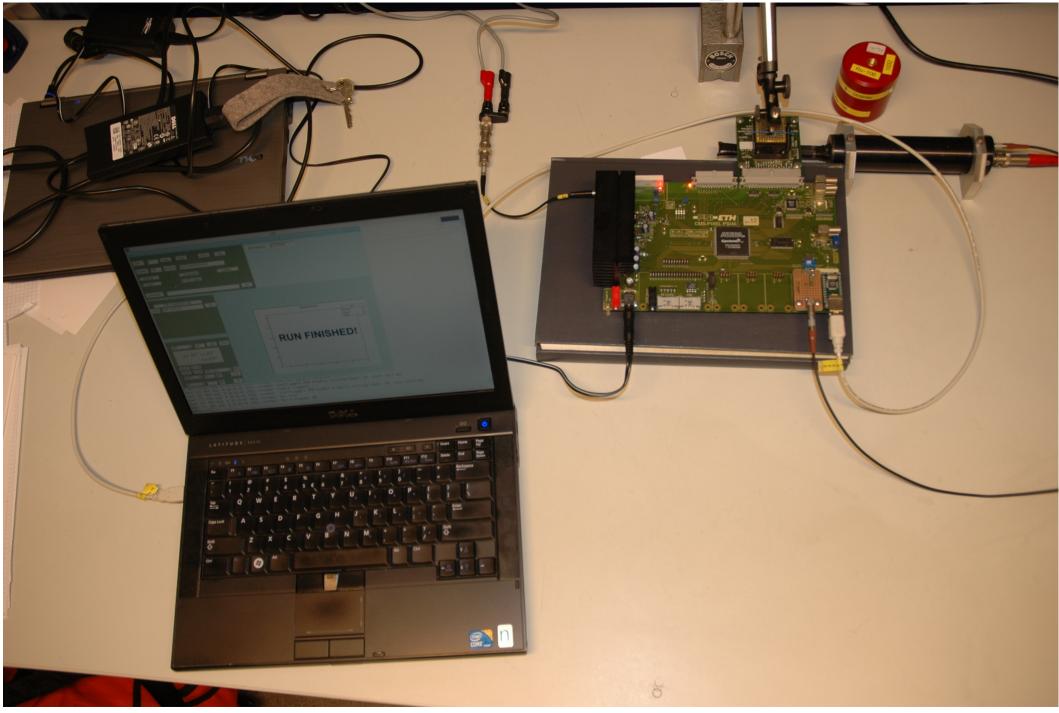

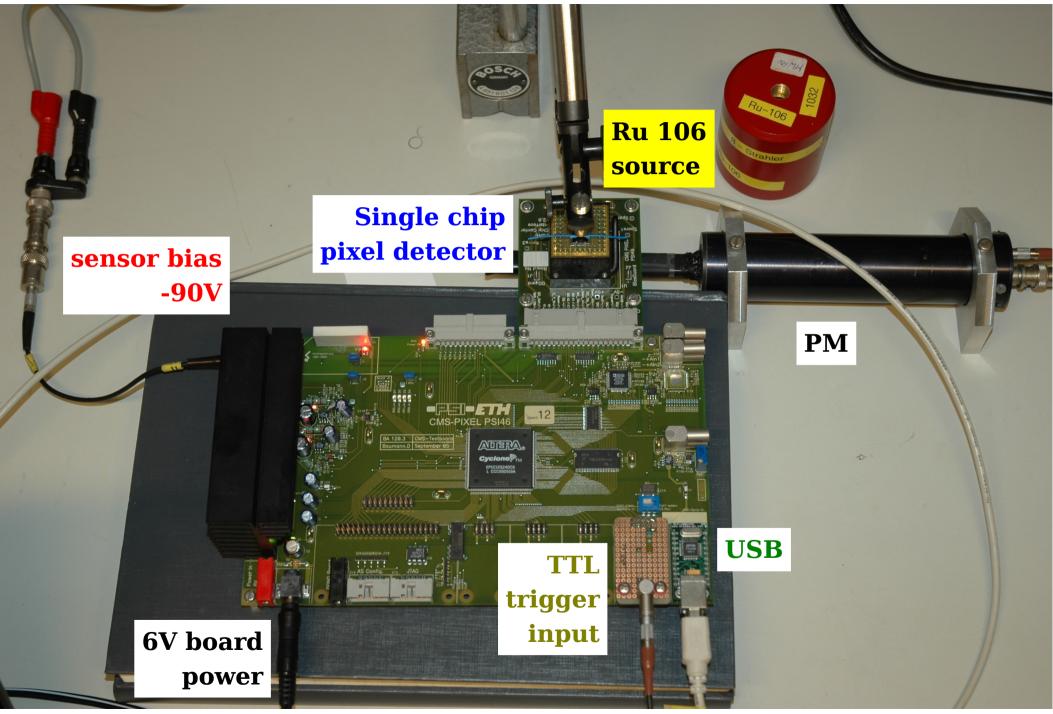

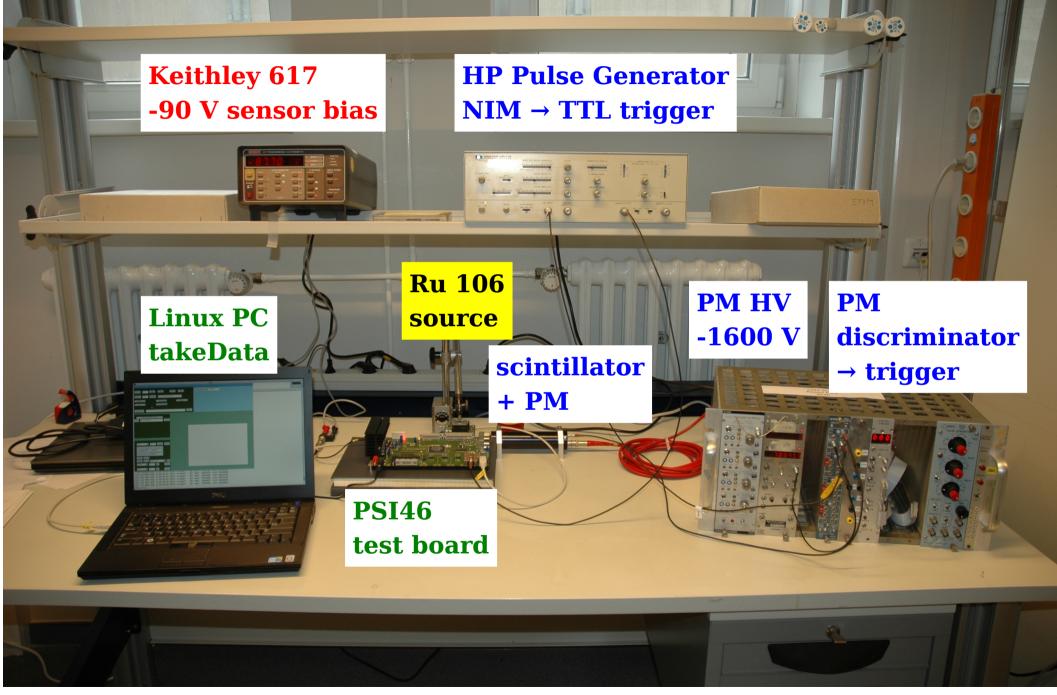

#### **Source test setup**

#### **Source test setup**

## **Cluster analysis code**

- Adapted clustering code from **BinaryFileReader** class (PSI code)

- For each event:

- start from a hit pixel and adjoin neighboring hit pixels into a cluster

- repeat for adjoined pixels, allow gap of one row/column

- determine the weighted center pixel of a cluster

- Added analysis of mean:

- cluster multiplicity

- cluster size

- cluster charge

- "Event display" for clusters

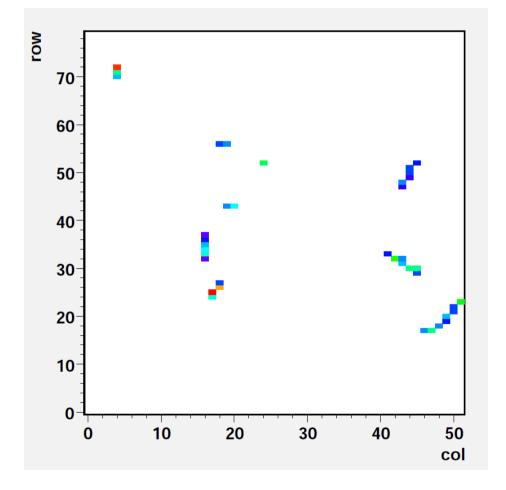

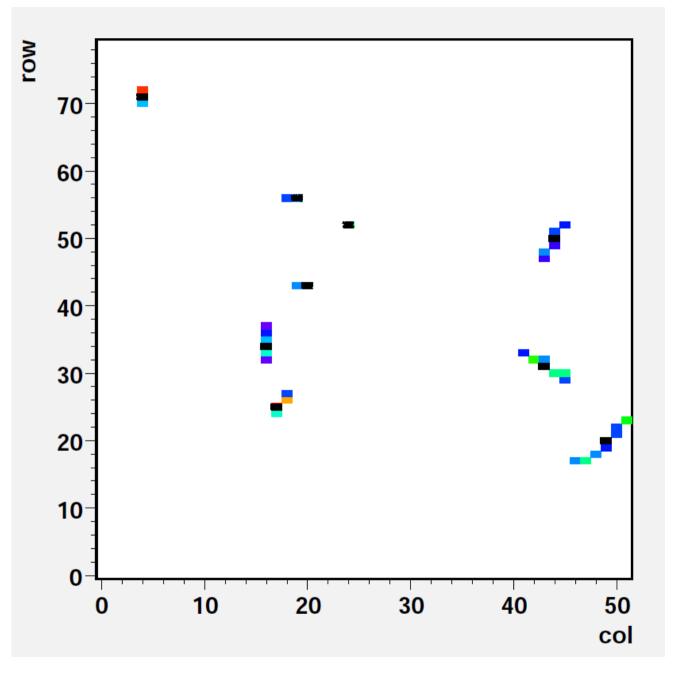

# **Single event display**

- Sample event

- ► Ru 106 source

- Chip 8

- Clock stretch 1 ms

- ► -100 V bias

A. Gajos: Pixel source test - results

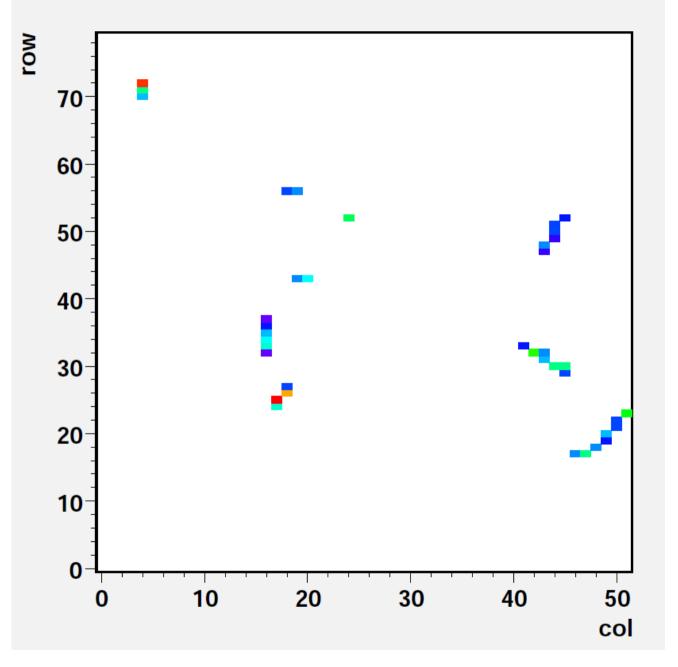

#### **Cluster analysis**

- Sample event

- ► Ru 106 source

- Chip 8

- Clock stretch 1 ms

- ▶ -100 V bias

- 9 clusters identified

- Black pixels indicate centers of clusters

A. Gajos: Pixel source test - results

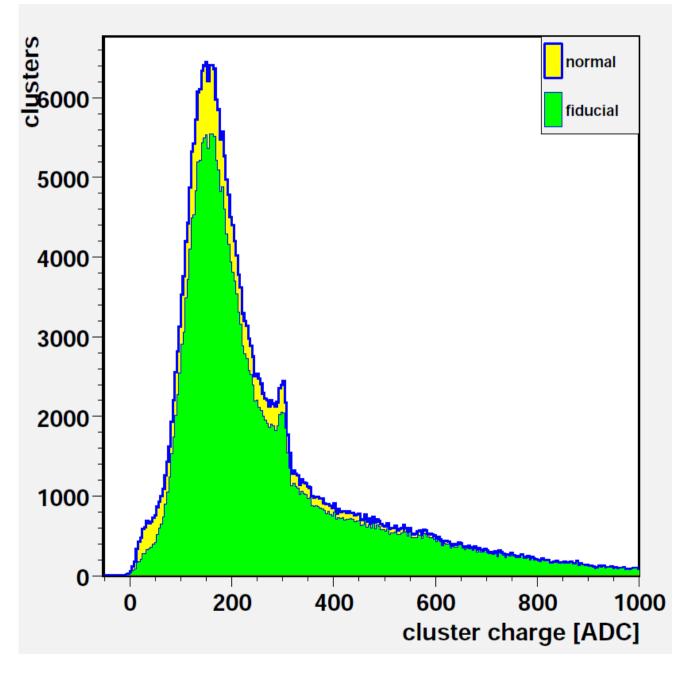

## **Cluster charge distribution**

- Ru 106 source

- All Clusters

- Peak at 300: saturated pixel

- Cluster charge distribution affected by hits at the edges

- Fiducial: cluster center 2 pixels from the edge

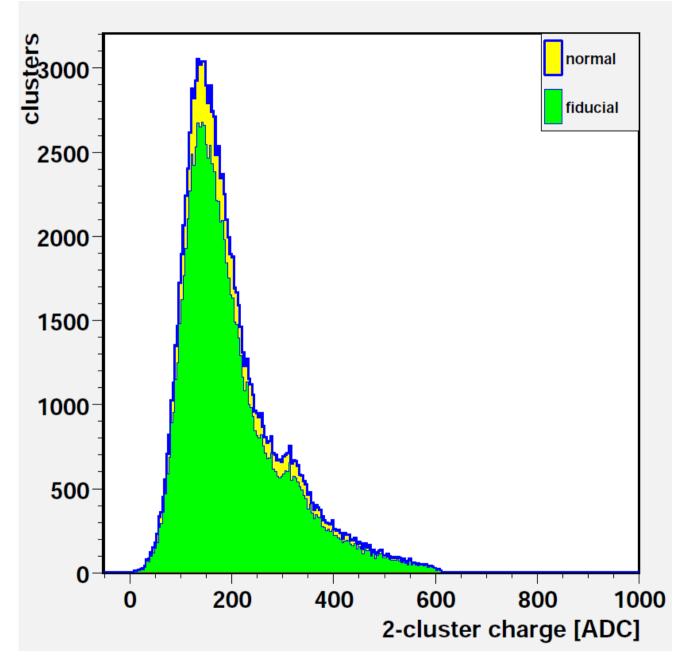

## **Cluster charge distribution**

- Ru 106 source

- 2-pixel clusters

- Reduced peak at 300: saturated pixel

- Cluster charge distribution less affected by hits at the edges

A. Gajos: Pixel source test - results

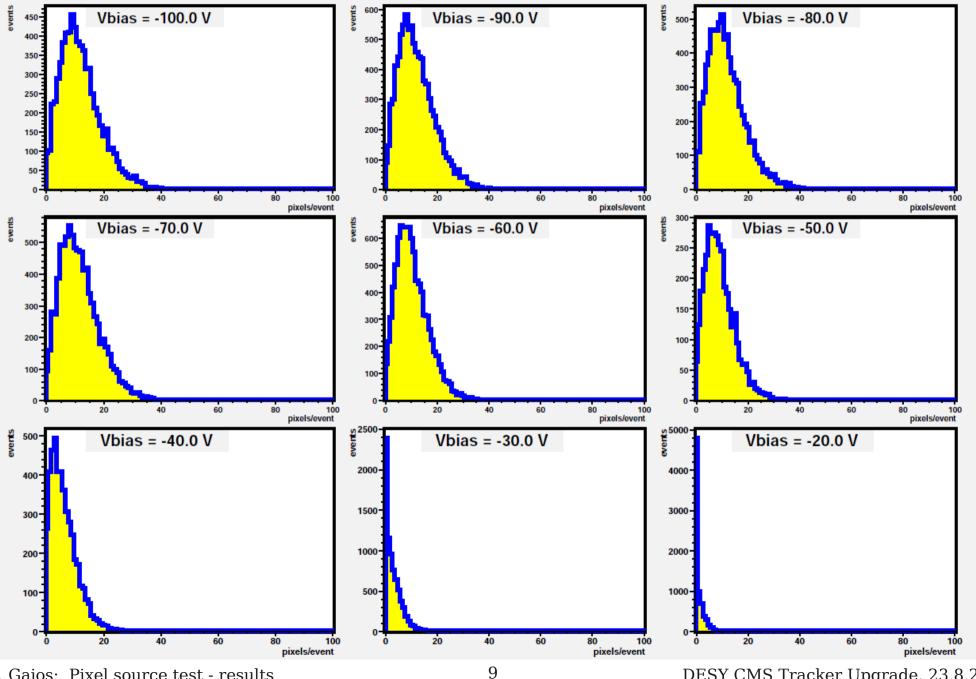

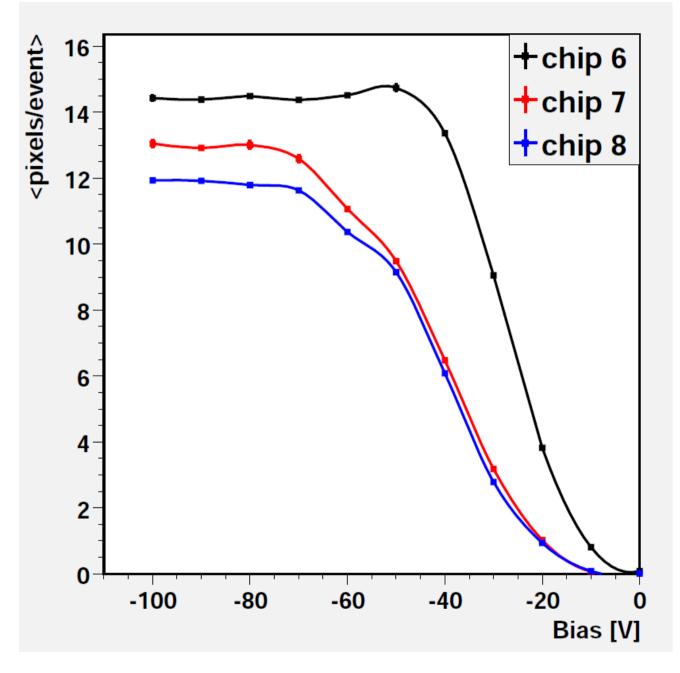

# **Pixel multiplicity vs bias voltage**

A. Gajos: Pixel source test - results

DESY CMS Tracker Upgrade, 23.8.2011

# **Pixel multiplicity vs. bias voltage**

- All scans with:

- Internal trigger

- Clock stretch 1 ms

- 10s run for one Vbias value

- Scans for chips 6, 7, 8

- Thresholds from Alexey Petrukhin

- Full depletion below

-70 V

A. Gajos: Pixel source test - results

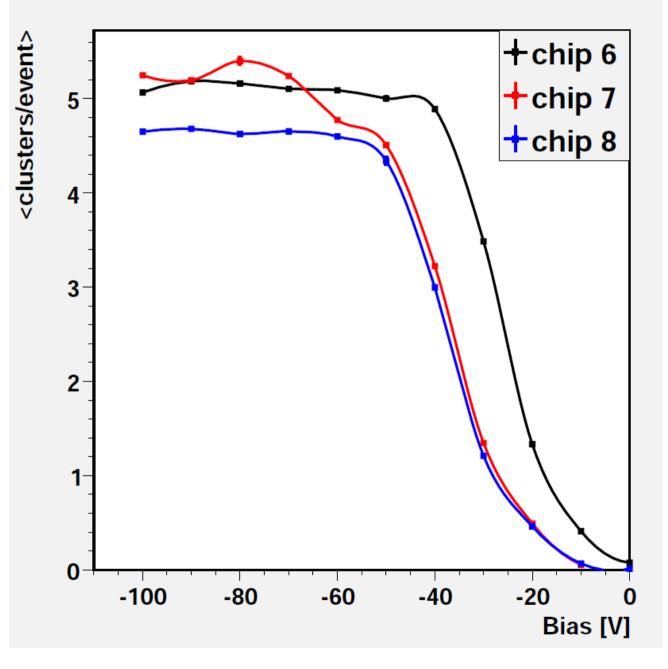

## **Cluster multiplicity vs. bias voltage**

- All scans with:

- Internal trigger

- Clock stretch 1 ms

- 10s run for one Vbias value

- Scans for chips 6, 7, 8

- Thresholds from Alexey Petrukhin

- Cluster efficiency saturates below -50 V

A. Gajos: Pixel source test - results

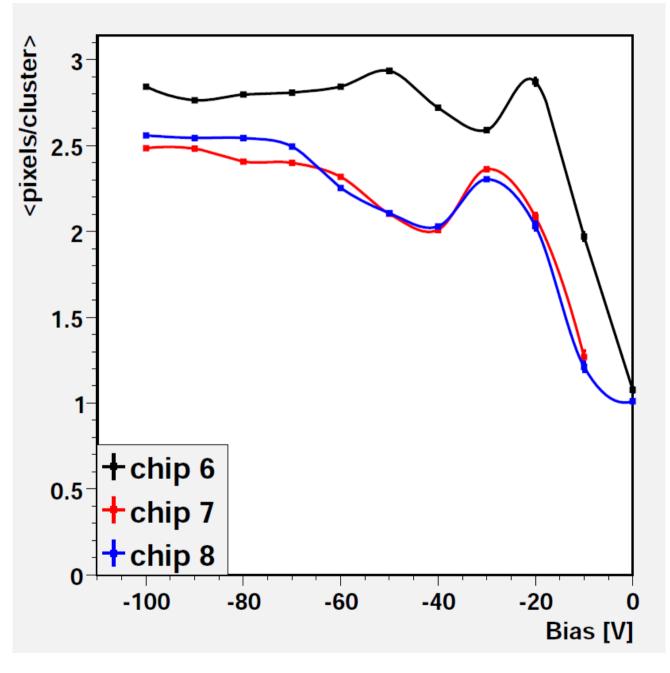

#### **Cluster size vs. bias voltage**

- All scans with:

- Internal trigger

- Clock stretch 1 ms

- 10s run for one Vbias value

- Scans for chips 6, 7, 8

- Thresholds from Alexey Petrukhin

A. Gajos: Pixel source test - results

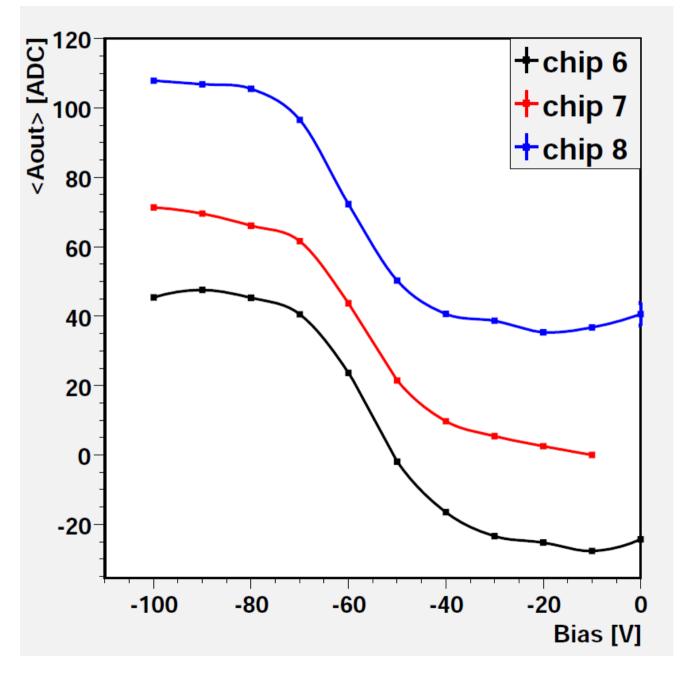

## Pixel charge vs. bias voltage

- All scans with:

- Internal trigger

- Clock stretch 1 ms

- 10s run for one Vbias value

- Scans for chips 6, 7, 8

- Thresholds from Alexey Petrukhin

- Analog gain and offset not equalized

A. Gajos: Pixel source test - results

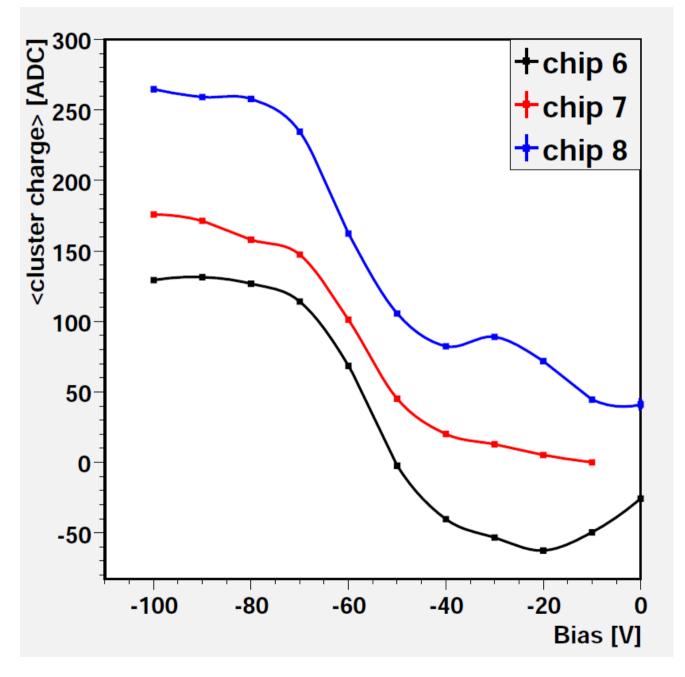

## **Cluster charge vs. bias voltage**

- All scans with:

- Internal trigger

- Clock stretch 1 ms

- 10s run for one Vbias value

- Scans for chips 6, 7, 8

- Thresholds from Alexey Petrukhin

- Analog gain and offset not equalized

A. Gajos: Pixel source test - results

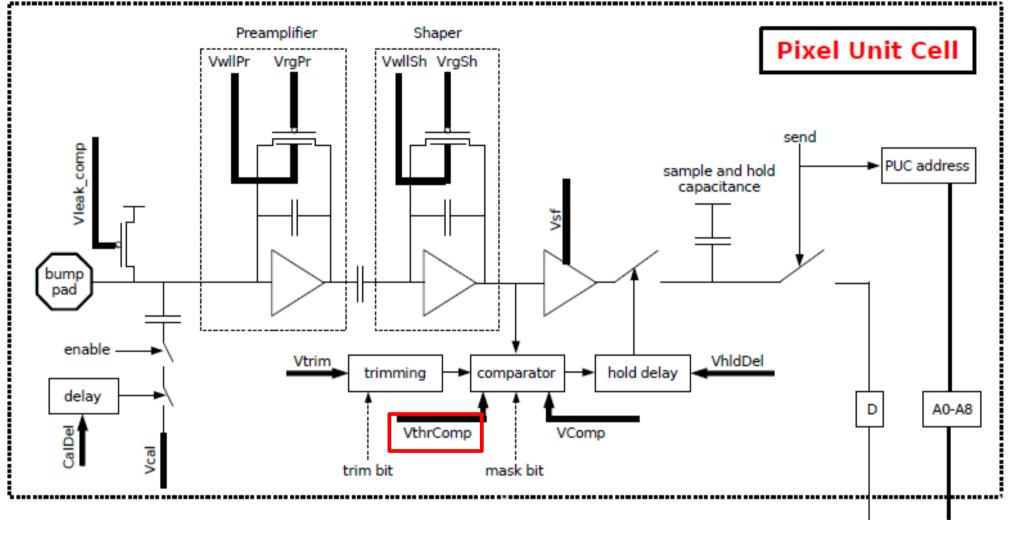

#### **Threshold scan**

- Varied DAC parameter: VthrComp: common threshold

- Values [DAC] range:

- From 30 highest threshold

- No hits recorded for higher thresholds

- To 130 lowest threshold

- Empty readouts for lower thresholds  $\rightarrow$  buffer overflows, internal reset

- Bias voltage fixed at -90 V

- Lowered source position

- ► ~2x rate increase

- Internal trigger

- Clock stretch 0.5 ms to keep same multiplicity. 1.8 kHz trigger

#### psi46 pixel readout chip

adjustable by programmable DAC, per ROC

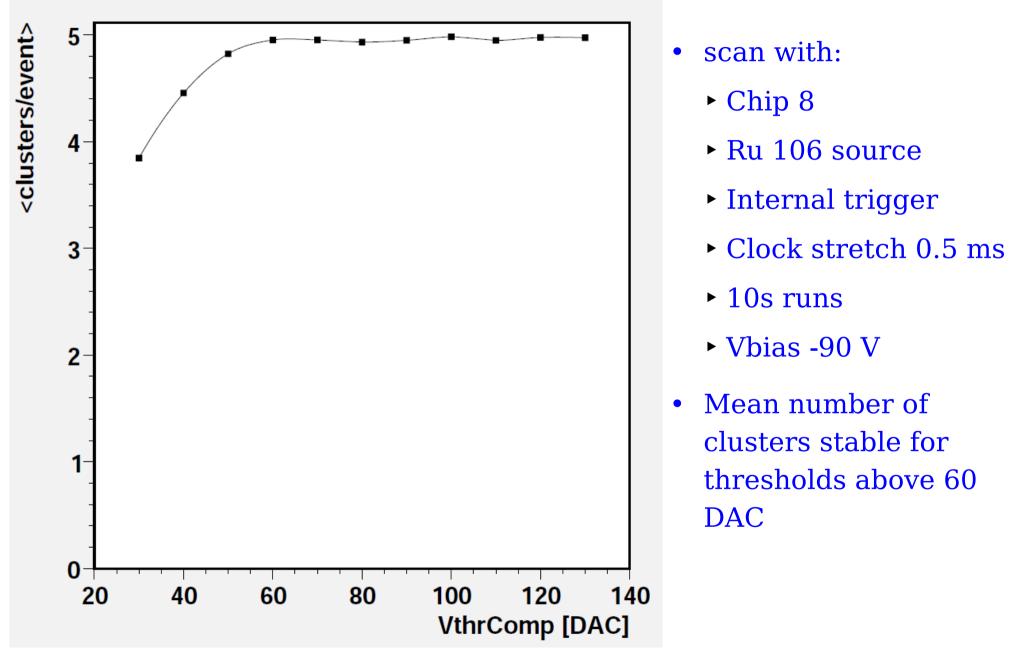

## **Cluster multiplicity vs. threshold**

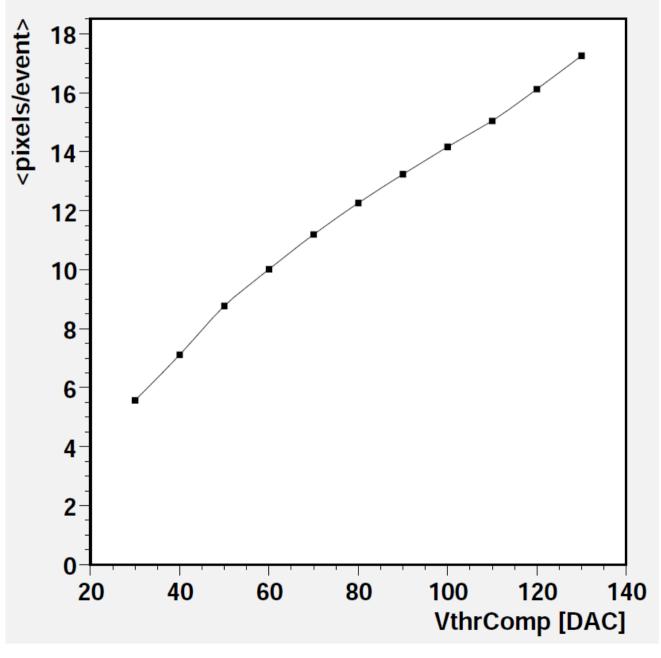

## **Pixel multiplicity vs. threshold**

- scan with:

- Chip 8

- Ru 106 source

- Internal trigger

- Clock stretch 0.5 ms

- 10s runs

- Vbias -90 V

- Pixels in the halo of clusters continue to grow

A. Gajos: Pixel source test - results

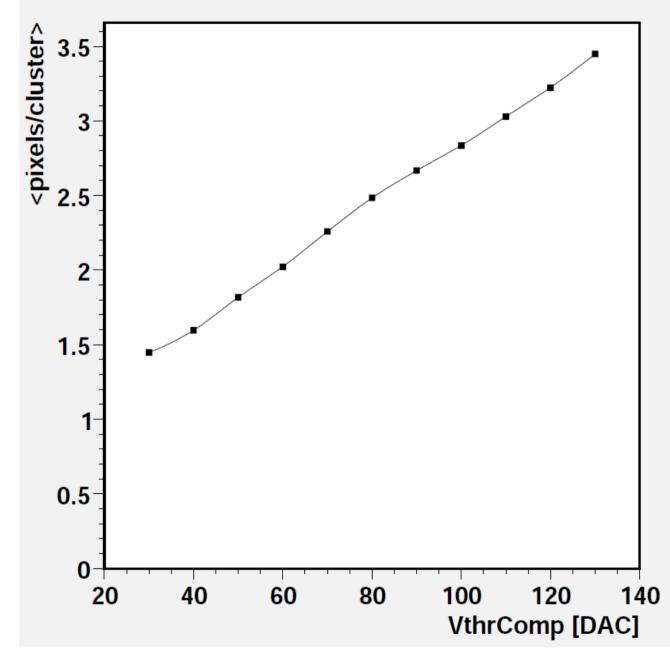

#### **Cluster size vs. threshold**

• Linear growth of clusters with softer threshold

A. Gajos: Pixel source test - results

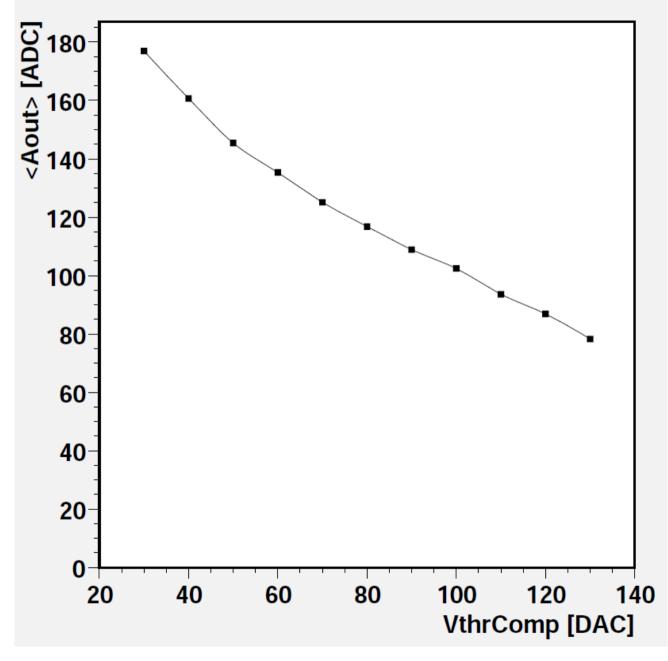

#### **Pixel charge vs. threshold**

• Low amplitude pixels appear with softer threshold

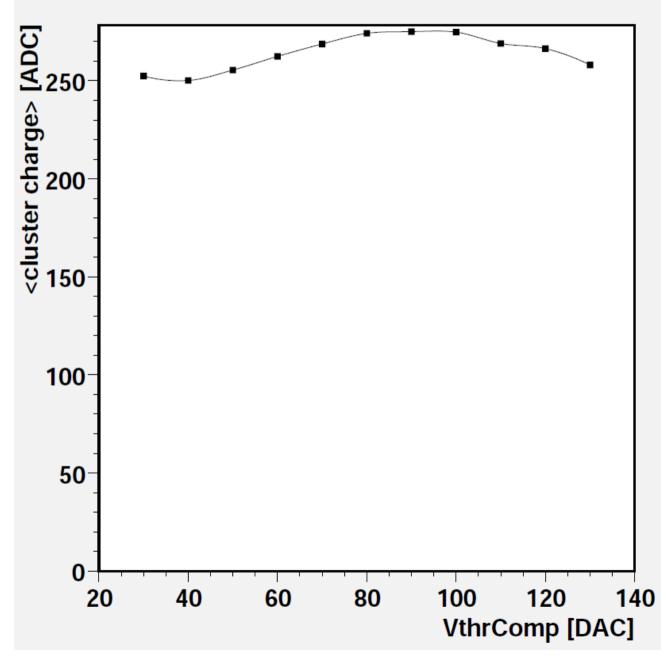

#### **Cluster charge vs. threshold**

- Stronger threshold → clusters lose some pixels

- A small drop at weak threshold?

A. Gajos: Pixel source test - results

## **Status**

- Software for source tests ready

- Chips 6,7 and 8 tested

- Problems with corrupt readouts still present

- They are masked out for analysis

# **Plans for the Testbeam**

- Use external scintillator trigger (E. Garutti)

- 3 GeV positrons, ~ 4 kHz trigger rate measured in TB 21 (I. Gregor)

- H. Maser prepared support frame for the testboard

- Measure pulse height for each pixel

- Uniformity test

- Threshold scan

- Delay scan

- A. Gajos: Pixel source test results

• Uli Koetz (DESY):

# Acknowledgements

- Iab space, NIM crate and modules, scope

- Erika Garutti (DESY and Uni HH):

- finger scintillator and PM.

- Torsten Külper:

- TTL trigger adapter.

- Beat Meier (PSI), Thomas Weiler (KIT), Tilman Rohe (PSI):

- code and advice.

- Carsten Niebuhr (DESY):

- Strahlenschutzunterweisung

- Wladimir Hain (DESY):

- source

- Carsten Muhl (DESY):

- source holder

#### **Source and detector**

- $\operatorname{Ru}^{106} \to \operatorname{Rh}^{106} \to \operatorname{Pd}^{106}$ :

- pure beta emitter,

- E<sub>max</sub> 3.54 MeV,

- half life 1.02 y,

- DESY Ru source #1032 has ~15 kHz activity today (scintillator).

- PSI46 ROC (v 2.4) from 2005 (chip 6)

- bump bonded at PSI to a baby pixel sensor.

## Setup in 1d EG 408

A. Gajos: Pixel source test - results

#### DESY CMS Tracker Upgrade, 23.8.2011

#### Software

- PSI test board with Aug 2010 FPGA firmware (v 6.1)

- Single ROC (no TBM emulator)

- settings for the 28 ROC DACs determined by A. Petrukhin.

- takeData code from PSI under 64 bit Linux:

- Run for up to 300 seconds (memory limit).

- FPGA generates reset clock stretch trigger token sequence at up to 1 kHz.

- Raw data from ROC are stored in 64 MB memory.

- transfer memory via USB (0.44 MB/s), store as binary file.

- Process binary file:

- decode raw data: header, pixel address, pulse height.

- (cluster finding code to be written...).

- fill ROOT histograms.

#### **PSI46 test board trigger modes**

- External trigger:

- used in CMS

- needed for test beam

- source test with penetrating beta rays

- Internal trigger:

- generated on the test board

- needed for X-ray source test

- allows stretching of the clock by up to 2<sup>16</sup> × 25 ns =1.64 ms for increased efficiency

- reached up to 89% duty cycle: 890 Hz with 1 ms clock stretch.

- Timing:

- board trigger delay tct = 103 BC after stretched clock cycle.

- ROC bunch crossing pointer WBC = 100.

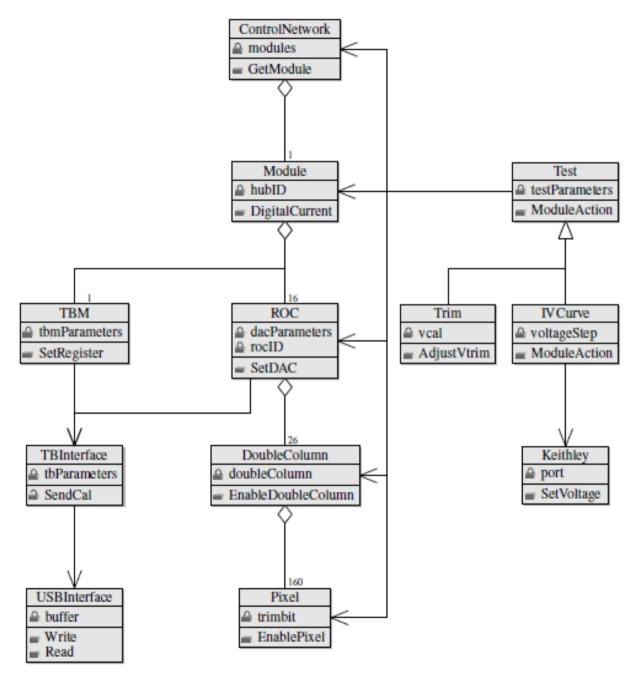

# psi46expert software

- C++ class library.

- Written by Peter Trüb (ETH, 2005-2007) for Scientific Linux (32 bit).

- Now compiled with g++ 4.4.5 under Ubuntu 10.10 (64 bit).

- USB interface required some changes (long → int).

- Lot's of code only a small portion explored so far...