# The OCTOPUS Project: Towards a Vertex Detector for Higgs Factories

Optimized CMOS Technology for Precision in Ultra-thin Silicon

Gianpiero Vignola, on behalf of the OCTOPUS project

11th Annual MT Meeting GSI in Darmstadt, 03 November 2025

### **OCTOPUS Institutes**

#### **International Project within DRD3 Collaboration**

| Member institutes |                      |

|-------------------|----------------------|

| APC Paris         | GSI Darmstadt M T    |

| Universität Bonn  | IPHC Strasbourg      |

| CPPM Marseille    | MBI Vienna           |

| CERN Geneva       | NIKHEF Amsterdam     |

| DESY Hamburg MT   | University of Oxford |

| ETH Zürich        | Universität Zürich   |

| FNSPE CTU Prague  |                      |

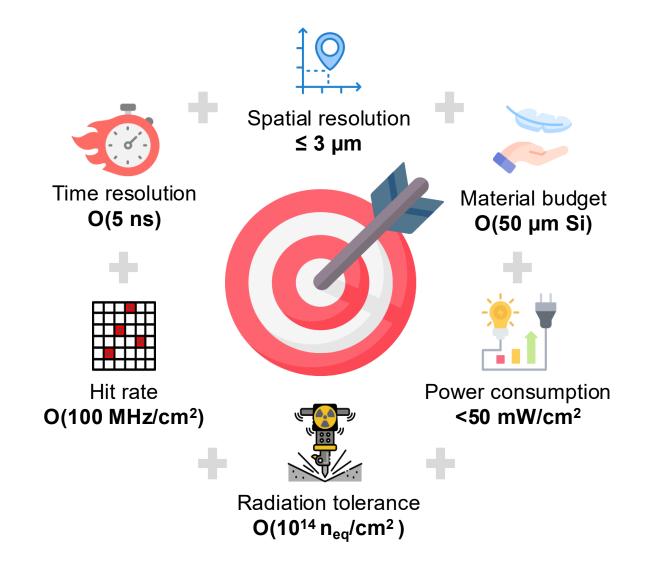

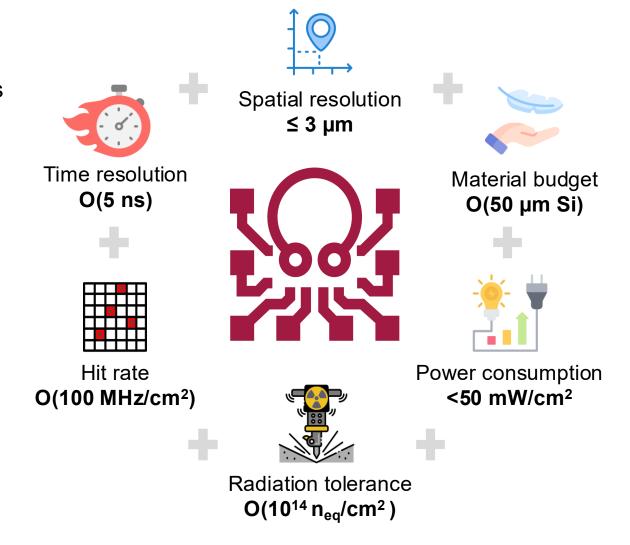

## **OCTOPUS Project: Final Target**

#### **Vertex Sensor Demonstrator**

- Development of a full-size sensor demonstrator for future lepton collider vertex detectors

- Target vertex-detector requirements outlined in the ECFA detector roadmap (in 2021)

- Simulate, develop, and test fine-pitch pixel sensors prototypes

- Exploiting synergies with related R&D activities and other DRD groups (DRD7, DRD8)

- Staged approach: adapting to the upcoming strategy update recommendations

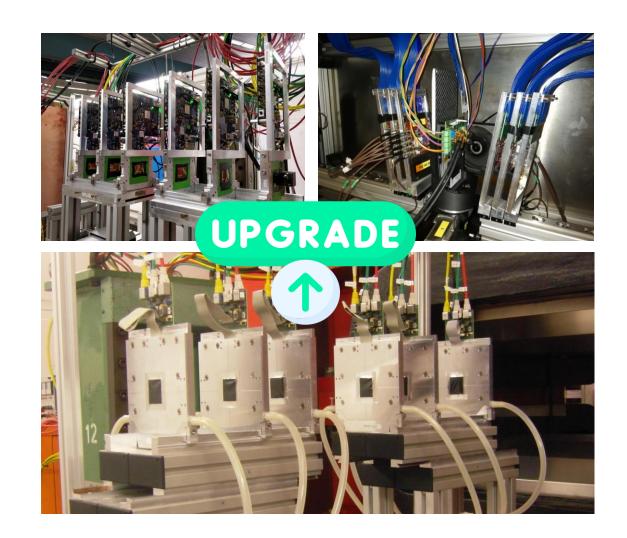

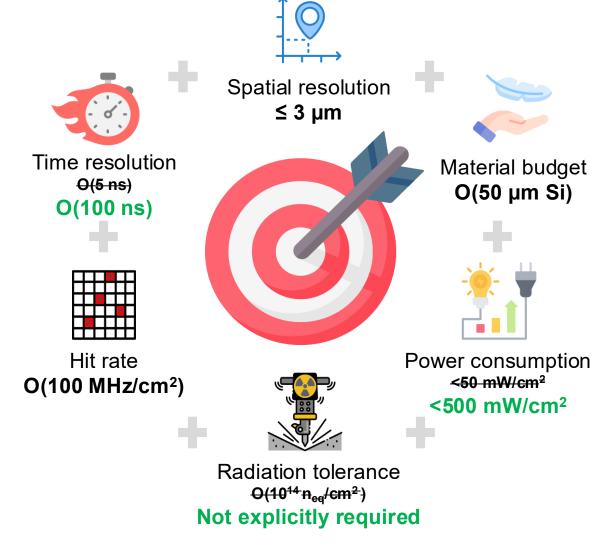

## **OCTOPUS Project: Intermediate Target**

**Development of High Resolution Sensor for Beam Telescopes**

## The Technology

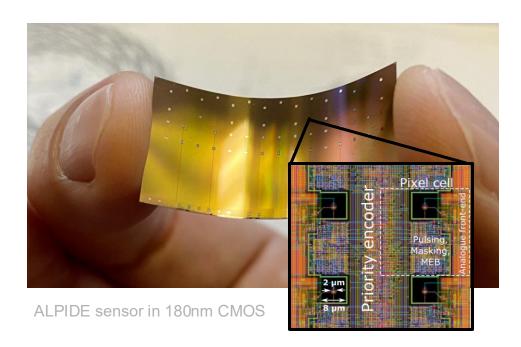

#### **Monolithic Active Pixel Sensors (MAPS)**

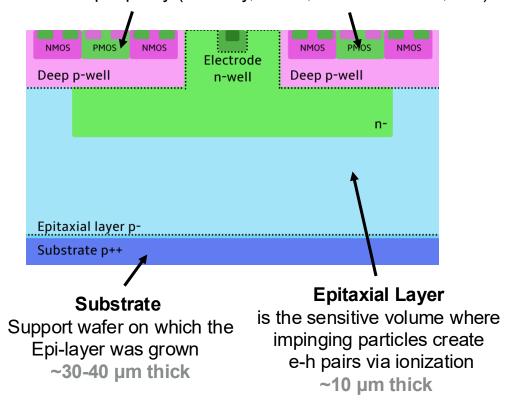

- Small collection electrode MAPS developed using commercial CMOS processes

- Already in use as detectors in HEP experiments

- Several R&D ongoing for the next-gen. MAPS produced using a CMOS 65 nm process

#### **Monolithic Electronics**

CMOS circuits on the same silicon. No additional electronics required. Can be at pixel level (masking, amplification, discriminator, digitization, etc.) or in the sensor periphery (memory, TDCs, data serializers, etc.)

## **Ongoing Activities: Investigation of Previous Works**

**Summary Report on Sensor Produced in TPSCo 65 nm process**

- Summarising results from recent studies on MAPS in TPSCo 65 nm process in the context of project goals

- Is the starting reference for OCTOPUS activities

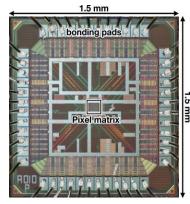

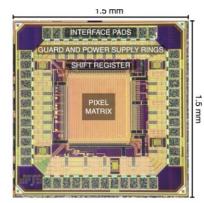

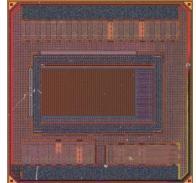

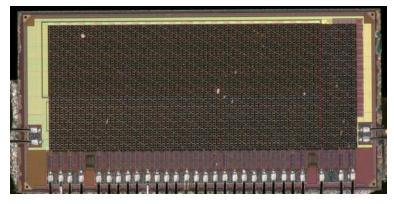

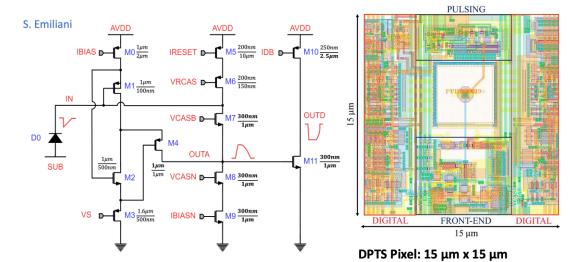

- Investigated prototypes: APTS (SF-OA) [1], [2], [2], [4], DPTS [5], CE-65(V2) [6], H2M [7]

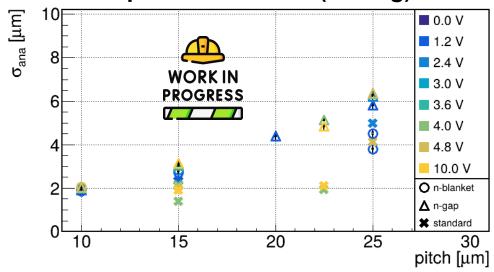

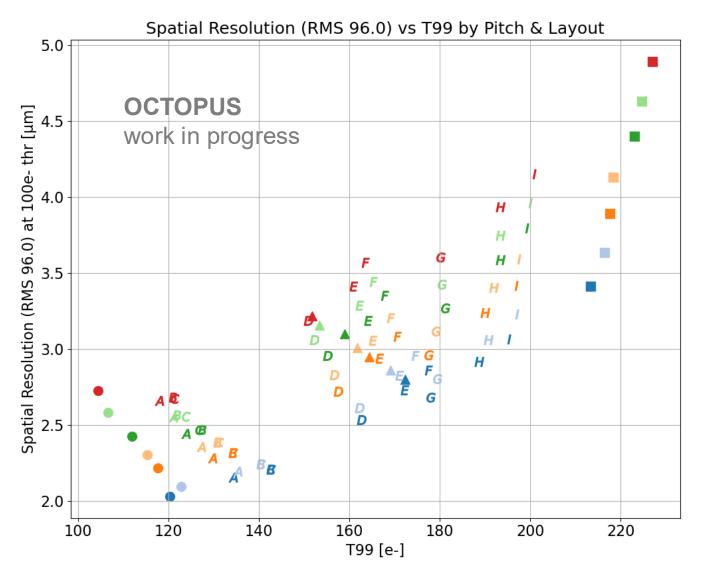

#### **Spatial resolution (analog)**

## **Ongoing Activities: Sensor Design Optimization**

#### **Using a Technology-Independent Simulation Approach**

- Significance emphasis on simulations-based on a technology-independent approach

- Improve sensor layout by combining TCAD and Allpix<sup>2</sup>

- Allows for an efficient and cost-effective development process by reducing the number of production iterations

- Use results from existing TPSCo 65 test chips to benchmark simulations

- Large parameter space of process variants, pitch, ToT resolution

- Trade-off between charge sharing (spatial resolution), efficiency, timing

## **Ongoing Activities: Sensor Design Optimization**

#### **Preliminary Simulations Results**

#### **Sensor Layout Variants** Pitch 15um 16um 17um 18um 19um 20um 21um Layouts Standard layout NGap layout Standard Modified Modified layout **NCross** A=0.5, B=highA=1.0, B=high A=1.5, B=high A=0.5, B=medium A=1.0, B=medium A=1.5, B=medium A=0.5, B=1.0

**NGap**

A=1.0, B=1.0

A=1.5, B=1.0

**NCross**

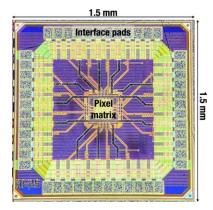

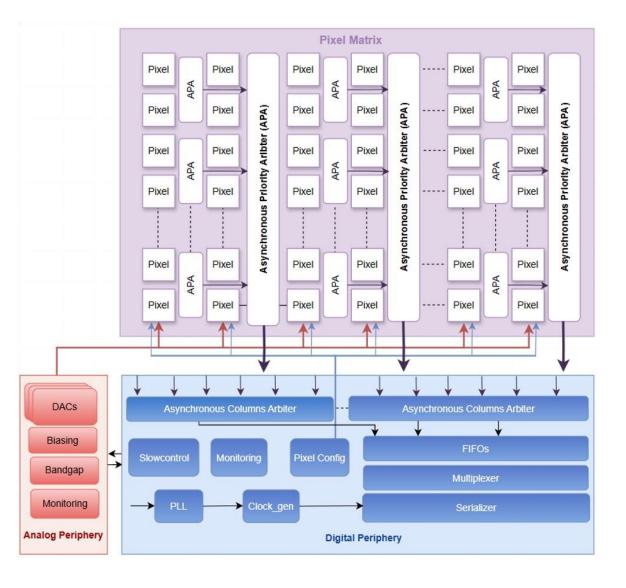

## Ongoing Activities: ASIC Concept and Design

#### In Preparation for First Submission

#### **WOLFI: First Large Scale Prototype concept**

- Aiming for a full column height with flexible width

- Active Matrix with minimal intelligence

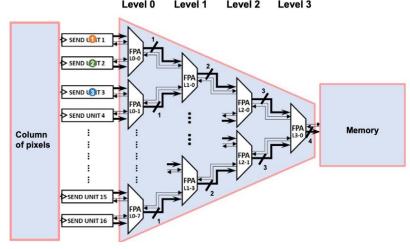

- APA (Asynchronous Priority Arbiter) readout of matrix with pixel grouping

- All biasing from the bottom of the chip

## Ongoing Activities: ASIC Concept and Design

#### In Preparation for First Submission

#### Front end

- FE based on MOSAIX, compact amplifier

- Sample rising and falling edge for offline ToT measurement

- Small footprint required to reach the target spatial resolution

#### Matrix readout: APA - Asynchronous Priority Arbiter

- Compact, low-power solution for high rate readout

- Moderate impact on time resolution, no time stamping clock in matrix

- 65nm proof-of-concept prototype (SPARC) already submitted

#### End of column & serializer

- Time stamping of hits after APA in end of column and buffer

- Focus on bit-efficiency in data transfer, limit TS and address bits

- IpGBT logic as preferred option, 40 to 50 Gbps for the reticle size chip

https://indico.cern.ch/event/1461789/

F.Piro, A Compact Front-End Circuit for a Monolithic Sensor in a 65-nm CMOS Imaging Technology, 09.09.2023, IEEE Transactions on Nuclear Science

APA structure

## **Summary & Outlook**

#### **Towards Lepton Collider Vertex Detector Demonstrator**

- OCTOPUS aims to develop a reticle size MAPS vertex sensor demonstrator for future lepton colliders

- Staged approach, profiting from previous

TPSCo 65 nm work and exploiting synergies

- Particular emphasis on simulations to enable efficient and cost-effective development process

- Exploring innovative options for sensor layout and matrix readout to achieve goals

- First large-scale prototype WOLFI In preaparation

- SPARC prototype to test APA is in production and will be tested by OCTOPUS in the coming months

- Investigations ongoing for first submission in 2026

## Thank you.

Gianpiero Vignola gianpiero.vignola@desy.de

Deutsches Elektronen-Synchrotron DESY Notkestraße 85, 22607 Hamburg 1C, O1.331, ATLAS

## **OCTOPUS Project Structure**

#### Four Workpackages

#### **WP1: Simulations**

- TCAD simulations: sensor optimization

- Allpix<sup>2</sup> simulations: detector performance

- Contribution to Allpix<sup>2</sup> development

- Physics performance and geometry optimization

#### **WP3: Data Acquisition**

- Chipboard design for prototypes & DAQ integration

- Chip/board assembly, bonding & logistics

- Contribution to Caribou development

#### WP2: ASIC

- Pixel front-end and matrix architecture design

- Periphery, DACs & slow control design

- Transceivers and readout design

- Chip integration and verifications

- Submission coordination & interface with DRD7

#### **WP4: Testing & Characterization**

- Summary of current TPSCo65 demonstrator results

- Lab characterization, FE optimization, calibration

- Testbeam characterization, performance