# First Major Release of fwk

14th MicroTCA Workshop

Çağıl Gümüş

Hamburg, 03.12.2025

HELMHOLTZ

# What is fwk?

# What is fwk?

- It is an **open-source, FPGA Framework**. Written in Tcl-language (>11k lines)

- Automates the creation and build processes of EDA Tools

- Divides the codebase into smaller chunks of IPs **Modules**

# Supported Tools

ModelSim

# How is fwk related to MicroTCA?

# MicroTCA and fwk are abstractions at a different level

**$\mu$ TCA®**

**Hardware Abstraction**

**FWK**

FPGa Firmware framework

**Firmware Abstraction**

# Where is fwk used?

# fwk is used in:

sckcen

struck innovative

systeme

**HZB** Helmholtz

Zentrum Berlin

**ICEYE**

JOHANNES GUTENBERG

UNIVERSITÄT MAINZ

**UH**

Universität Hamburg

DER FORSCHUNG | DER LEHRE | DER BILDUNG

**HZDR**

HELMHOLTZ ZENTRUM

DRESDEN ROSSENDORF

**TARLA**

Turkish Accelerator & Radiation Laboratory

# How does fwk work?

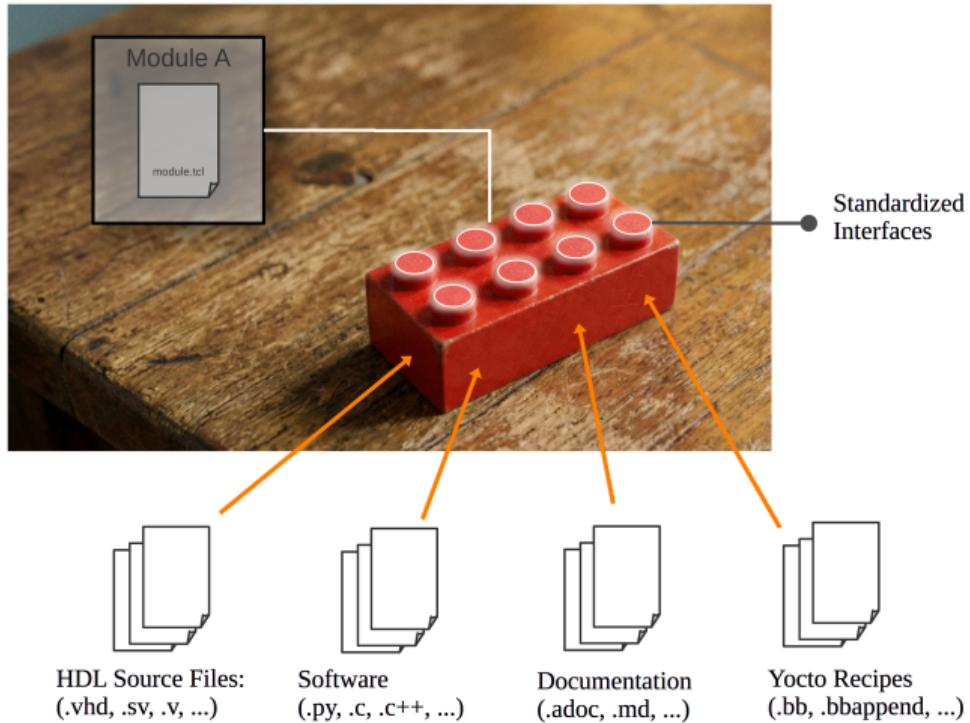

# Module

Generated by Gemini 3

**Module** is a container for an IP. It is the building block of fwk.

# Module

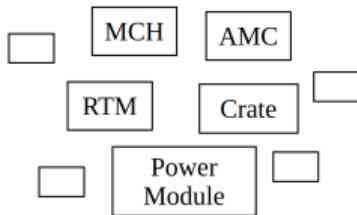

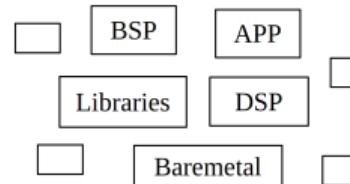

# Types of Modules

Generated by Gemini 3

There are many types of modules: BSP, RTM, FMC, APP, etc.

# Modules using Modules

Generated by Gemini 3

Modules can encapsulate other modules.

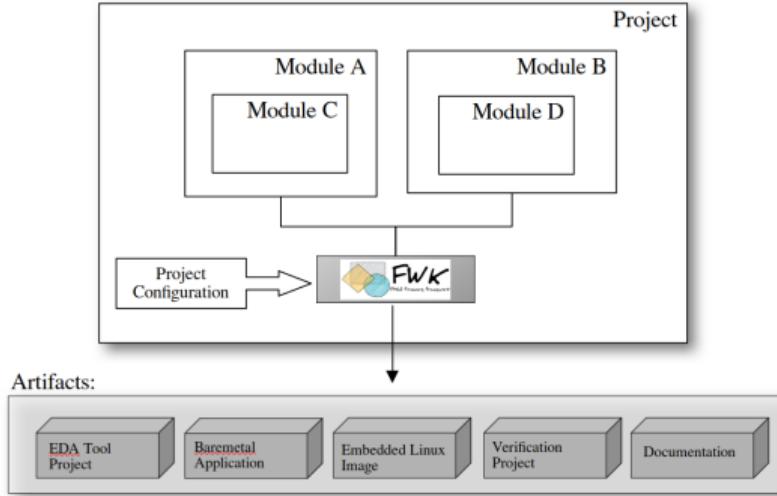

# Assembled Project

Generated by Gemini 3

Final assembled project.

# Open Source Modules and Projects

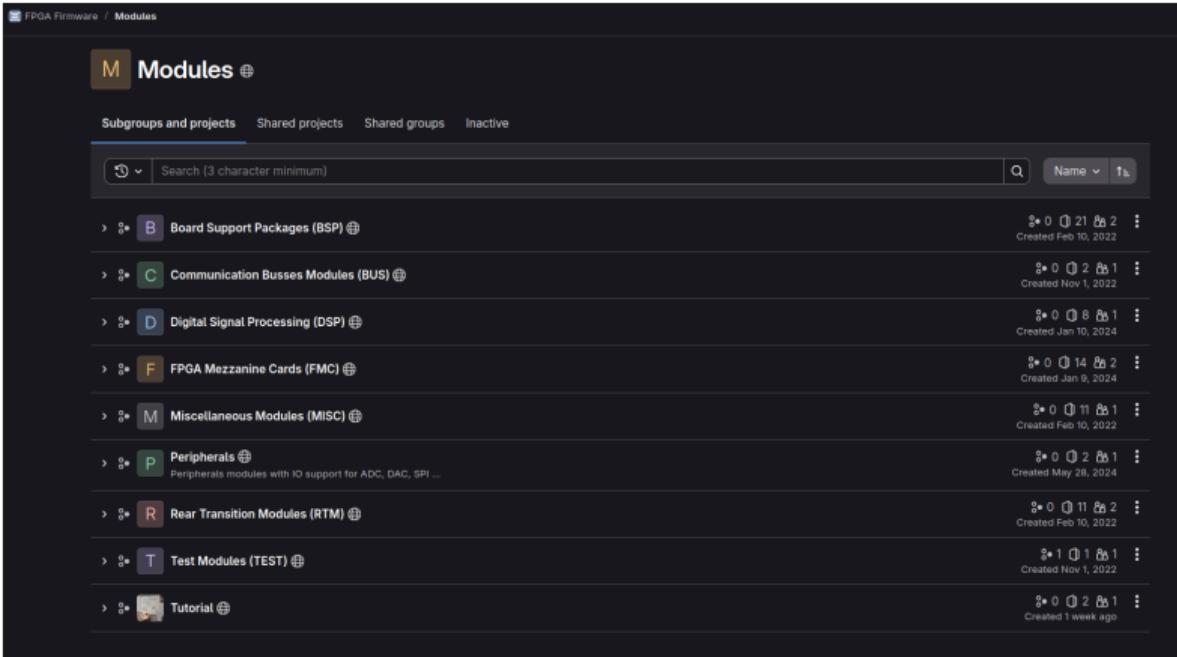

The screenshot shows a dark-themed web interface for managing modules. At the top, there is a navigation bar with a 'FPGA Firmware' icon and the text 'FPGA Firmware / Modules'. Below the navigation bar, there is a search bar with a placeholder 'Search (3 character minimum)' and a dropdown menu. The main content area is titled 'Modules' and contains a list of subgroups and projects. The list includes:

- Board Support Packages (BSP) (21 issues, 2 pull requests, created Feb 10, 2022)

- Communication Busses Modules (BUS) (2 issues, 1 pull request, created Nov 1, 2022)

- Digital Signal Processing (DSP) (8 issues, 1 pull request, created Jan 10, 2024)

- FPGA Mezzanine Cards (FMC) (14 issues, 2 pull requests, created Jan 9, 2024)

- Miscellaneous Modules (MISC) (11 issues, 1 pull request, created Feb 10, 2022)

- Peripherals (2 issues, 1 pull request, created May 28, 2024)

- Rear Transition Modules (RTM) (11 issues, 2 pull requests, created Feb 10, 2022)

- Test Modules (TEST) (1 issue, 1 pull request, created Nov 1, 2022)

- Tutorial (2 issues, 1 pull request, created 1 week ago)

Each item in the list has a small icon next to the subgroup name and a three-dot menu icon on the right.

Visit our Gitlab Page to see all DESY-Modules

# fwk on Evaluation Boards

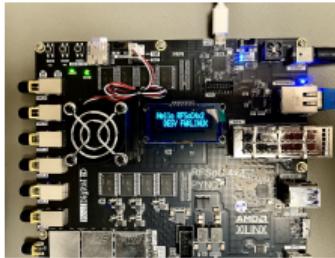

- fwk can support various evaluation boards from AMD. Available:

- ZCU208, ZCU102, RFSoC4x2

- Universidad Politécnica de Madrid has created an fwk example design for Kria260!

- GitHub Link: I2A2 Instrumentation R&D Group

# Future

# Milestones & Future

## Milestone 1.0.0 Reached:

- › Complete overhaul of the Tcl API

- › Documentation written from scratch (w/ the help of LLMs)

- › Evolved into a community project with >20 contributors.

- › External Facilities and Companies started to join the cause!

## Outlook:

- › MSK Group of DESY will continue maintain and develop for many years to come.

- › 2.0.0 Planning has already started...

# fwk Documentation and Tutorials

**FPGA Firmware Documentation (Public)**

fwk Documentation

What is an fwk Project?

What is an fwk Module?

Configuration Mechanism

How fwk works under the hood?

Command Reference (tclake)

Tcl API Reference

Address Space

VHDL Library Management

Supported EDA Tools

Test and Verification of a Module

Module Documentation Guide

Template Engine Usage

> TUTORIALS

CHANGELOG

License and Copyrights

Contributions and Development Guide

## fwk Tcl API Reference

### Main Process Procedures

These procedures control the high-level execution flow of the framework.

```

proc ::fwk::createProject {}

```

Creates the vendor tool project. This proc executes the following flow:

- Creates the project build directory (`PrjBuildPath`).

- Calls `fwk::tool::cleanProject` to remove old project files.

- Packages any modules defined in the `::fwk::ip` namespace (if it exists).

4. Calls `fwk::tool::createProject` to create the empty tool project.

5. Calls `fwk::doCreate` (runs `doCreate` hook in all modules).

6. Calls `fwk::protoTemplatesRec` (processes all templates).

7. Calls `fwk::addr::main` (generates address space files).

8. Calls `fwk::addSourcesAfter` (runs `addSources` hook in all modules, which in turn calls `fwk::tool::addSources`).

9. Calls `fwk::doPostCreate` (runs `doPostCreate` hook in all modules).

10. Calls `fwk::tool::saveProject` and `fwk::tool::closeProject` (if not in GUI mode).

```

proc ::fwk::buildProject {}

```

Builds the project using the vendor tool:

1. Calls `fwk::tool::openProject`.

2. Creates the `out` directory.

3. Calls `fwk::addr::main` to regenerate address spaces (ensuring they are up-to-date).

4. Calls `fwk::doOnBuild` (runs `doOnBuild` hook in all modules).

5. Calls `fwk::tool::buildProject` (runs the tool's main synthesis/implementation).

6. Calls `fwk::tool::exportOut` (copies artifacts to the `out` directory).

**FPGA Firmware Documentation (Public)**

fwk Documentation

Home Page

Installation

What is an fwk Project?

What is an fwk Module?

Configuration Mechanism

How fwk works under the hood?

Command Reference (takake)

Tcl API Reference

Address Space

VHDL Library Management

Supported EDA Tools

Test and Verification of a Module

Module Documentation Guide

Template Engine Usage

> TUTORIALS

Basic Tutorial

Address Space Tutorial

Test and Verification Tutorial using CocoTB

Vitis Tutorial using fwk

CHANGELOG

License and Copyrights

Contributions and Development Guide

## Address Space Tutorial

Modules can instantiate sub-modules while mapping the address space of these instances into their own. This tutorial demonstrates how to achieve this hierarchical address mapping using DesyRDL within fwk projects.

Before starting this tutorial, it is recommended to review the [Main Documentation of DesyRDL](#).

In short, DesyRDL generates the compiled address map along with synthesizable HDL files that handle address decoding. This offers a significantly better approach to creating registers, as users only need to define them using an industry-standard language (SystemVerilog). fwk ensures that the files generated by DesyRDL are added to the project correctly (e.g., ensuring libraries are set correctly).

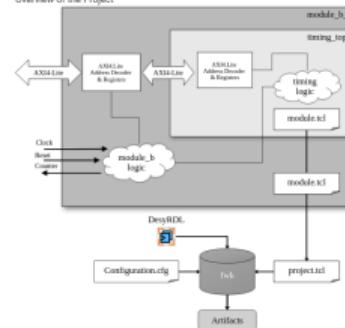

### Overview of the Project

The diagram illustrates the project structure for the Address Space Tutorial. It shows a top-level module `module_b_top` containing `Timing_top` and `module_b`. `Timing_top` contains `Timing logic` and `module_a`. `module_a` contains `module_a logic`. `module_b` contains `module_b logic`. A `Clock` signal is connected to `module_a logic` and `module_b logic`. A `Reset` signal is connected to `module_a logic`. A `Config` signal is connected to `Timing_top`. A `DesyRDL` block is connected to `Timing_top`. A `Configuration.cfg` file is connected to `DesyRDL`. The `DesyRDL` block is connected to a `fwk` block, which is connected to a `project` block. The `project` block is connected to `Artifacts`.

`[fig-tutorial-adress-space]` shows how the entire workspace looks like from the top view.

In this tutorial, we will use a module named `module_b`, which contains a dependent module named `Timing`. The `Timing` module originates from DESY and is actively used across many projects. For more information, please refer to the [DESY Documentation](#).

Check out the brand new documentation and tutorials for 1.0 release!

# Thank you!

## Contact

Deutsches Elektronen-

Synchrotron DESY

[www.desy.de](http://www.desy.de)

Çağıl Gümüş

0000-0003-2176-0212

MSK

[cagil.guemues@desy.de](mailto:cagil.guemues@desy.de)

+49-40-8998-3760

<https://cagil-gumus.github.io/>