#### Jaroslaw Szewinski<sup>1</sup>, Bin Yang<sup>2</sup>

<sup>1</sup>National Center of Nuclear Research <sup>2</sup>Deutsches Elektronen-Synchrotron

16.12.2011

J.Szewinski, B.Yang (NCBJ, DESY)

TMCB Firmware

### The Board

### **Board features**

- 1x Spartan-6 FPGA (XC6SLX45T-2FGG484C)

- 8x Analog input, 1 MSPS, 16 bit (2x AD7655 ADC)

- 4x Analog input, 128 kSPS, 24 bit (4x AD7767 ADC)

- 2x Analog output, 1 MSPS, 18 bit, (2x AD5781 DAC)

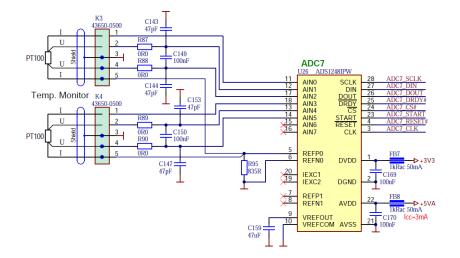

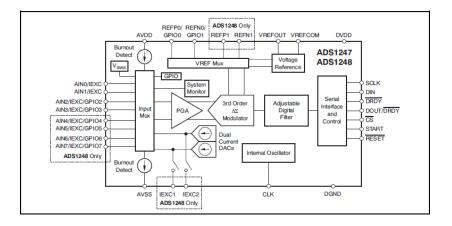

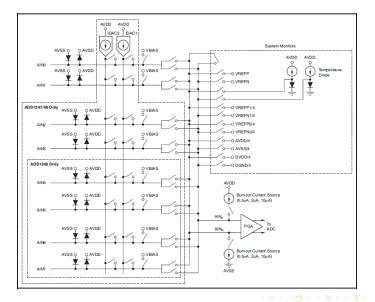

- 4x Temp sensor (2x ADS1248)

- 2x Peltier (1x DAC8552 DAC, 2x LTC2365 ADC)

- GPIO (20x IO)

- Ethernet (1x DP83848C, RMII mode)

- RocketIO fiber interface (1x SFP)

- 13x LVDS pairs

- 2x I2C channels

- 8x LED

#### Implementation status

- 1x Spartan-6 FPGA (XC6SLX45T-2FGG484C)

- 8x Analog input, 1 MSPS, 16 bit (2x AD7655 ADC)

- 4x Analog input, 128 kSPS, 24 bit (4x AD7767 ADC)

- 2x Analog output, 1 MSPS, 18 bit, (2x AD5781 DAC)

- 4x Temp sensor (2x ADS1248)

- 2x Peltier (1x DAC8552 DAC, 2x LTC2365 ADC)

- GPIO (20x IO)

- Ethernet (1x DP83848C, RMII mode)

- RocketIO fiber interface (1x SFP)

- 13x LVDS pairs

- 2x I2C channels

- 8x LED

## MicroBlaze based embedded system for the Ethernet

| 📀 Xilinx Platform Studio (EDK_0.61                                                                                                                                                                                                                                                    | lxd) - D:\users\jszewins | \tmcb\Firmware\tmcb.xmp ·                  | [System Assembly View] | - 🗆 🗵      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------|------------------------|------------|

| 🔶 Eile Edit View Project Hardwa                                                                                                                                                                                                                                                       | re Device Configuration  | Debug ≦imulation <u>W</u> indow <u>H</u> e | lp                     | _ 8 ×      |

|                                                                                                                                                                                                                                                                                       |                          |                                            |                        |            |

| Project ↔ □ 륜 ×                                                                                                                                                                                                                                                                       | ALL                      | Bus Interfaces Ports                       | Addresses              | <u>_</u>   |

| Platform                                                                                                                                                                                                                                                                              | XMM                      | Name                                       | Bus IP Type            | IP Version |

| Project Files MHS File: tmcb.mhs UGF File: data(tmcb.ucf MHS File: that(tmcb.ucf MPACT Command File: etc/dot Implementation Options File: etc/bitgen El: Files Project Options Oevice: xc6s(x45tfgg484-2 Netiks: TopLevel Implementation: x95 (xflow) HDL: VHOL Sim Model: BEHAVIGRAL |                          | axi4lite_0                                 | 👷 axi_interconnect     | 1.03.a     |

|                                                                                                                                                                                                                                                                                       |                          | microblaze_0_dlmb                          | 🙀 lmb_v10              | 2.00.b     |

|                                                                                                                                                                                                                                                                                       |                          | microblaze_0_ilmb                          | 🙀 lmb_v10              | 2.00.b     |

|                                                                                                                                                                                                                                                                                       |                          | ⊕- microblaze_0                            | 🙀 microblaze           | 8.20.a     |

|                                                                                                                                                                                                                                                                                       |                          | microblaze_0_bram_block                    | ☆ bram_block           | 1.00.a     |

|                                                                                                                                                                                                                                                                                       |                          | microblaze_0_d_bram_ctrl                   | 👷 lmb_bram_if_cntlr    | 3.00.b     |

|                                                                                                                                                                                                                                                                                       |                          | microblaze_0_i_bram_ctrl                   | 👷 lmb_bram_if_cntlr    | 3.00.b     |

|                                                                                                                                                                                                                                                                                       |                          | 🗈 debug_module                             | 👷 mdm                  | 2.00.b     |

|                                                                                                                                                                                                                                                                                       |                          | microblaze_0_intc                          | 📩 axi_intc             | 1.01.a     |

|                                                                                                                                                                                                                                                                                       |                          | ⊕ eth_0                                    | 🔫 axi_ethernetlite     | 1.00.a     |

|                                                                                                                                                                                                                                                                                       |                          | clock_generator_0                          | 👷 clock_generator      | 4.02.a     |

|                                                                                                                                                                                                                                                                                       |                          | mii_to_rmii_0                              | ☆ mii_to_rmii          | 1.01.a     |

| Design Summary                                                                                                                                                                                                                                                                        |                          | proc_sys_reset_0                           | 👷 proc_sys_reset       | 3.00.a     |

|                                                                                                                                                                                                                                                                                       |                          |                                            |                        |            |

| Legend<br>Master ⇒Slave ⊯Master/Slave ⊨Target (Initiator ©Connected OUnconnected M Monitor<br>☆ Production @License (paid) @License (eval) ℃Local ≚Pre Production 腔Beta 黑Developr<br>& Superseded ℃Discontinued<br>◆ Project ◆ IP Catalog System Assembly View<br>↓                   |                          |                                            |                        |            |

- Standard LwIP stack could not be used because it needs at least 1MB of RAM - so new one has been created

- New stack supports minimal set of features needed to handle UDP protocol

- Memory is needed for TCP, to reconstruct big data blocks from fragmented packets (long buffer is needed)

- UDP transfers single packets, without taking care of data loss and packet order

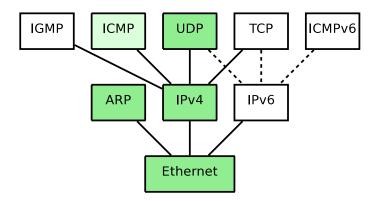

## Implemented parts of TCP/IP protocol family

Protocol Stack:

- Support for Ethernet frames

- Support for the ARP protocol

- Support for the IPv4 protocol without fragmentation and extended options (frame up to 1500 bytes)

- Support for the ICMP protocol only response to echo request (ping)

- Support for the UDP protocol

- All code runs in 64kB of ram (probably less would be also fine)

- About 500 lines of C code

Software:

- MEX files for communication from Matlab are ready

- Dedicated DOOCS servers will be made for particular applications

#### 2 Ethernet

#### 4 Summary

- RF switches (GPIO) ready

- Digital Controlled Attenuators (GPIO) ready

- Temperature controller under development

- PID controller will be ported from ACB2.1

- Peltier (TEC) to be done

- Amplitude RF detector, readout from 24-bit ADC ready

- Operation modes (continues, switching) under development

- Ethernet communication has used to set parameters ready

## Firmware for Fiber Link Optical Synchronization

- Analog monitoring (slow and fast ADCs) ready

- Controller (ADC → IIR → PID → DAC feedback) under development

- Fast ADC readout ready

- DAC support ready

- PID controller will be ported from ACB2.1

- Low-pass filter (2<sup>nd</sup> order IIR) will be ported from ACB2.1

- Temperature monitoring under development

- Temperature control with Peltier element to be done

- Microwire protocol, for attenuators and phase shifters to be done

- SFP fiber link interface under development

- DOOCS server to be done

- C code for Ethernet communication with TMCB ready

## Difficulties

Ethernet - No RAM memory on board caused the need for writing own TCP/IP stack implementation

- Ethernet No RAM memory on board caused the need for writing own TCP/IP stack implementation

- DAC Board no #2 had some problems with one of the DACs

- Ethernet No RAM memory on board caused the need for writing own TCP/IP stack implementation

- DAC Board no #2 had some problems with one of the DACs

- SFP interface RocketIO is clock sensitive, and clock generated by I<sup>2</sup>C programmable clock generator Si570. So, first the generated clock frequency has to be confirmed that it is correct (RocketIO expects precise frequency), and then debugging has to go down to debug core inside FPGA.

- Ethernet No RAM memory on board caused the need for writing own TCP/IP stack implementation

- DAC Board no #2 had some problems with one of the DACs

- SFP interface RocketIO is clock sensitive, and clock generated by I<sup>2</sup>C programmable clock generator Si570. So, first the generated clock frequency has to be confirmed that it is correct (RocketIO expects precise frequency), and then debugging has to go down to debug core inside FPGA.

#### Temperature sensors

- The sensor is self (PT100) had to be obtained first (took some time)

- The ADC for temperature monitoring is complex, and has to correctly configured to work properly

# ADS1248 (1)

J.Szewinski, B.Yang (NCBJ, DESY)

TMCB Firmware

16.12.2011 16 / 20

# ADS1248 (2)

16.12.2011 17/20

## ADS1248 (3)

J.Szewinski, B.Yang (NCBJ, DESY)

TMCB Firmware

16.12.2011 18/2

Issues:

- External RAM (SRAM, SDRAM) memory would make writing the embedded code easy.

- External EEPROM would be nice (for storing MAC address).

- Serial (USB-Serial) interface would be also nice (not critical).

Plans:

- DCM firmware is already being developed by B.Yang

- RF Optical fiberlink application will be developed by J.Szewinski

## Thank You

J.Szewinski, B.Yang (NCBJ, DESY)

TMCB Firmware

16.12.2011 20 / 20