# 103. Tagung der Studiengruppe elektronische Instrumentierung im Frühjahr 2012

in Dresden vom 12. März -14. März 2012

am

**Helmholtz-Zentrum Dresden Rossendorf**

Editor: Peter Göttlicher (DESY)

Verlag Deutsches Elektronen-Synchrotron

### Impressum

### 103. Tagung der Studiengruppe elektronische Instrumentierung im Frühjahr 2012 12.-14. März 2012, Dresden, Deutschland

Conference Homepage http://indico.desy.de/conferenceDisplay.py?confId=5248 oder https://indico.desy.de//event/SEI\_fruehjahr\_2012

Online Proceedings auf http://www-library.desy.de/confprocs.html

The copyright is governed by the Creative Commons agreement, which allows for free use and distribution of the articls for non-commertial activity, as long as the title, the authors' names and the place of the original are referenced.

Editor: Peter Göttlicher Juli 2012 DESY-PROC-2012-01 ISBN 978-3-935702-65-2 ISSN 1435-8077

Published by Verlag Deutsches Elektronen-Synchrotron Notkestraße 85 22607 Hamburg Germany

Printed by Kopierzentrale Deutsches Elektronen-Synchrotron

### 103. Tagung der Studiengruppe elektronische Instrumentierung im Frühjahr 2012

SEI - Studiengruppe elektronische Instrumentierung der Helmholtz-Zentren Dresden (HZDR), 12. März - 14. März 2012

### Inhaltsverzeichnis

| Allgemeines und Zusammenfassendes                                                                      |                             |    |

|--------------------------------------------------------------------------------------------------------|-----------------------------|----|

| Eröffnung und Ausblick                                                                                 | P. Göttlicher               | 3  |

| Bild der Teilnehmer                                                                                    | HZDR, PR-Abt.               | 4  |

| Tagungsprogramm                                                                                        |                             | 5  |

| Notizen aus der Tagung                                                                                 | D. Notz                     | 8  |

|                                                                                                        |                             |    |

| Vorträge<br>Ein Framework zur hochperformanten Verarbeitung von<br>Datenströmen mit digitaler Hardware | Prof. B. Lang               | 10 |

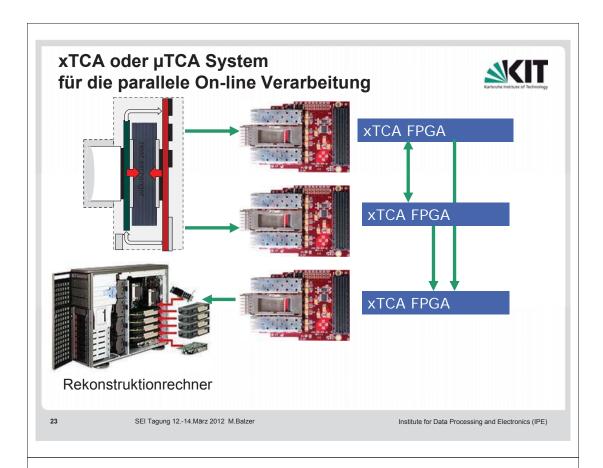

| FPGA framework development for modular high-speed DAQ system                                           | Q. Xia                      | 23 |

| Einführung des Kontrollsystems TANGO am Jülich<br>Centre for Neutron Science                           | H. Kleines                  | 37 |

| EtherCAT Feldbusknoten: Entwicklung, Systemunterstützung und -kompatibilität                           | P. Kaever                   | 47 |

| Simplify your LabVIEW-EPICS communication                                                              | C. Winkler,<br>J. Kuszynski | 54 |

| Customized Off-The-Shelf Technologies for building system platforms for Big Physics experiments        | L. Johansson                | 62 |

| Modulare Ethernet basierte DAQ- und MSR-Systeme                                                        | S. Hering<br>V. Thomas      | 77 |

| IPMI und MicroTCA Module Management - Aktuelle Entwicklungsarbeiten                                                                       | M. Drochner | 93  |

|-------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|

| Model Driven FPGA Design – An approach                                                                                                    | M. Penno    | 107 |

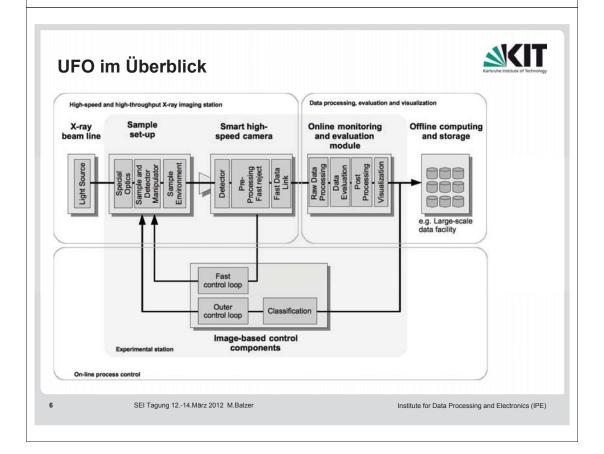

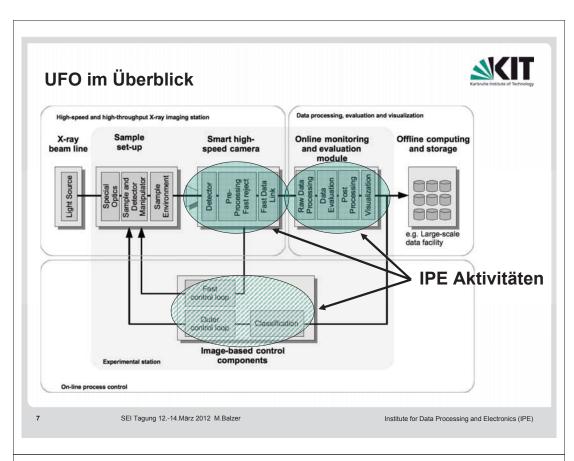

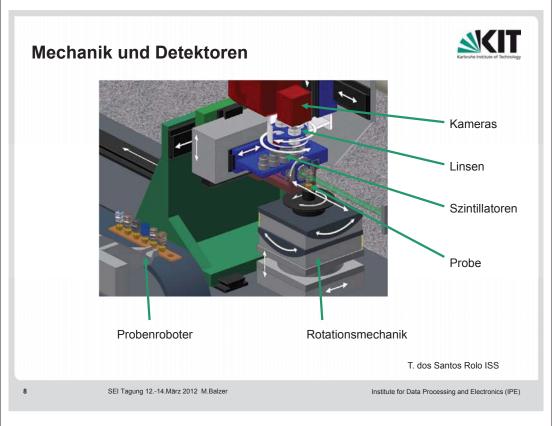

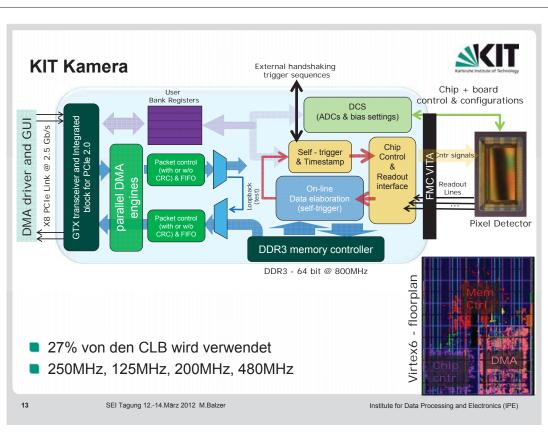

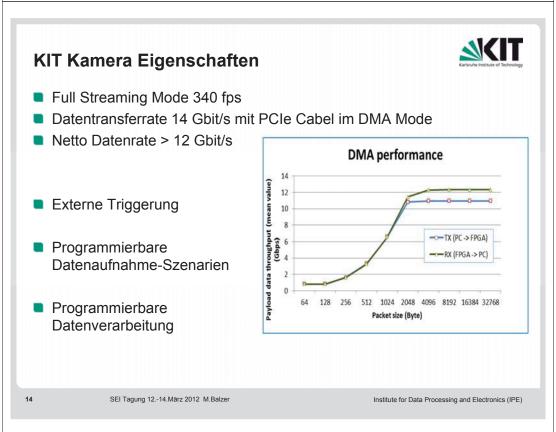

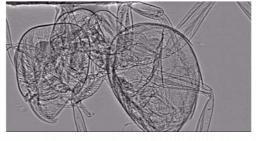

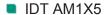

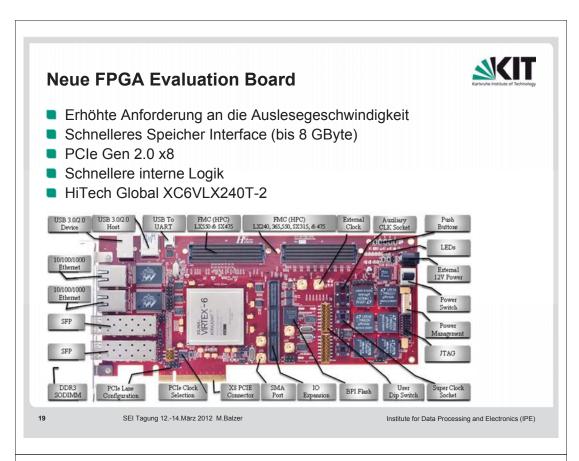

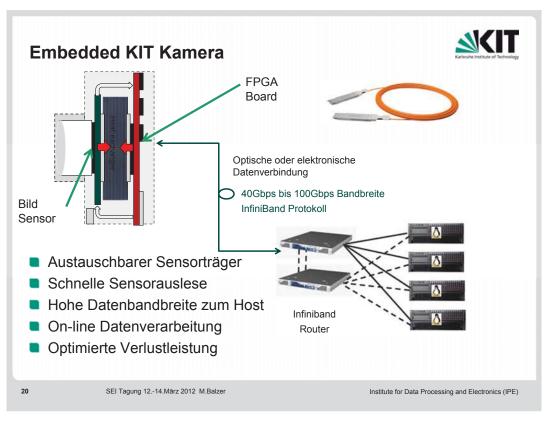

| KIT Kamera System für UFO                                                                                                                 | M. Balzer   | 121 |

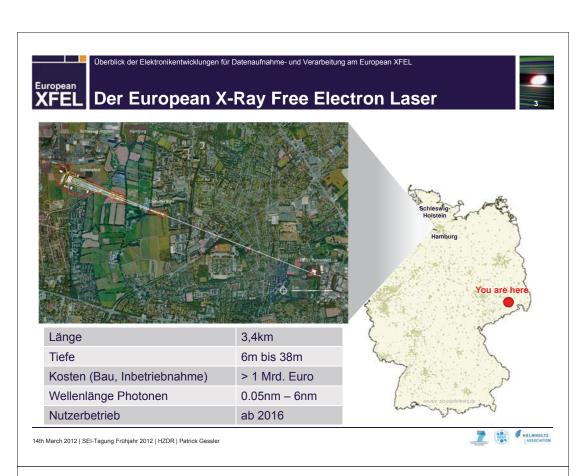

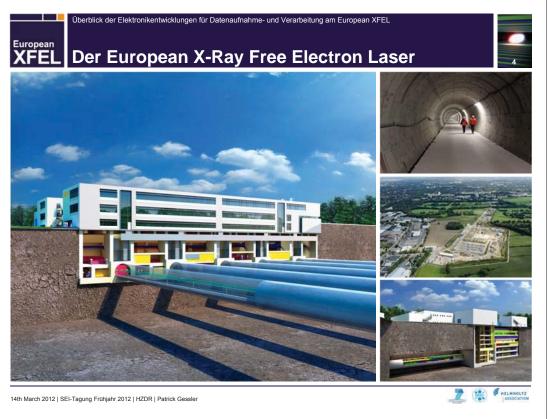

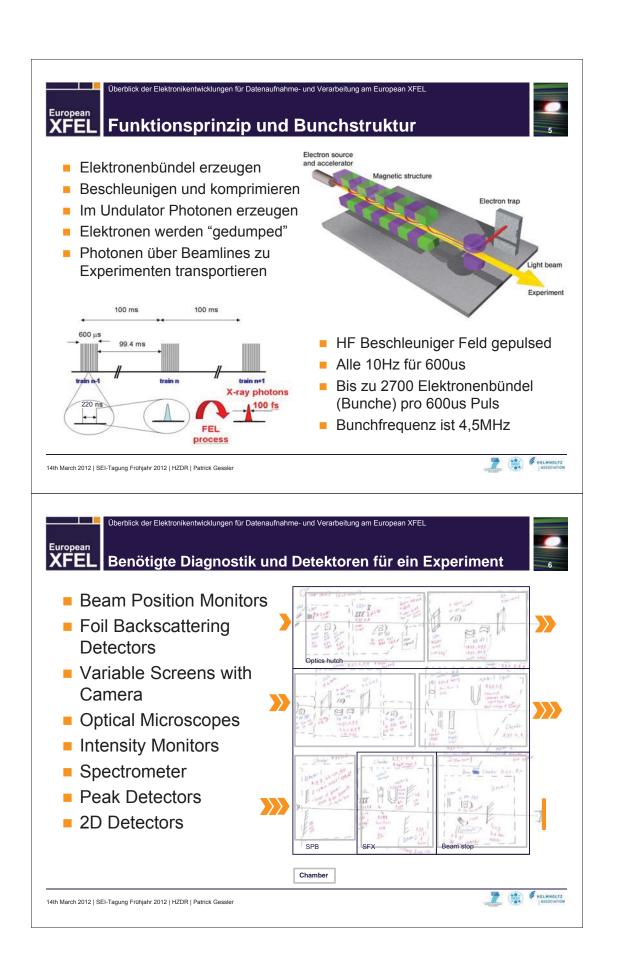

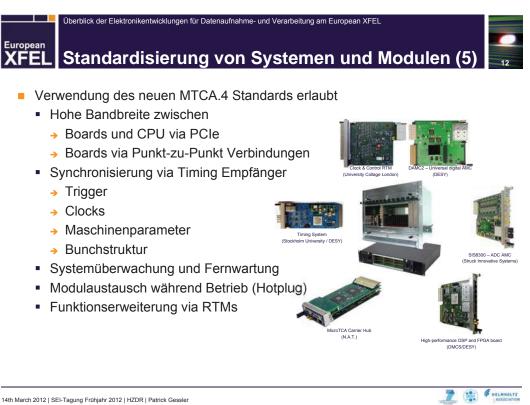

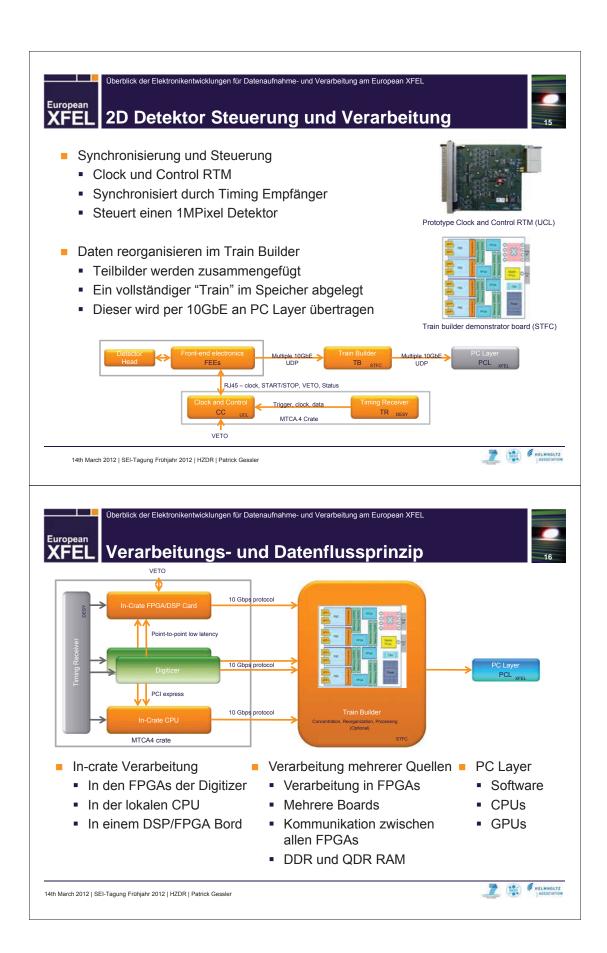

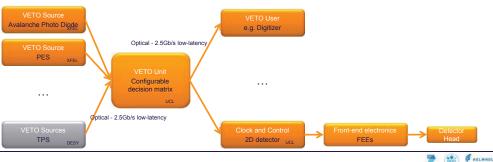

| Überblick über die Entwicklungen der Datenaufnahme-<br>und Verarbeitungssysteme fr Photon Beamlines und Ex-<br>perimente am European XFEL | P. Gessler  | 133 |

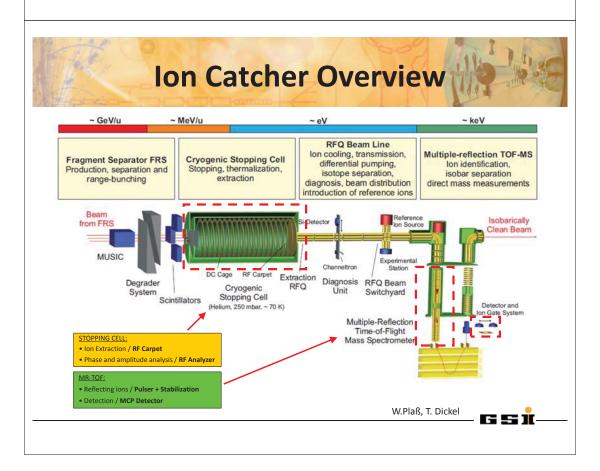

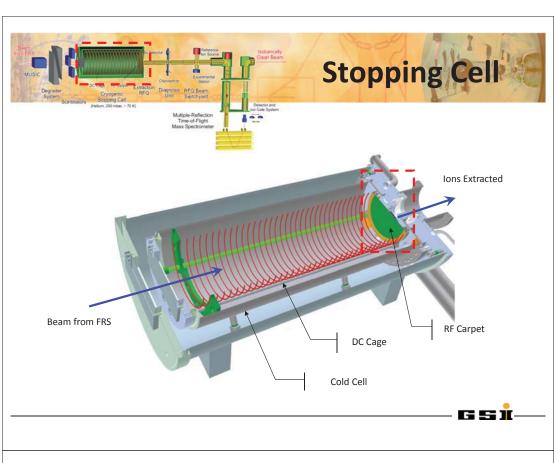

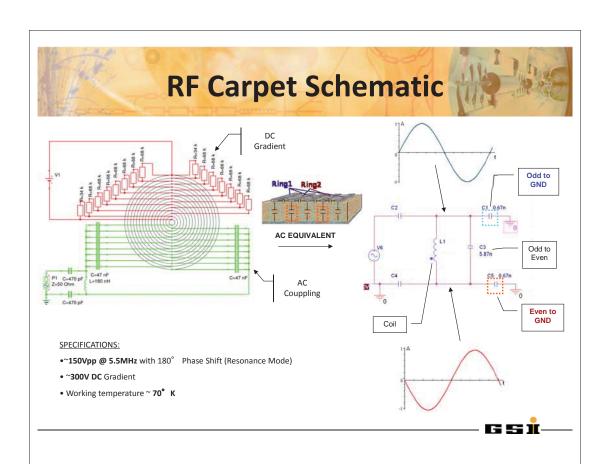

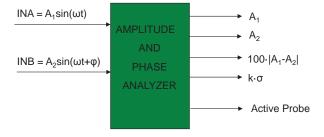

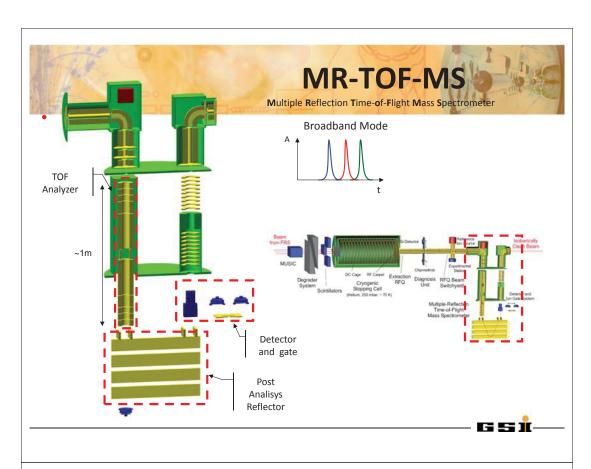

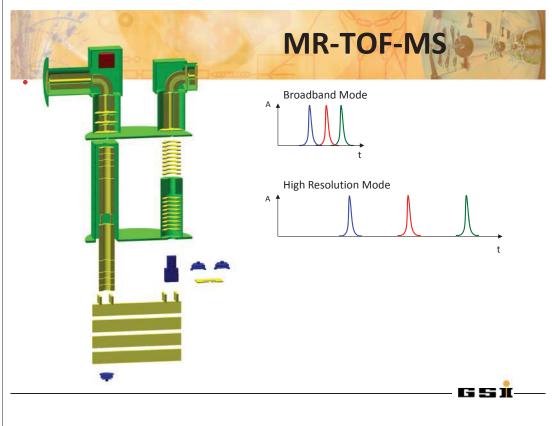

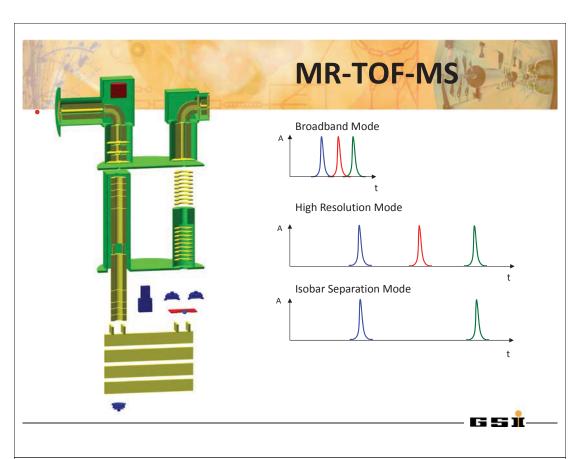

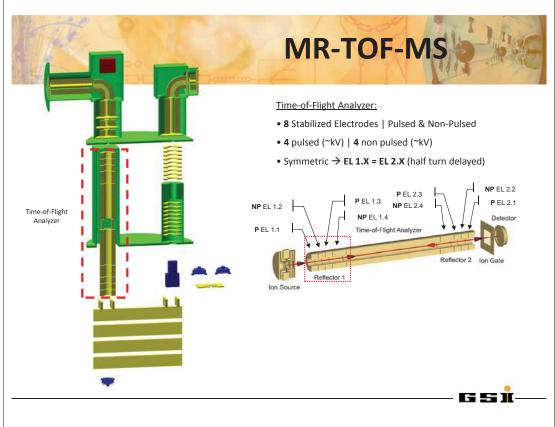

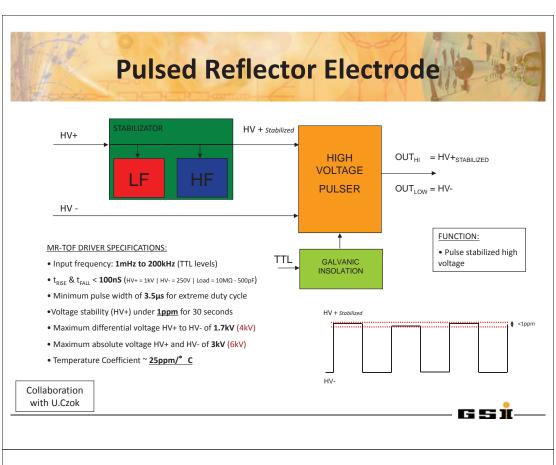

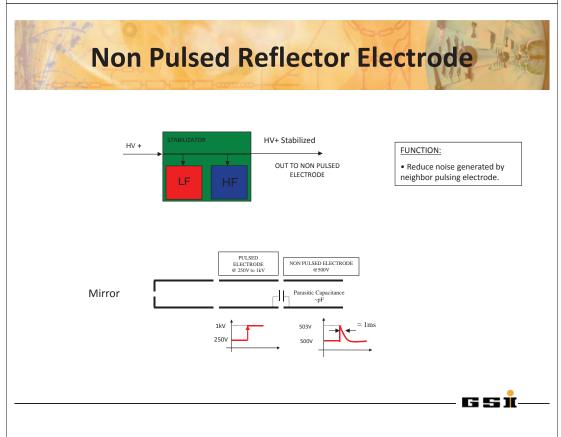

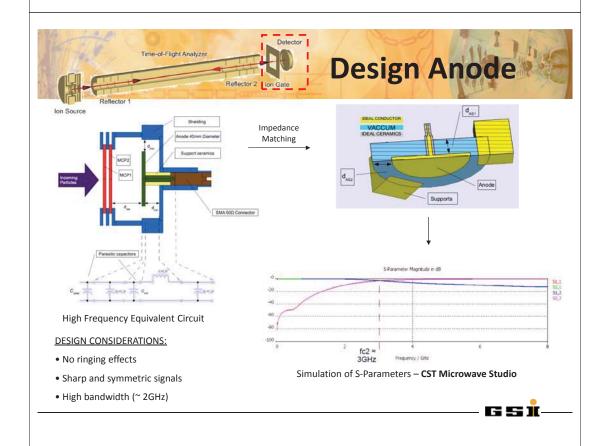

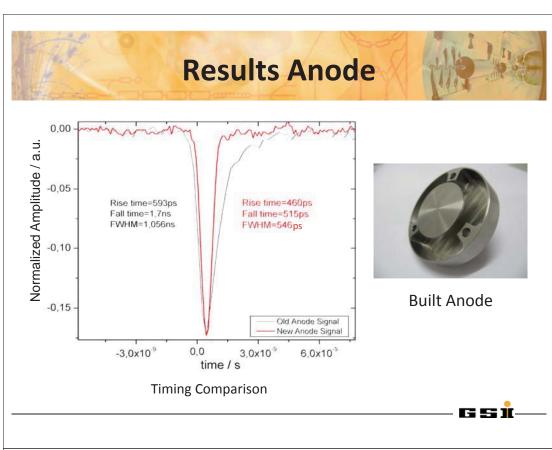

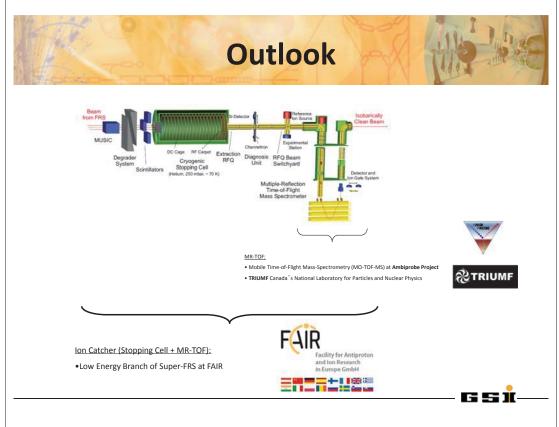

| Developed High Performance Electronics for the Gas<br>Filled Stopping Cell and MR-Time-of-Flight-MS of the<br>FRS Ion Catcher at GSI      | *           | 145 |

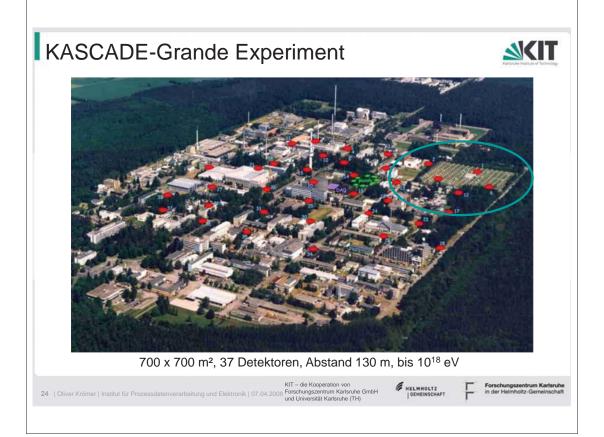

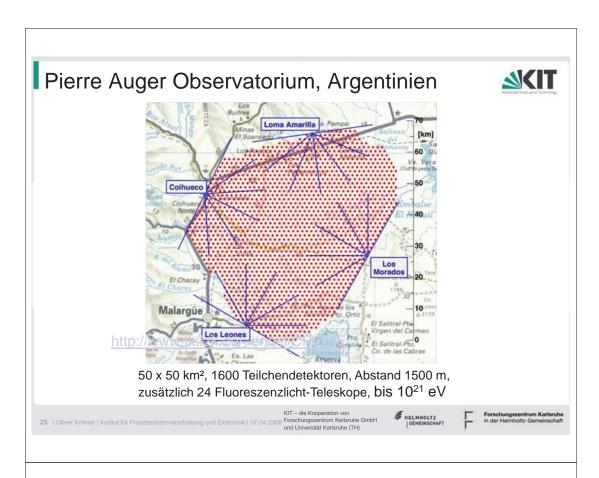

| Nachweis von Mikrowellenemissionen aus hochenergetischen kosmischen Luftschauern                                                          | O. Krömer   | 155 |

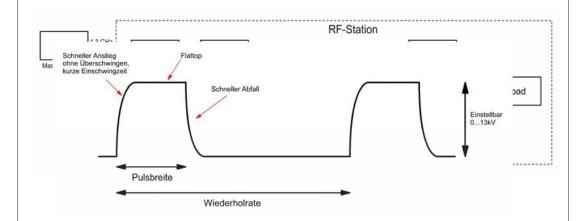

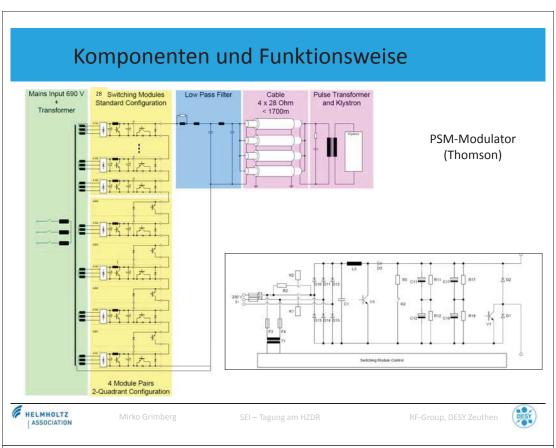

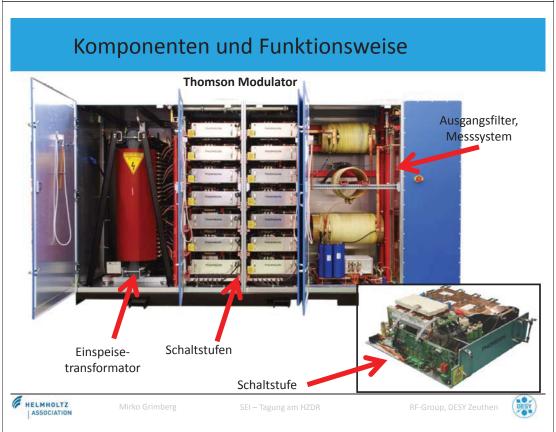

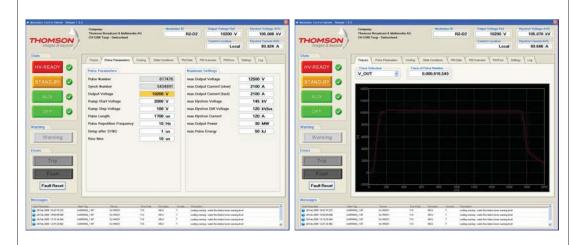

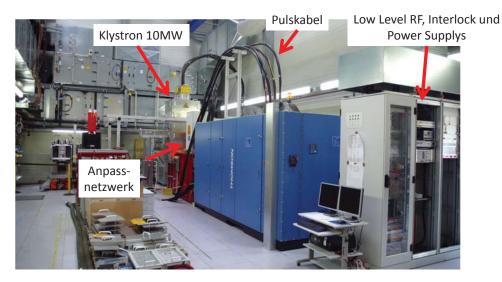

| Der Modulator Teststand Überblick, Ergebnisse und Ausblick                                                                                | M. Grimberg | 168 |

### Eröffnung

Zu der jährlichen Tagung, die allen Interessierten an Elektronik in der Forschung offensteht, kamen 66 Teilnehmer und -innen. Sie sind von verschiedenen Forschungs-einrichtungen, den Helmholtz-Zentren – DESY, FZJ, GSI, HZB, HZDR und KIT –, anderen Forschungseinrichtungen – XFEL, Universitäten und Hochschulen – und der Wirtschaft angereist.

Die Vorträge und Ausstellungen regten zu interessanten Diskussion zwischen den Teilnehmern an, so mal ähnliche Arbeitsmethoden an den verschiedenen Einrichtungen benutzt werden. Die abgedeckten Themen lassen sich zu den Schwerpunkten

- FPGA's und schnelle Datennahme,

- Messen-Steuern-Regeln und damit verbundene langsame Datennahme und Benutzeroberflächen und

- Systeme und Detektoren

zusammenfassen. Sie sind mit ähnlichen Gewichten vertreten gewesen.

Ein weiterer Inhalt wurde durch das lokale Labor HZDR gestaltet. So stellte Prof. Helm das Forschungszentrum als Vortrag vor, und wir konnten das Hochfeld-Magnetlabor auf dem Gelände besichtigen.

Auf einer Exkursion lernten wir auch die Gläserne Manufaktur kennen, wo eine moderne Fertigungsstraße so gestaltet ist, dass Besucher die technischen Tricks und Arbeitsabläufe der Automontage bei der realen Fertigung beobachten können.

Das Tagungsprogramm ist auf dem Internet einzusehen: http://indico.desy.de/conferenceDisplay.py?confId=5248 oder https://indico.desy.de//event/SEI\_fruehjahr\_2012

Die Homepage der Studiengruppe ist auf http://sei.desy.de/ zu finden.

### **Ausblick**

Die nächste Tagung wird für das Frühjahr 2013 in Jülich geplant.

Teilnehmer der Tagung SEI\_2012

Quelle: HZDR, PR-Abteilung

### Tagungsprogramm:

### SEI-Tagung am HZDR - Frühjahr 2012

## Studiengruppe elektronische Instrumentierung der Helmholtz-Zentren

### Monday 12 March 2012

### **Vortraege 1** - Haus 114 / Raum 201 (14:00-16:00)

| time  | title                                                                                      | presenter                                      |

|-------|--------------------------------------------------------------------------------------------|------------------------------------------------|

| 14:00 | HZDR - Helmholtz-Zentrum Dresden-Rossendorf                                                | Prof. HELM                                     |

| 14:30 | Eroeffnung                                                                                 | Dr. GOETTLICHER, peter (DESY)                  |

| 14:45 | Lokale Informationen                                                                       | Dr. KAEVER, Peter (HZDR)                       |

| 15:00 | Ein Framework zur hochperformanten Verarbeitung von Datenströmen mit digitaler<br>Hardware | Prof. LANG, Bernhard<br>(Hochschule Osnabrück) |

| 15:30 | FPGA framework development for modular high-speed DAQ system                               | Ms. XIA, Qingqing (DESY)                       |

### **Vortraege 2** - Haus 114 / Raum 201 (16:30-18:00)

| time  | title                                                                        | presenter                                                                                               |

|-------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 16:30 | Einführung des Kontrollsystems TANGO am Jülich Centre for Neutron Science    | Mr. KLEINES, Harald<br>(Forschungszentrum Jülich<br>GmbH)                                               |

| 17:00 | EtherCAT Feldbusknoten: Entwicklung, Systemunterstützung und -kompatibilität | Dr. KAEVER, Peter (HZDR)                                                                                |

| 17:30 | Simplify your LabVIEW-EPICS communication                                    | Mr. WINKLER, Carsten<br>(Helmholtz-Zentrum Berlin)<br>Mr. KUSZYNSKI, Jens<br>(Helmholtz-Zentrum Berlin) |

### **Busfahrt zum Abendessen, Linie 261** - ---- (18:13-18:20)

4:---- 4:4]-

| time title                               | presenter |

|------------------------------------------|-----------|

| 18:13 Busfahrt zum Abendessen, Linie 261 |           |

### **Busfahrt zum Hotel:Linie 261 spaetestens 21:17** - ---- (21:17-21:52)

| ume   | uue                                             | presenter |

|-------|-------------------------------------------------|-----------|

| 21:17 | Busfahrt zum Hotel: Linie 261, spätestens 21:17 |           |

### Tuesday 13 March 2012

### **Vortrage 3** - Haus 114 / Raum 201 (09:00-10:30)

| time  | title                                                                                              | presenter                                                                                         |

|-------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 09:00 | Customized Off-The-Shelf Technologies for building system platforms for Big<br>Physics experiments | Mr. JOHANSSON, Leif (National Instruments)                                                        |

| 09:30 | Modulare Ethernet basierte DAQ- und MSR-Systeme                                                    | Mr. HERING, Stephan (systerra<br>computer GmbH)<br>Mr. THOMAS, Volker (systerra<br>computer GmbH) |

| 10:00 | IPMI und MicroTCA Module Management - Aktuelle Entwicklungsarbeiten                                | Mr. DROCHNER, Matthias (FZJ)                                                                      |

### **<u>Firmenausstellungen</u>** - Haus 114 / Raum 201 (10:30-13:30)

### Parallel pro Firma 1Tisch+Strom , Kaffee

| time  | title                                                                                  | presenter                                                |

|-------|----------------------------------------------------------------------------------------|----------------------------------------------------------|

| 10:30 | Beckhoff - New Automation Technology                                                   | Mr. BURANDT, Nils (Beckhoff<br>Automation GmbH)          |

| 10:31 | Agilent SA Acqiris Operation                                                           | SPELTHANN, Hans Dieter<br>(Agilent SA Acqiris Operation) |

| 10:32 | Ausstellung der iseg Spezial- elektronik                                               | DONIX, Maik (iseg<br>Spezialelektronik GmbH)             |

| 10:33 | Ausstellung computer- gestützter Messtechnik National Instruments                      | Mr. YI, David (National<br>Instruments Germany GmbH)     |

| 10:34 | powerBridge Computer: MTCA.4 Solutions                                                 | Mr. HOLZAPFEL, Thomas<br>(powerBridge Computer)          |

| 10:35 | Struck Innovative Systeme GmbH                                                         | Dr. MATTHIAS, Kirsch (Struck<br>Innovative Systeme GmbH) |

| 10:36 | systerra computer GmbH: Modulare DAQ Systeme, Netzwerk- technik und Industrie-Computer | Mr. HERING, Stephan (systerra computer GmbH)             |

| 10:37 | WIENER Plein & Baus GmbH: Produkt- ausstellung                                         | Mr. KOESTER, Andreas<br>(WIENER Plein + Baus GmbH)       |

### Führung durch das Magnet-Hochstrom-Labor - Haus 114 / Raum 201 (13:30-14:30)

| time  | title | presenter |

|-------|-------|-----------|

| 13:30 |       |           |

## <u>Exkursion: Gläserne Manufaktur: Link: http://www.glaesernemanufaktur.de/</u> - to be announced (14:45-18:30)

| time  | title                       | presenter |

|-------|-----------------------------|-----------|

| 14:45 | Anfahrt                     |           |

| 15:45 | Führung gläserne Manufaktur |           |

| 17:30 | Gang/ Fahrt zum Abendessen  |           |

### Wednesday 14 March 2012

### Vortraege 4 - Haus 114 / Raum 201 (09:00-11:00)

| time  | title                                                                                                                                 | presenter                                    |

|-------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 09:00 | Model Driven FPGA Design – An approach                                                                                                | Mr. PENNO, Marek (DESY)                      |

| 09:30 | KIT Kamera System für UFO                                                                                                             | Mr. BALZER, Matthias (KIT)                   |

| 10:00 | Überblick über die Entwicklungen der Datenaufnahme- und Verarbeitungssysteme für<br>Photon Beamlines und Experimente am European XFEL | Mr. GESSLER, Patrick (European<br>XFEL GmbH) |

| 10:30 | Developed High Performance Electronics for the Gas Filled Stopping Cell and MR-Time-of-Flight-MS of the FRS Ion Catcher at GSI        | Mr. AYET SAN ANDRES,<br>Samuel (GSI)         |

### **Vortraege 5** - Haus 114 / Raum 201 (11:30-13:00)

| time  | title                                                                               | presenter                                                         |

|-------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| 11:30 | Nachweis von Mikrowellenemissionen aus hochenergetischen kosmischen<br>Luftschauern | Dr. KRöMER, Oliver (Karlsruher<br>Institut für Technologie (KIT)) |

| 12:00 | Der Modulator Teststand – Überblick, Ergebnisse und Ausblick                        | Mr. GRIMBERG, Mirko (DESY)                                        |

| 12:30 | Abschluss der Tagung                                                                | Dr. GOETTLICHER, peter<br>(DESY)                                  |

D. Notz 20. 3. 2012

**Betr**: Gesprächsnotizen über die Frühjahrstagung **der Studiengruppe Elektronische Instrumentierung** vom 12. bis 14. 3. 2012 beim HZDR (Rossendorf) (103. SEI Tagung)

### Für DESY von Interesse

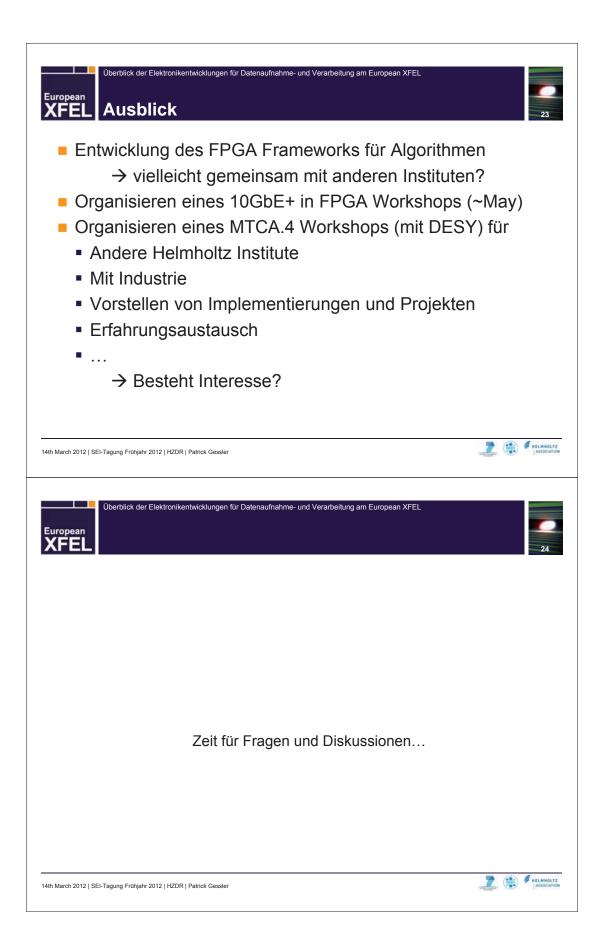

Es gibt Überlegungen, einen µTCA Workshop (bei DESY?) zu veranstalten. Es wurden mehrere Tools zur Programmierung von FPGAs vorgestellt.

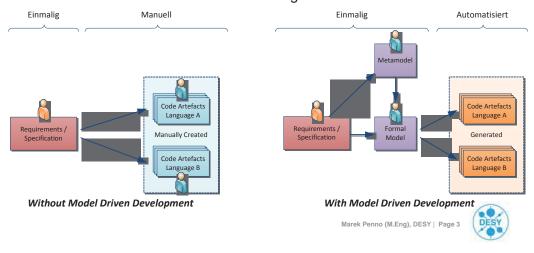

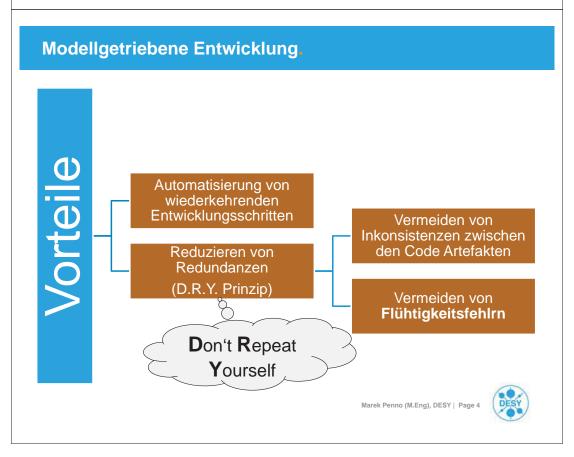

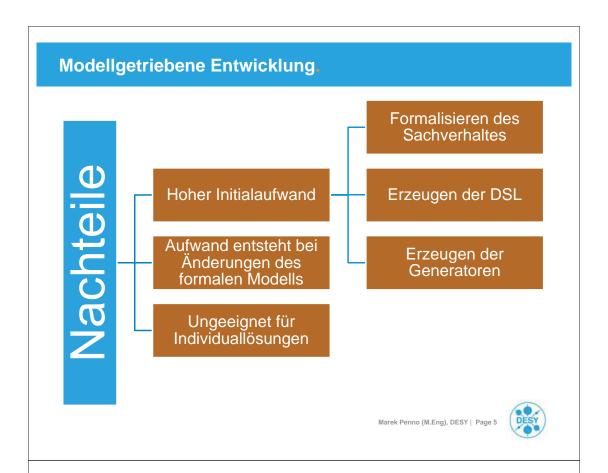

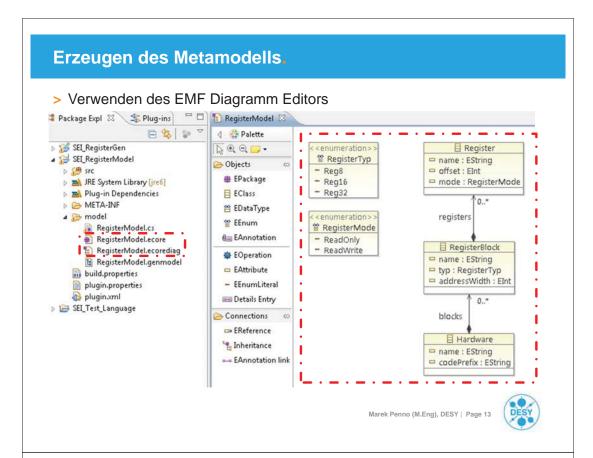

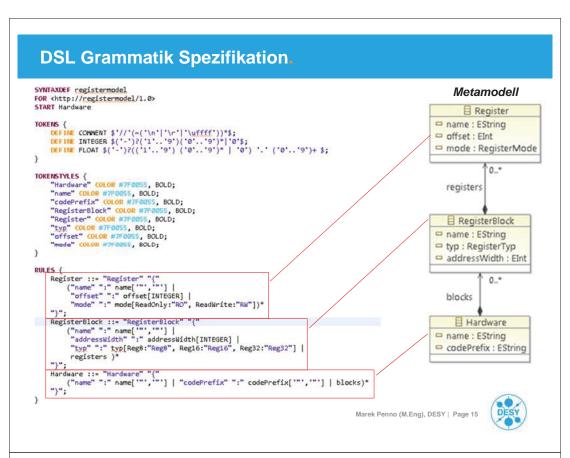

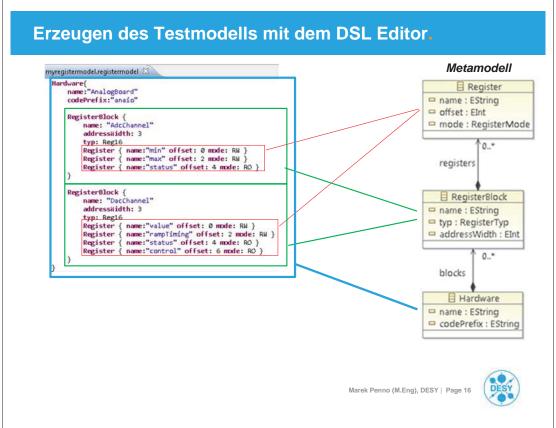

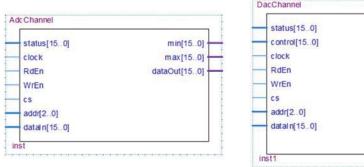

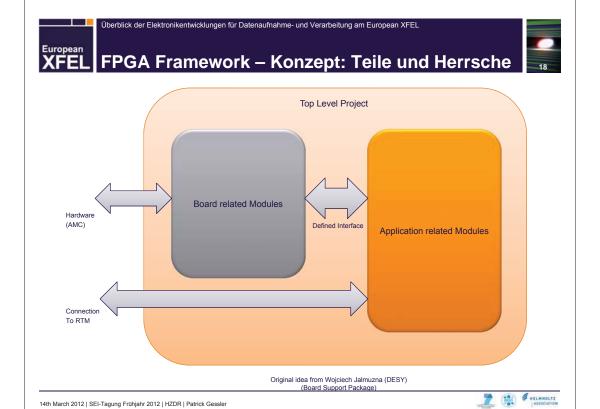

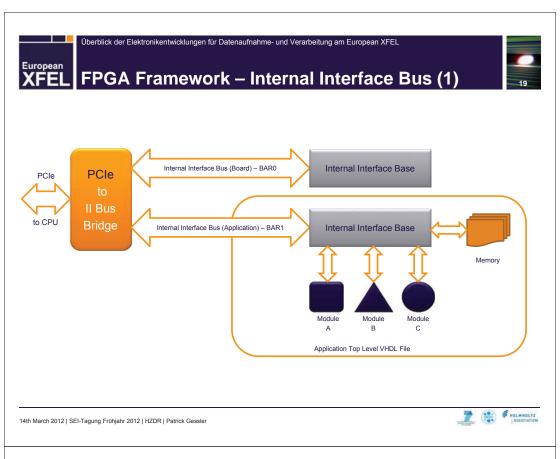

DSL = Domain Specific Language; modellgetriebene Modelle. D.R.Y: Don't repeat yourself. Wiederholungen und Redundanzen reduzieren. Eclipse Modelling Framework (EMF) basiert auf Java oder XML (www s. u.). Board related modules, application related frameworks. Simulink für Algorithmen. Das Einarbeiten in die verschiedenen Systeme ist sehr zeitintensiv.

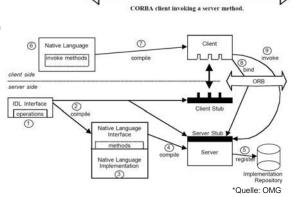

H. Kleines (FZJ) gab einen Übersichtsvortrag über verschiedene Kontrollsysteme. Das gegenwärtige Kontrollsystem für die Neutronenexperimente ist TACO. Übergang zu TANGO. Es herrscht große Vielfalt: Client/Server Systeme: ILL: MAD, NOMAD (CORBA); NIST: ICP; SNS: pyDAS mit Python; HFIR LabVIEW; HZB Berlin: CARESS (CORBA).

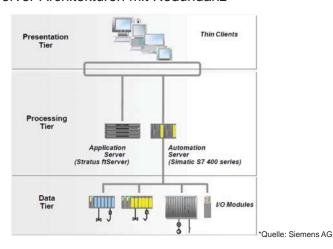

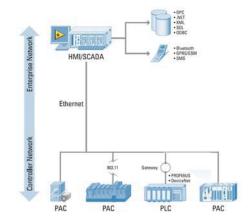

SCADA Systeme (Supervisory Control and DAQ): Wonderware InTouch, Siemens WinCC.

DCS (Distributed Control Systems): Siemens PCS7, EPICS.

CORBA (Common Object Request Broker Architecture): Von OMG standardisiert. IDL (Interface Definition Language) basiert auf C++ und Java.

Industrielle Kontrollsysteme basierend auf Windows ActiveX, .Net, VB-Skripting. Kontrollsysteme in der Forschung: PVSSII, EPICS,Yokogava; DESY: TINE, DOOCS, TANGO, EPICS; CERN: FESA, UNICOS, JCOP; FAIR: FESA; ITER TANGO vs. EPICS, das DOE hat sich mit EPICS durchgesetzt. HZB (Berlin) benutzt LabVIEW. Real time ist leider noch nicht unterstützt.

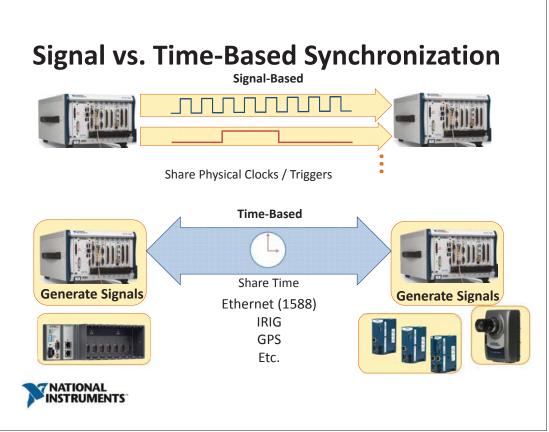

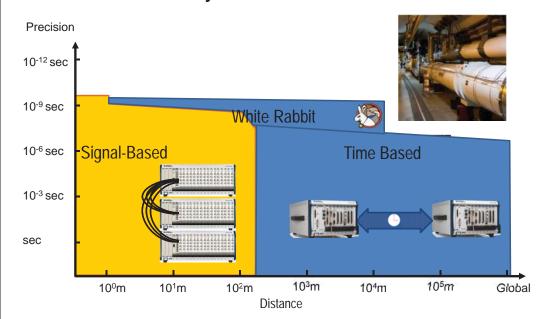

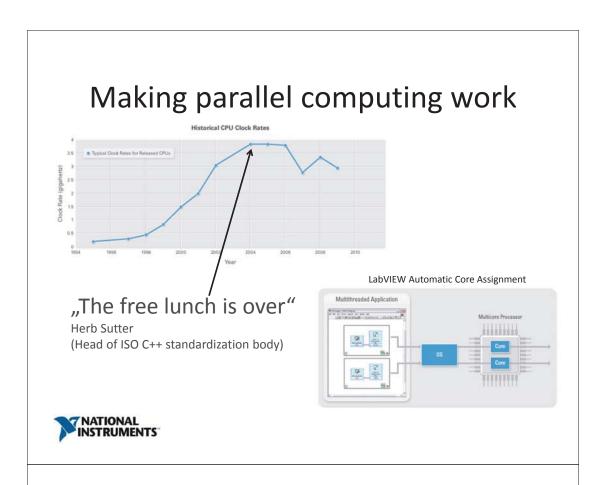

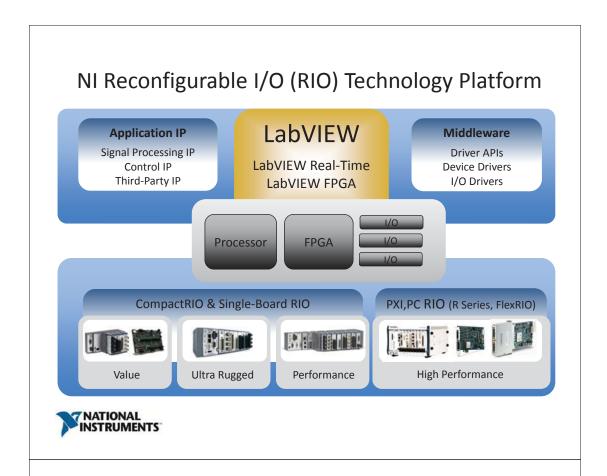

National Instruments (NI) hat enge Zusammenarbeit mit XILINX, TI (Texas Instr) und Analog Devices. Zusammenarbeit mit CERN im Rahmen von White Rabbit mit 10 km Abständen, mehr als 2000 Knoten und Zeitgenauigkeit von < 1ns Skew und 100 ps Jitter. Arbeiten an Multi-Core Prozessoren.

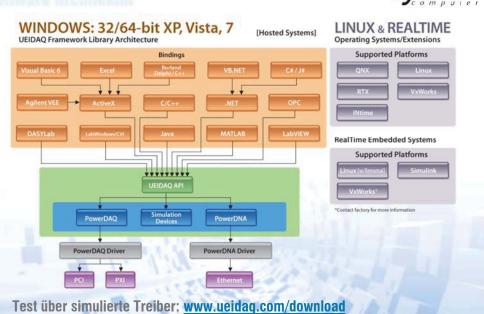

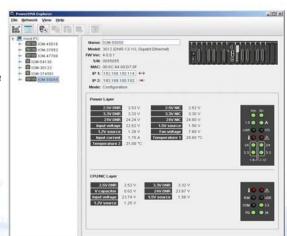

Systerra beschrieb ihre Zusammenarbeit mit United Electronic Industries (UEI). Module sind klein. System basiert auf Simulink. *Bei Kontrolllampen werden die Einschaltstromkurven gemessen, um rechtzeitig zu sehen, ob Birnen ausgewechselt werden müssen.* Benutzung in Flugsimulatoren. Hohe Verfügbarkeit. Plattformen Linux und VxWorks. Es gibt Quellcodes zu jedem Modul. 10 Jahre Nachkaufgarantie. Alterung von Elektrolytkondensatoren. Geräte nachkallibrieren.

### Sonstiges

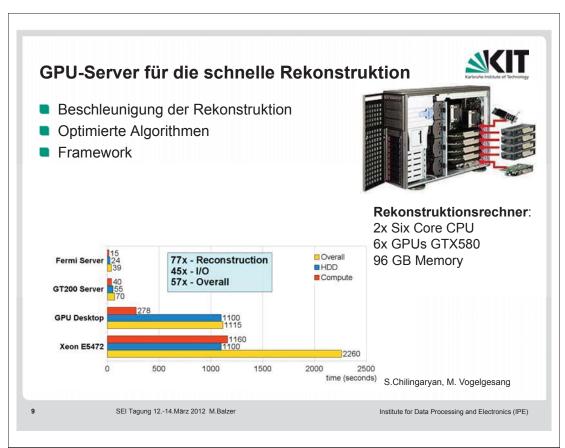

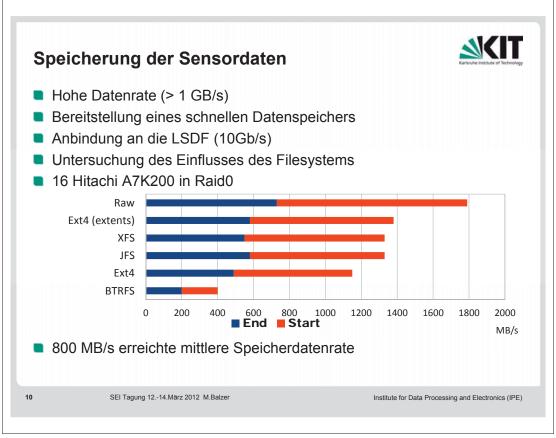

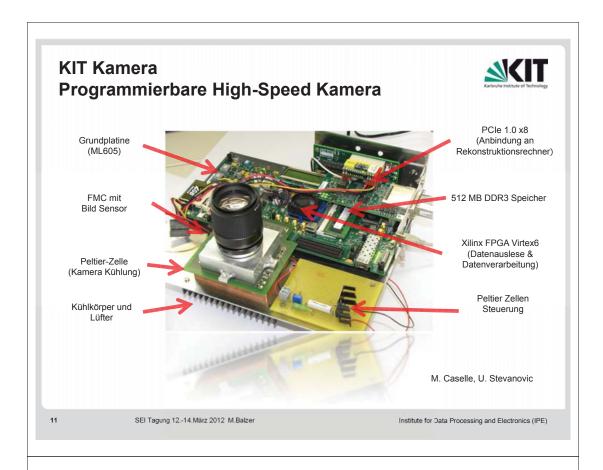

Rossendorf (HZDR) benutzt EtherCAT mit Feldbusknoten von Siemens und Beckhoff. Die ultra fast imaging Camera (UFO) beim KIT braucht viel Rechenpower: 2\*6 Core CPU, 6 GPUs GTX580, 96 GB Memory, XFS File System. Der CMOSIS Sensor CMV2000 liefert bis zu 340 Frames/s. Verlustfreie Kompression.

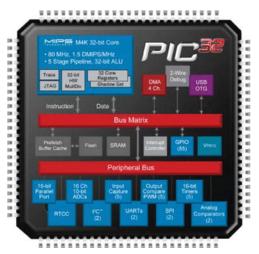

FZJ baut eigenen Management Controller für  $\mu$ TCA zum Steuern von Netzteil oder Lüfter. Benutzter Chip: PIC32MX460. Kann mehr als benötigt, ist aber preiswert. Schnelles I/O und auch JPAG. Bei den Backplanes für  $\mu$ TCA gibt es solche mit IP Adresse 192.168.16.17 oder 0.0.0.0. Empfohlen wird ersteres.

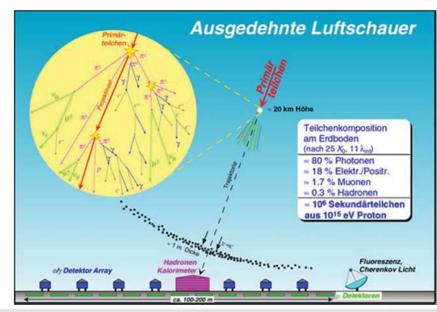

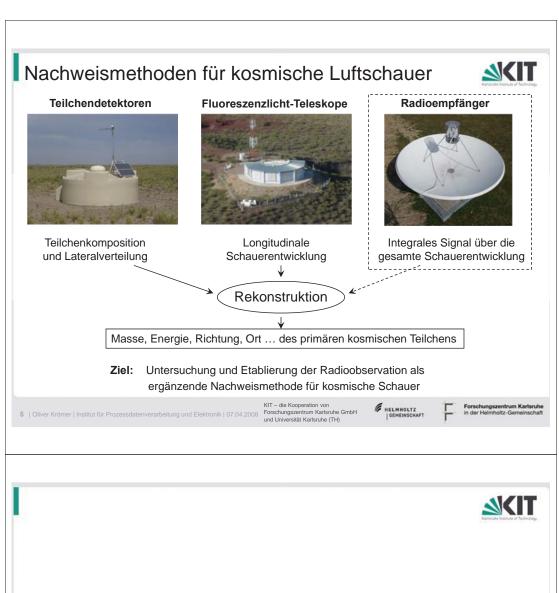

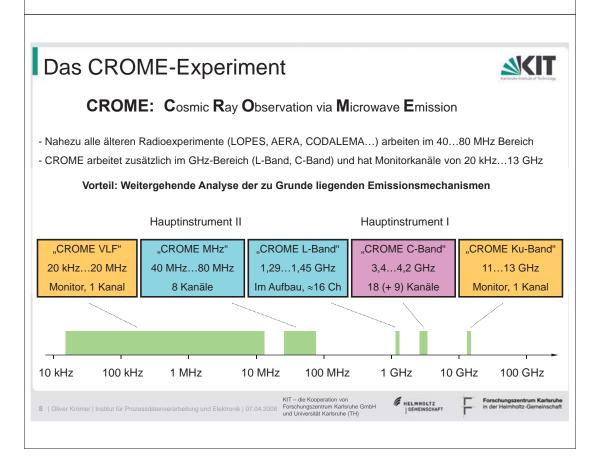

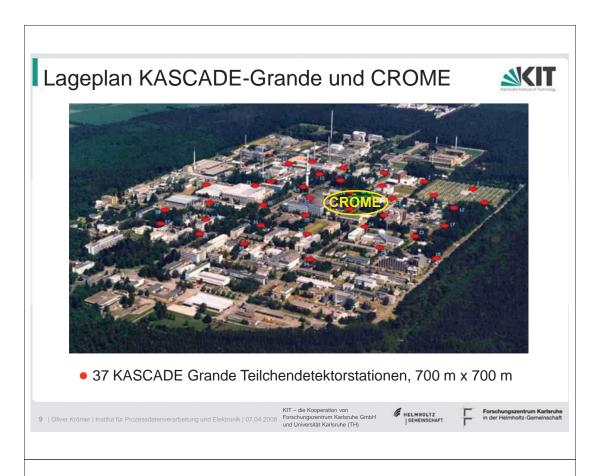

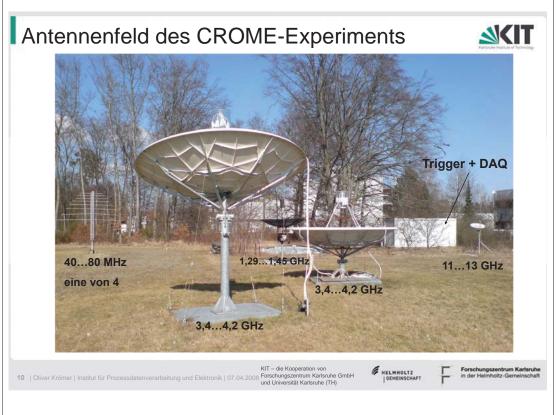

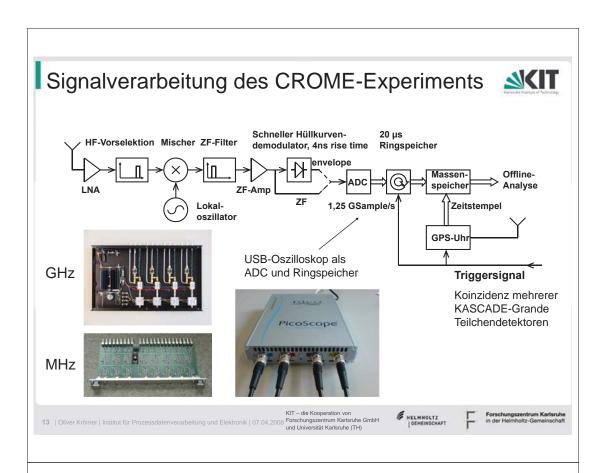

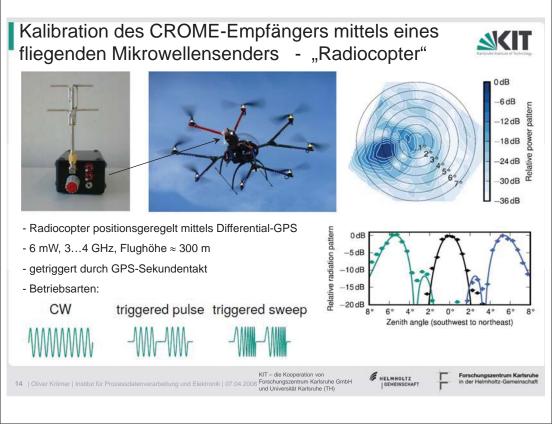

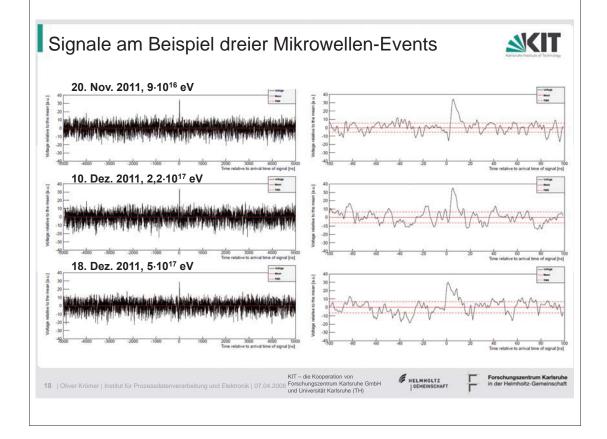

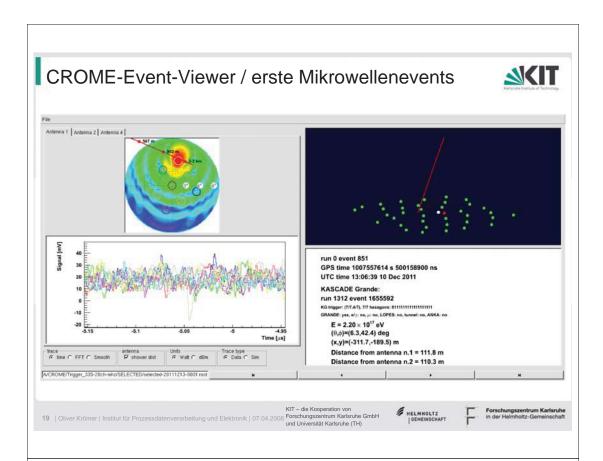

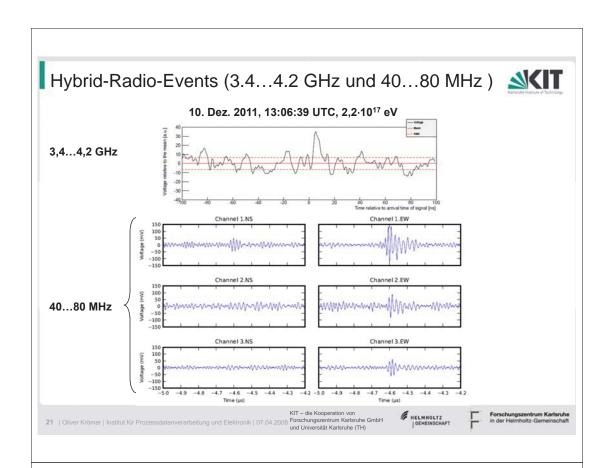

Zur Untersuchung von Luftschauern für das KIT Experiment Crome (Cosmic Ray Observation Microwave Emission) gibt es neue Radioempfänger. Einige Empfänger benutzen logarithmisch-periodische Dipolantennen. Zum Überprüfen der Anlage dient ein Mikrowellensender an einem RadioCopter Hubschrauber. Trigger kommt vom Kaskade Experiment.

### **WWW Informationen:**

http://zennotz.desy.de/SEI

<u>http://www.ueidaq.com/download</u> für United Electronic Industries Software zum Spielen.

http://de.wikipedia.org/wiki/Modellgetriebene\_Softwareentwicklung

http://www.emftext.org/index.php/EMFText

http://www.eclipse.org/modeling/emf/

http://www.eclipse.org

http://www.acceleo.org/pages/home/en

http://www.omg.org

http://www.omg.org/spec/MOFM2T/1.0/

### **Termine:**

9. – 15. 6. 2012 RT2012 Berkely 27.10. – 3. 11. 2012 IEEE NSSS Anaheim, CA, USA

### Nächste Treffen der Studiengruppe:

In Jülich, FZJ, ~März 2013

Stored in notz/ESONE/SEI/MINUTES/hzdr2012.doc (+.pdf)

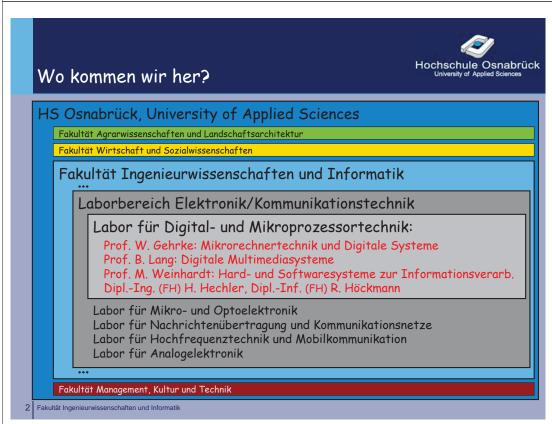

### Womit beschäftigen wir uns?

- · Programmierung

- Grundlagen, Objektorientiert

- Embedded Systeme, Treiberprogrammierung

- · Digitale Systeme und Rechnerarchitektur

- Programmierbare Logik (CPLDs, FPGAs)

- Hardwarebeschreibungsprachen (VHDL)

- Mikrocontroller, Soft-Prozessoren

- · Bild- und Videoverarbeitung

- Algorithmen

- Software-Modellierung

- Hardware-Realisierung

3 Fakultät Ingenieurwissenschaften und Informatik

### **Inhalt**

- Motivation

- · Erste Beispiele

- · Eigenschaften des Frameworks

- · Elementare Datenfluss-Komponenten

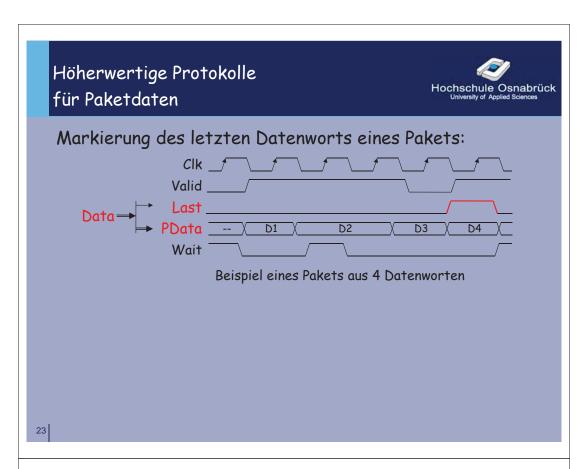

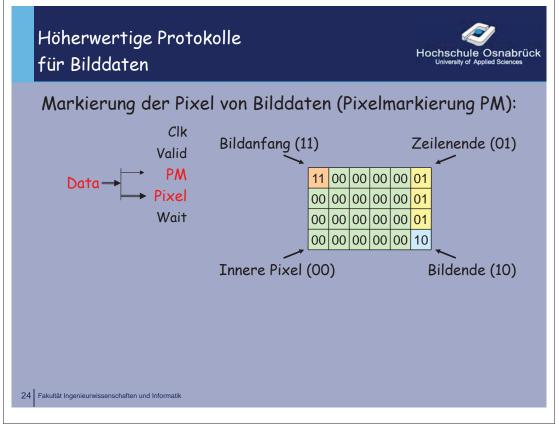

- Höherwertige Protokolle

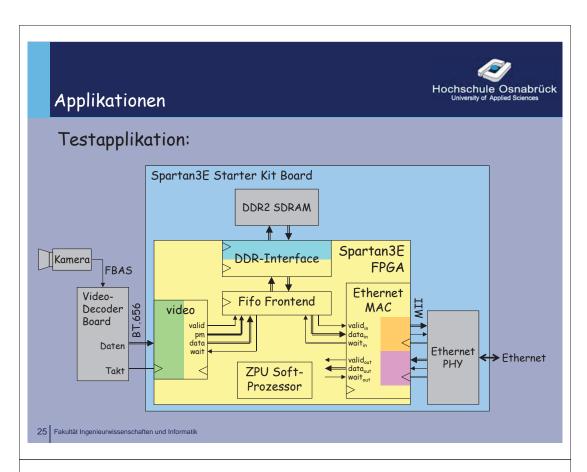

- Applikationen

### Motivation

In vielen technischen Anwendungen fallen Massendaten als Datenströme an, die schnell erfasst und verarbeitet werden müssen, z.B.:

- Bildverarbeitung

- Telekommunikation

- · Schnelle Sensoren, Detektoren

Ziele bei der Erfassung und Verarbeitung dieser Daten sind beispielsweise:

- Reduktion der Datenmenge durch Extraktion interessierender Information

- Lenkung von Datenströmen

- Speicherung von Daten-Bursts für die spätere Offline-Verarbeitung

5 Fakultät Ingenieurwissenschaften und Informatik

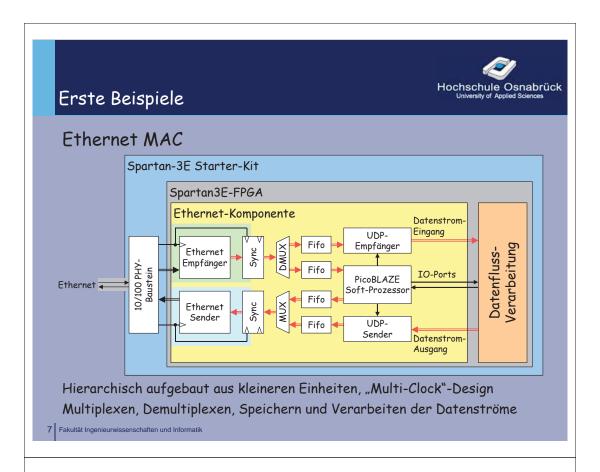

#### Hochschule Osnabrück Erste Beispiele Einfacher ATM-Switch (um 1993) Sync\_ai Eingangs-Daten\_ai FIFO Daten\_ai Wort/Byte Konversion stufe Idle-Zellen Takt\_ai > Takt\_ai Gener. ATM-Zellen Sync\_bi Sync bi Eingangs-FIFO Daten bi Daten bi stufe Takt\_bi → Takt\_bi FIFO Sync\_ci > Sync\_ci Eingangs-Daten\_ci FIFO Daten\_ci stufe Takt\_ci Takt\_ci Takt (Vorstudie für einen komplexen ASIC-Baustein) 6 Fakultät Ingenieurwissenschaften und Informatik

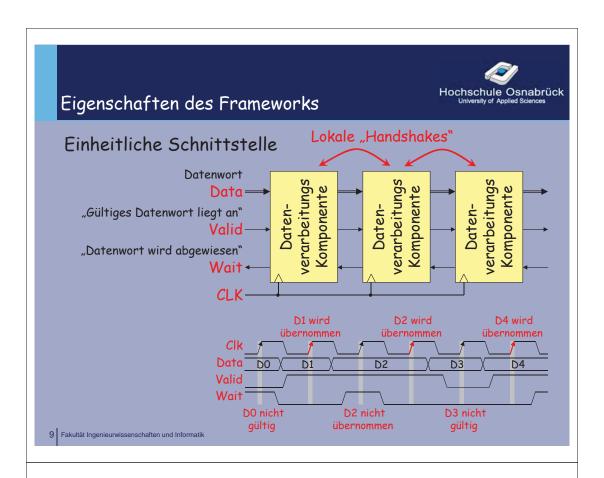

### Eigenschaften des Frameworks

Vorstellung eines Framework für die Verarbeitung synchroner, digitaler Datenströme.

Daten werde auf einer Schnittstelle unidirektional von einem Sender zu einem Empfänger weitergeleitet.

Es bietet an seinen Schnittstellen folgende elementare Eigenschaften für die Weiterleitung der Datenströme:

- Es ist schnell:

- Mit jeder Taktflanke kann die Weitergabe eines Datenworts erfolgen.

- Es ist flexibel:

- Gültige Datenworte werden vom Sender markiert.

- Die Übernahme eines angebotenen Datenworts kann vom Empfänger bei jeder Taktflanke abgewiesen werden.

Vergleichbar dem "ready-valid handshake protocol" (Dynalith Systems) und dem "AMBA AXI4-stream protocol" (ARM)

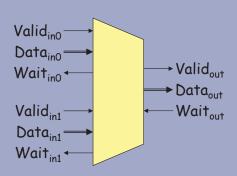

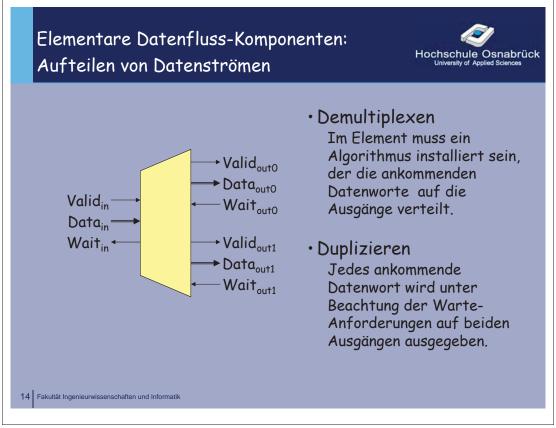

### Elementare Datenfluss-Komponenten zur Modellierung von Pipelinesystemen

Elementare Datenfluss-Komponenten des Frameworks:

- · Verarbeitung der Daten in der Pipeline

- · Aufteilen des Datenflusses (Demultiplex, Split)

- · Zusammenfügen von Datenflüssen (Multiplex, Merge)

- Synchronisation des Datenflusses

- · Synchronisation des "Warte"-Flusses

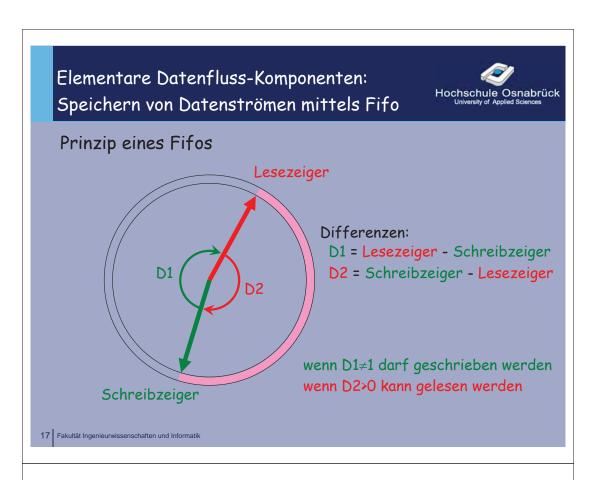

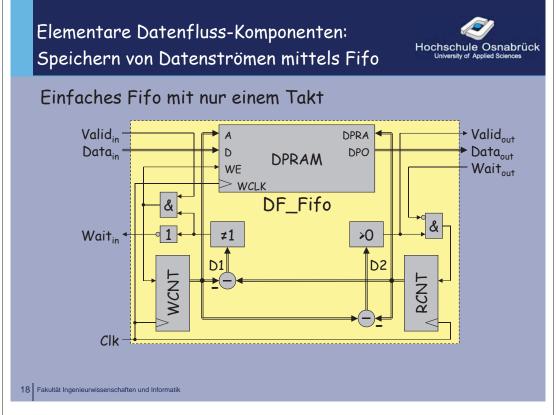

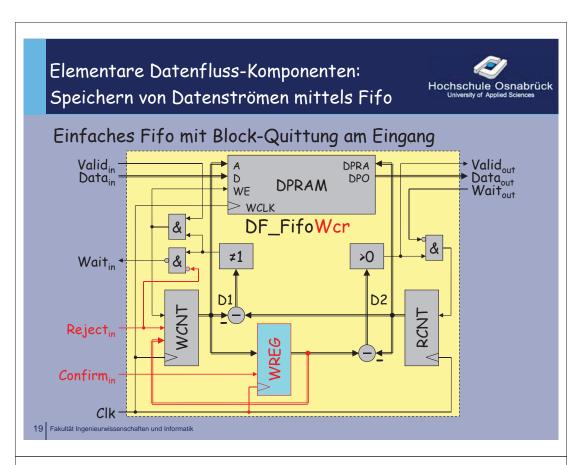

- · Zwischenspeichern von Datenflüssen

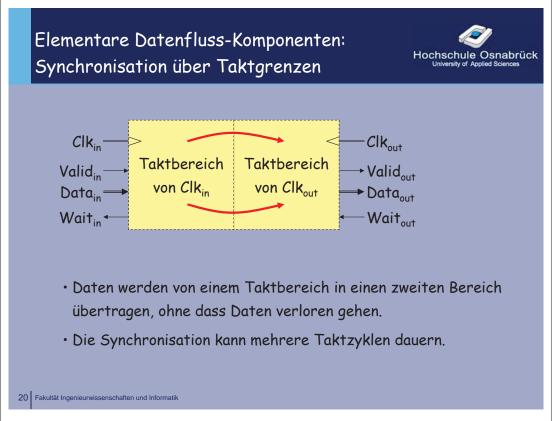

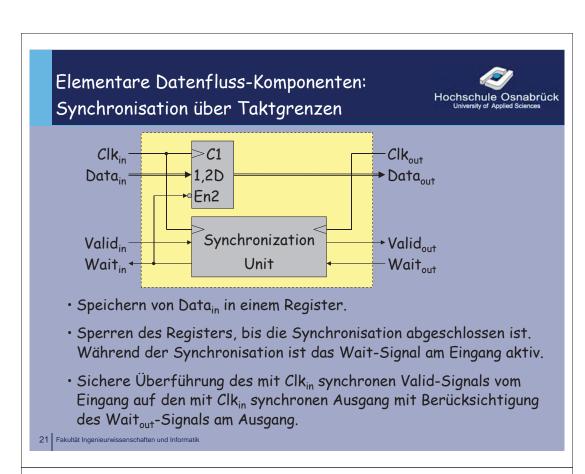

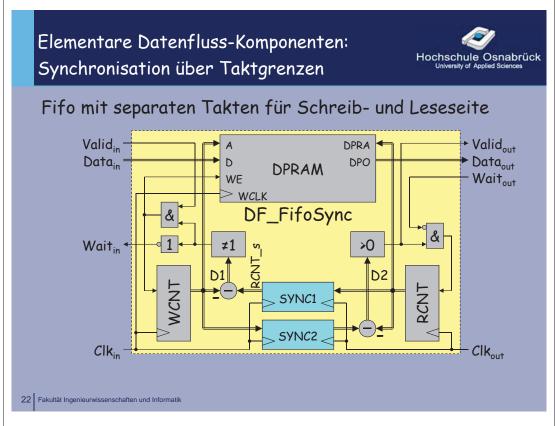

- · Überführung von Datenflüssen über Taktgrenzen

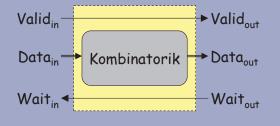

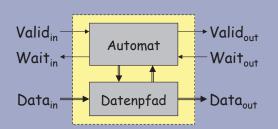

### Elementare Datenfluss-Komponenten: Verarbeitung von Datenströmen

Einfache Komponente Verarbeitung erzeugt kombinatorische Verzögerung auf den Datenleitungen

Komplexe Komponente Verzögerungen können auf den Datenleitungen und den Kontrollleitungen "Valid" und "Wait" entstehen.

11 Fakultät Ingenieurwissenschaften und Informatik

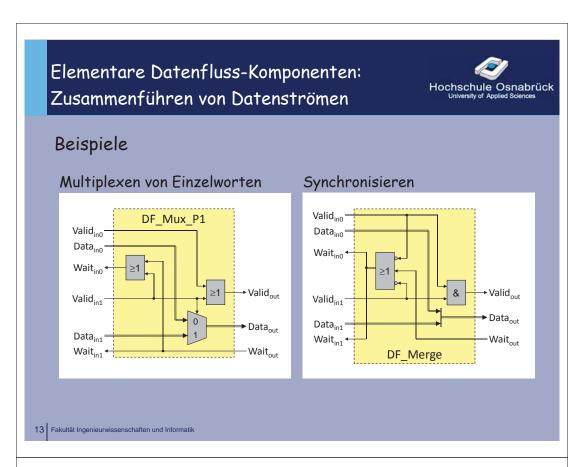

### Elementare Datenfluss-Komponenten: Zusammenführen von Datenströmen

Multiplexen

Zwei Datenströme gleicher Datenwortbreite werden zu einem Datenstrom zusammengefasst. Alle Datenworte beider Ströme bleibt eigenständig erhalten. Konflikte zwischen den Strömen müssen aufgelöst werden.

Synchronisieren Zwei Datenströme werden aufeinander synchronisiert. Die Datenworte der beiden Ströme werden paarweise zu einem Datenwort zusammengefasst.

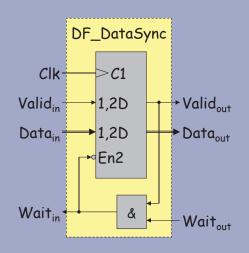

### Elementare Datenfluss-Komponenten: Synchronisierung in Datenflussrichtung

- Daten am Ausgang werden synchron mit dem Takt bereitgestellt.

- Eine Warteanforderung vom Ausgang wird nur dann an den Eingang weitergereicht, wenn im Sychnronisations-Register gültige Daten vorliegen.

15 Fakultät Ingenieurwissenschaften und Informatik

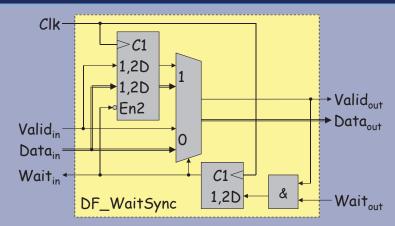

### Elementare Datenfluss-Komponenten: Synchronisierung in Warteflussrichtung

- · Daten werden vorsorglich in einem Register zwischengespeichert.

- Wenn am Ausgang eine Warteanforderung vorliegt, wird im folgenden Taktzyklus diese am Eingang aktiviert und das aktuelle Datenwort aus dem Register nochmals am Ausgang angelegt.

## **FPGA Framework Development For Modular High-Speed DAQ Systems**

Qingqing Xia FEA, DESY Hamburg SEI Conference HZDR Dresden, 12 March, 2012

### **Outline**

- > FEA Group

- Digital High Speed Electronics for DAQ Systems at Experiments and Accelerators

- > Hardware for Modular High-Speed DAQ Systems

- Modularity of MicroTCA Systems

- Hardware development for MicroTCA Systems

- > FPGA Framework Development

- Concept & Realization

- Framework Example: DAMC2 Framework Development

## FEA Group: Digital High Speed Electronics for DAQ Systems at Experiments and Accelerators

### > High-speed digital data acquisition and control systems

- System specification, design and development

- FPGA-based DAQ System

- □ xTCA: Modular card-based System (AMC,RTM)

- VMEbus, PX

- □ Fast serial links: 10-Gigabit-Ethernet

- PCI-Express

- DDR2 Memories

- PCB-Design/Layout

- FPGA-Firmware development

- Hardware-oriented software development

FMC with 2x 10-Gigabit-Ethernet Links

### > Centralized system administration for Mentor Graphics ECAD

- Client server installation

- Component library

- User project register/tracking

- Quality control

Qingqing Xia | SEI-Conference | 12 March, 2012 | Page 3

Hardware for Modular

High-Speed DAQ Systems

### Hardware for Modular High-Speed DAQ Systems

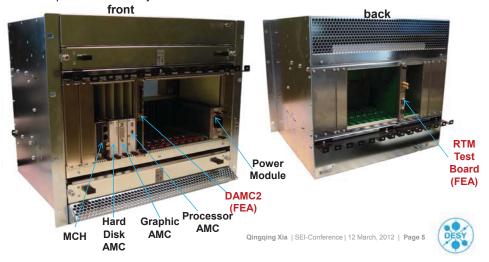

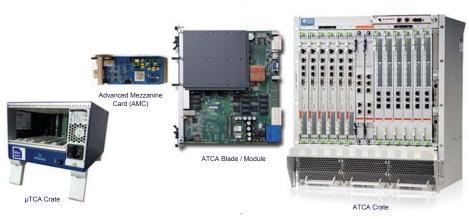

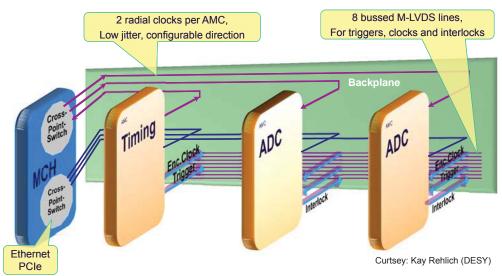

- MicroTCA system for Physics (MTCA.4)

- MTCA.4: http://www.picmg.org/v2internal/resourcepage2.cfm?id=5

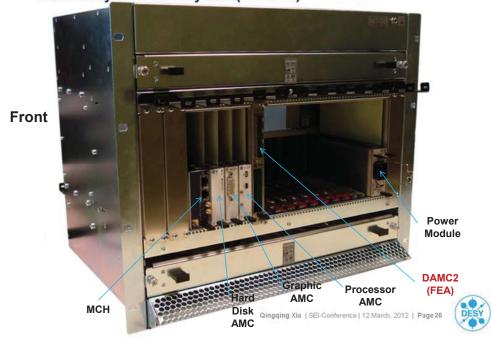

- MCH: MicroTCA Carrier HUB; AMC: Advanced Mezzanine Card

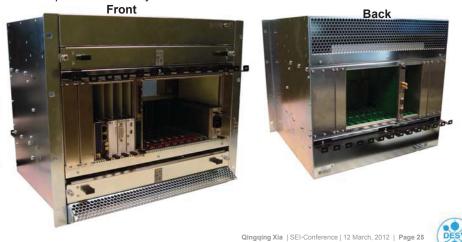

- Set-Up in our laboratory

### Hardware for Modular High-Speed DAQ Systems

MicroTCA system for Physics (MTCA.4)

### Modularity & Flexibility

Analog and digital rear transition I/O can be separated from the FPGA based front module

### Hardware for Modular High-Speed DAQ Systems

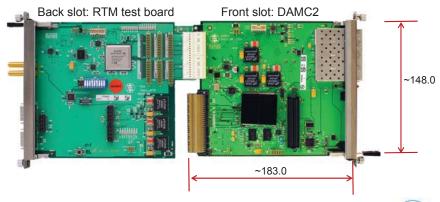

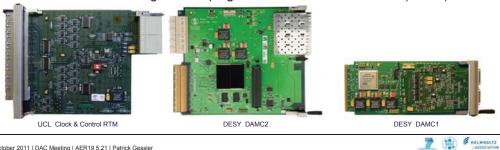

> DAMC2 (DESY Double Size AMC)

### **Key Features**

- FPGA: V5LX50T-1FFG1136

- Interface to "outside world"

- 4 Lanes PCIe from AMC-edge-connector

- Four SFP optical links

- FMC connector

- μRTM connector

- On board memories

- 2 x 512Mb DDR2 memories

- JTAG Interface

- Clocking

- 100MHz clock from AMC-edge-connector

- □ 2x I2C programmable oscillators(10M-810MHz)

- On-board LVDS 200MHz oscillator

### Board will be used for different applications!

## DESY

### Hardware for Modular High-Speed DAQ Systems

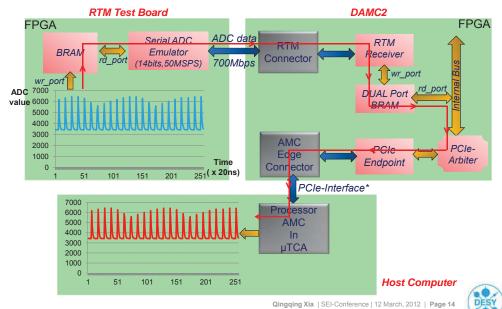

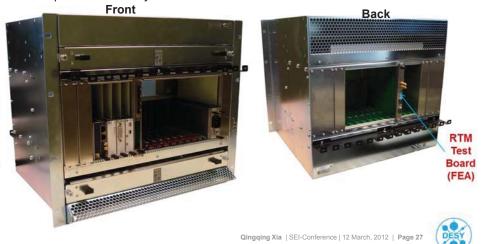

### > RTM Test Board

### Key Features

- FPGA: Data generator, Emulation of the behavior of different RTM boards

- Interface to front AMC board: 54 differential /108 single-ended signals

### **Application Example**

ADC Emulation: 14 bit 50MHz Sample Clock, 8 channels, on each channel 700Mbit/s 350MHz DDR (*Double Data Rate*) serial data

## FPGA Framework Development

Qingqing Xia | SEI-Conference | 12 March, 2012 | Page 9

### **FPGA Framework Development**

### > Concept

- FEA provides FPGA framework with VHDL/Verilog Modules for on board peripherals (PCle, DDR2, Ethernet,...)

- User copy over the FEA framework and then focus on developing algorithms for various projects

###

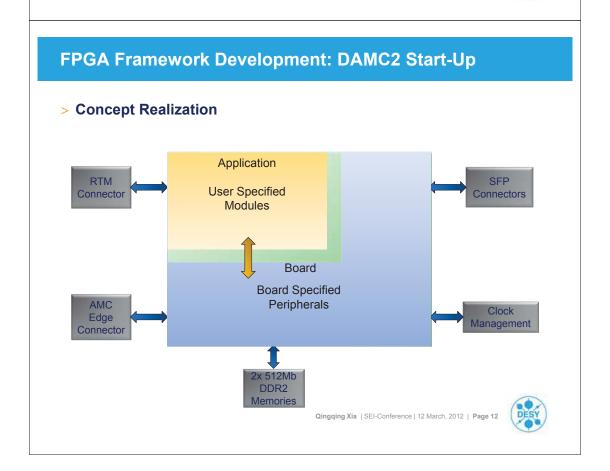

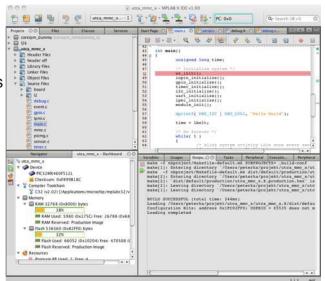

### **FPGA Framework Development: DAMC2 Start-Up**

### > Framework Block Diagram

### **FPGA Framework Development: DAMC2 Start-Up**

### > First Framework Chain-Test

### **FPGA Framework Development: DAMC2 Start-Up**

- > First version of DAMC2-StartUp Framework is ready for user

- > Further improvement, optimization, tests will be done in the near future

### Thank you!

Qingqing Xia | SEI-Conference | 12 March, 2012 | Page 15

### Spare Slides

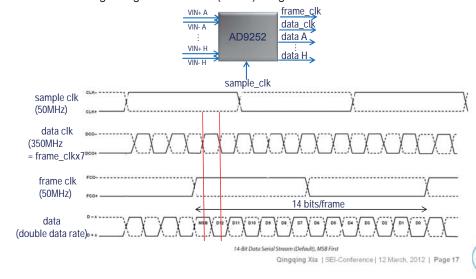

### **FPGA Framework Development: DAMC2 Start-Up**

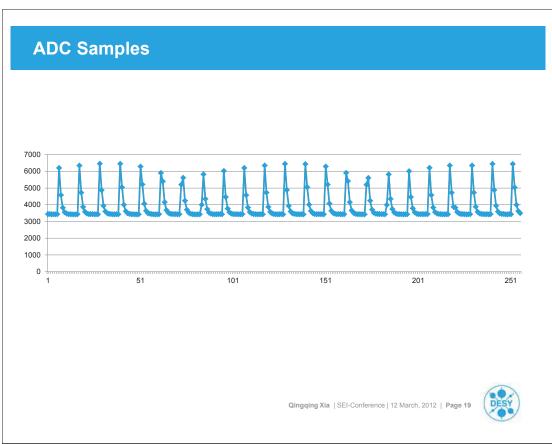

### > AD9252

- Octal, 14-Bit, 50 MSPS, Serial LVDS ADC

- 8 analog-to-digital converters (ADCs) integrated → 8 data channels

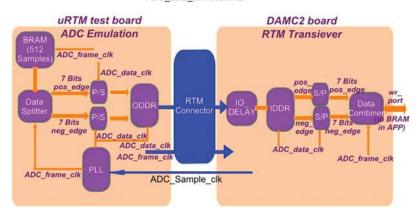

### **FPGA Framework Development**

- > 8-Channels ADC Emulation using uRTM test mode

- > Block diagram for one single channel (350 DDR serial data)

ADC\_frame\_clk=50MHz ADC\_data\_clk=350MHz

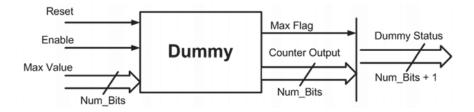

### **Dummy Module (Later Exercise)**

Simple configurable counter to show how to use the II bus data/strobes signals to configure/monitor user defined registers:

Asynchronous Reset with II bus Strobe (write or read cycle)

Enable implemented as Internal register (no Strobe required)

Max value configurable using II strobe + Data bus (write cycle only)

Monitor of Max value and Dummy Status

Bruno Fernandes, WP76 (DAQ & Control Systems)

### **Notes**

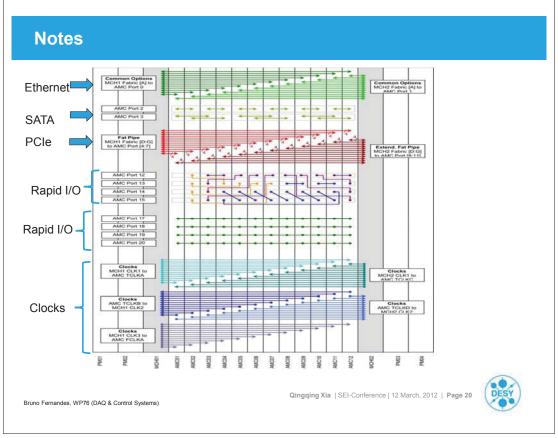

- The MCH is a MicroTCA (uTCA/MTCA) Carrier Hub in the form factor of a single width, mid- or full-size Advanced Mezzanine Card (AMC). It provides the central management and data switching entity for all MicroTCA systems.

- Using the features of AdvancedMC, MicroTCA provides high performance and high availability in one system. MicroTCA has the advantages and technology of AdvancedTCA but in a small form factor. This new technology is used in multiple industries with many different applications. In general, every application of AdvancedMC modules is also possible with MicroTCA modules. Schroff will supply development tools, standard applications and customised systems to further develop this new technology.

- Advanced Mezzanine Cards are printed circuit boards (PCBs) that follow a specification of the PCI Industrial Computers Manufacturers Group (PICMG), with more than 100 companies participating. Known as AdvancedMC

- MicroTCA (auch: μTCA) stand for Micro Telecommunications Computing Architecture

- HUB(1): IPMI(I2C) Interface connected to every other AMC Modules, so that information(sensor, temperature,...) can be downloaded to HUB and it everthing is fine, HUB will allow PM to supply power to that AMC

- HUB(2): Forward connection between different AMC with PCIe, because no straight connection between two AMC's Pcie interface.

- Hard disk(AMC01) → SATA interface & I2C

- Graphic card → PCIe& I2C

- Processor card → PCIe to Graphic Card and DAMC2, SATA interface to Hard disk, and I2C

- Processor card to HUB, HUB to Graphic Card/DAMC2(PCIe) → Processor to Graphic Card/DAMC2(PCIe)

- 8000Euro for crate, HUB, CPU, Graphic Card, Hard disk, PM

- carte: 2500-3000Euro

Bruno Fernandes, WP76 (DAQ & Control Systems)

Qingqing Xia | SEI-Conference | 12 March, 2012 | Page 23

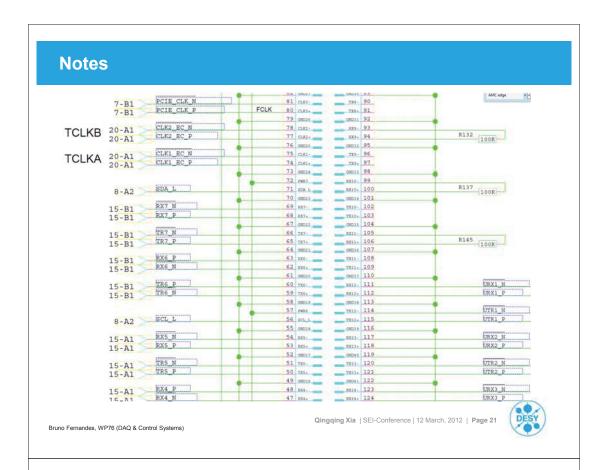

### **Notes**

- Hard disk: Telum 200-SATA is a Serial ATA (SATA) hard disk drive AdvancedMC (AMC), 200GB

- Graphic Card:Telum™ 3001 is a high-quality graphics adapter AdvancedMC that incorporates a high-performance graphics processing unit (GPU). Integrating x8 PCI-Express (PCI-E) and 128 MB memory in a single package, allows the GPU to deliver exceptional 2D, 3D and multimedia graphics performance.

- Telum NPA-5854 is an intelligent high-performance IP packet processor AdvancedMC (AMC) based on the Cavium OCTEON Plus multi-core CN5850-SCP processor.

- Advanced Mezzanine Cards are printed circuit boards (PCBs) that follow a <u>specification</u> of the <u>PCI</u> Industrial Computers Manufacturers Group (PICMG)

- RTM Connector: Advanced CA Zone 2 Z-PACK HM-Zd High Speed Signal Connectors Front Board

Intel® CoreTM 2 Duo L7400 processor, 1.5 GHz core clock, 4 MByte L2 cache

- Single width, full-size or mid-size AMC.0, R2.0 form factor

- · AMC.0, R2.0 Hot Swap compliant

- Up to 4 GByte DDR2 SDRAM with ECC in main memory (2 banks of soldered components)

Qingqing Xia | SEI-Conference | 12 March, 2012 | Page 24

DESY

#### Hardware for Modular High-Speed DAQ Systems

- MicroTCA system for Physics (MTCA.4)

- MTCA.4: http://www.picmg.org/v2internal/resourcepage2.cfm?id=5

- MCH: MicroTCA Carrier HUB; AMC: Advanced Mezzanine Card

- Set-Up in our laboratory

#### Hardware for Modular High-Speed DAQ Systems

> MicroTCA system for Physics (MTCA.4)

### **Hardware for Modular High-Speed DAQ Systems**

- > MicroTCA system for Physics (MTCA.4)

- MTCA.4: http://www.picmg.org/v2internal/resourcepage2.cfm?id=5

- MCH: MicroTCA Carrier HUB; AMC: Advanced Mezzanine Card

- Set-Up in our laboratory

# Überlegungen zur Einführung von TANGO im Jülich Centre for Neutron Science

06.03.12 | Harald Kleines

#### **Einführung**

JÜLICH FORSCHUNGSZENTRUM

Neutronenleiterhalle des FRMII

- ZEL entwickelt die Kontroll- und Datenerfassungssysteme für die Neutroneninstrumente des Jülich Centre for Neutron Science (JCNS)

- 11 Instrumente an den 3 Außenstellen (FRMII, ILL, SNS) des JCNS

- homogene Systemarchitektur: "Jülich-Münchener Standard"

- Instrument-Software basiert auf dem "Kontrollsystem" TACO\* (ESRF)

- Wechsel zum Nachfolgesystem TANGO\*\*??

- sehr aufwendig

- Langjährige Koexistenz

- Situation FRMII und ESS?

\*TACO: <u>Telescope</u> and <u>Accelerator</u> <u>Controlled with Objects</u>

\*\*TANGO: <u>TA</u>co <u>N</u>ext <u>G</u>eneration <u>O</u>bjects

#### Steuerungs- und DAQ-Software für Neutroneninstrumente

- Aufgaben: "Slow Control" + Datenerfassung + Experimentsteuerung

- Typisch: verteilte Client/Server-Architekturen mit standardisierter Middleware, Bedienung über Skripte, teilweise auch mit GUIs

- Beispiele:

- ILL: MAD, NOMAD (basiert auf CORBA)

- NIST: ICP

- SNS: pyDas mit python/Windows, HFIR: "noname" mit Labview/Windows

- HZB: CARESS (basiert auf CORBA)

- Tendenz der letzten Jahre: Verwende standardisiertes Kontrollsystem (insbesondere auch in der Synchrotronstreuung)

- FRJ2 (TACO), FRMII (TACO)

#### Kontrollsysteme: Terminologie

- HMI-Systeme

- Beispiele: ProTool, WinCC Flexible,...

- Entwicklungsumgebungen für Bedienpanels

- SCADA-Systeme (Supervisory Control and Data Acquisition)

- Beispiele: Wonderware InTouch, Siemens WinCC,....

- Graphische Editoren f

ür Pozessbilder, Skripting

- Datenbanken für Konfiguration, Alarme und Prozessdaten

- "Variablen-zentriertes" Modell

- DCS (Distributed Control Systems)

- Beispiele: Siemens PCS7, EPICS,...

- Beinhalten auch Frontend-Systeme für Steuerungsaufgaben

- Verteilte Systeme

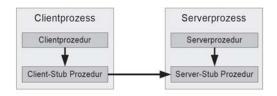

#### **Verteilte Systeme**

- Middleware:

- Softwarschicht zwischen HW + OS und Applikation

- Unterstützung der Verteilung

- Plattform-übergreifend

- Beispiele: .NET, DCOM, SOAP

- RPC

- Objekt-orientiertes Analogon: Java RMI

- Ist sprachabhängig!!!

IDL

#### **CORBA (Common Object Request Broker Architecture)**

- Von der OMG standardisiertes objektorientiertes Middlewaresystem

- IDL (Interface Definition Language)

- Beschreibung der Server-Schnittstelle

- Übersetzung in C++, JAVA,.....

- 3-Tier: ORB

- Protokoll: IIOP (via TCP)

- Adressen: IOR

- Alternativen

- ZeroC ICE

- Facebook Thrift

- ØMQ

- •

IDL

Object Request

#### Trends bei industriellen Kontrollsystemen

- Stark Windows-basiert (ActiveX, .Net, VB-Skripting, OPC)

- Verteilte Client/Server-Architekturen mit Redundanz

- 3-Tier Modell

JÜLICH

#### Situation bei Kontrollsystemen in der Forschung

- Getrieben durch Beschleuniger

- Industrielle SCADA-Systeme meist nur f

ür Subsysteme

- Ausnahme: CERN mit PVSSII

- Nordamerika: Dominierend ist EPICS, wg. Druck des DOE

- Veraltet, Datenbank und Prozessvisualisierung heterogen

- Asien: proprietäre Systeme, EPICS, industrielle Systeme (Yokogawa,..)

- Europa: sehr vielfältig

- DESY: TINE, DOOCS, TANGO, EPICS

- CERN: FESA, UNICOS(PVSSII) für LHC-Beschleuniger; JCOP (PVSSII) für LHC-Experimente

- FAIR: FESA für Beschleuniger, EPICS für PANDA

- ITER: Entscheidung zwischen TANGO und EPICS zugunsten von EPICS

#### **Situation im JCNS**

- TACO (ESRF, ca. 1990): Tool für Entwicklung von Kontrollsystemen

- Verteilte Client-Server-Architektur (Sun-RPC)

- Geräteabstraktion

- dev\_putget(dev,cmd,argin,argin\_type,argout,argout\_type,error)

- Name-service: Taco Manager => Ortstransparenz

- Datenbank: dbm (+mysql)

- TACO-Konfiguration + Parameter

- Probleme bei Multithreading

- Rudimentäre Implementierung von Asynchronität (Events,...)

### JÜLICH

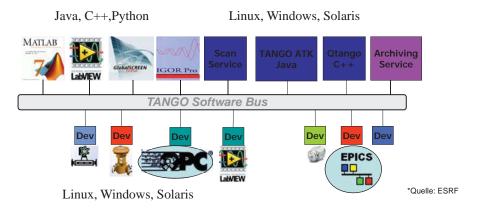

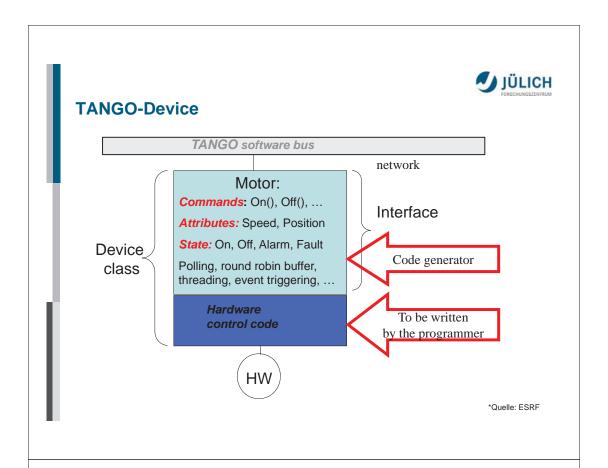

#### **TANGO**

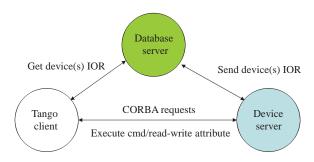

- Objektorientierter Nachfolger von TACO (Entwicklung durch ESRF seit 2001)

- CORBA-basiertes Toolkit für die Entwicklung von Kontrollsystemen

- Modell: "Software-Bus" für verteilte Objekte

- Definiert standardisierte Schnittstelle zu Geräten (Devices)

#### **TANGO Device**

- Device state

- 14 vordefiniert Zustände (ON, OFF, FAULT, STANDBY, UNKNOWN....)

- Endliche Automaten erlauben zustandsabhängige Operationen auf Geräten

- Attribute: Lesen und Schreiben von physikalischen Werten

- Wert, Status, Zeitstempel, Dimension

- Kommandos: Auslösen von Aktionen auf dem Gerät

- Ein generischer Aufruf

#### out = dev.command\_inout("Cmd name",in);

- 20 verschiedene Datentypen

- Jedes device besitzt automatisch 2 Kommandos DevState and DevStatus

- Abfrage der verfügbaren Kommandos

dev.command\_list\_query()

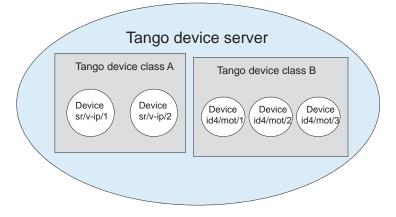

#### **Device Server**

Server ist Prozess auf Betriebssystemebene, multithreaded

\*Quelle: ESRF

#### **Polling und Events**

- Polling Thread in jedem Server füllt Round-Robin Buffer

- Polling Buffer f

ür Kommandos und Attribute

- Client kann vom Gerät oder aus dem Polling Buffer lesen

- => Data Caching

- Alternativ: Events

- Polling Thread erkennt Event-Bedingung (Werteänderung,....)

- Aufruf von Corba-Methode omniNotify zur Benachrichtigung

- Aufruf von Callback im Client

#### **TANGO Datenbank**

- Datenbank: mySQL oder Oracle

- Konfiguration

- Parametrierung

- Archive

\*Quelle: ESRF

#### **TANGO Archive**

- HDB (History Data Base)

- Langzeitarchiv für Prozessdaten

- Abtast-Intervall ≥ 10s

- Unbegrenzt

- TDB (Temporary Data Base)

- Kurzzeitarchiv für Prozessdaten

- Abtast-Intervall ≥ 100 ms

- Maximal 3 Tage

- Snap (Snapshot Data Base)

- Schnappschüsse, die wieder eingespielt werden können??

#### **Tango Tools**

- Astor/Starter: Administration des Systems (Starten, Stoppen,...)

- Pogo: Graphischer Editor zur Generierung von Server-Code

- Jive: Gaphischer Browser für die Datenbank und Test-Tool für Devices

- LogViewer: Graphisches Display für Log-Nachrichten

- JDraw: Graphischer Editor f

ür Prozessbilder (JAVA)

- Canone: Grapischer Editor für Prozessbilder (Web)

- DeviceTree: Graphische Applikation Konfiguration von Device-Attributen und zum Ausführen von Device-Kommandos

- Diverse Tools f

ür die Archive HDB, TDB und Snap

- E-Giga: Datendisplay für Webbrowser

#### **Status**

- Open Source

- Zusätzlich kann über MOU der Status eines Committers oder Contributers erworben werden

- Wird aktiv weiterentwickelt

- Unterstützte Sprachen

|        | C++ | Java | Python | Matlab | LabView | IgorPro |

|--------|-----|------|--------|--------|---------|---------|

| Client | OK  | OK   | OK     | OK     | OK      | OK      |

| Server | OK  | OK   | OK     |        |         | *       |

- Unterstützte Betriebssysteme

- Windows 98 / 2000 / XP, Solaris 7/9, div. releases von Suse, ReadHat, Debian und Ubuntu

\*Quelle: ESRF

#### Motivation für die Einführung von TANGO

- Konsistente Objektorientierung

- Beseitigung von Defiziten von TACO

- Multi-threading

- Event-Mechanismus

- Fehlendes Data-Caching

- •

- Funktionalitäts-Erweiterungen

- Logging/Alarm-System, Graphischer Editor für Prozessbilder, Archive,....

- Migrationsunterstützung

- Aktive Kollaboration: Elettra, Alba, Soleil, DESY, MAX-lab, TUM

- Modernisierung, Verbesserung des Supports, neue Funktionalitäten, Fit werden für die ESS!!!

#### Migration der JCNS-Instrumente zu TANGO

- Vorarbeiten

- Installation, Server-Entwicklung/Test

- Test von omniORB (CORBA ORB)

- Bachelor-Arbeit (Analyse der TANGO-Funktionalität und –Performance, Implementierung Motorserver)

- Exemplarische Migration eines Instruments

- Kleinwinkelstreuanlage KWS3

- Test von Performance und Stabilität

- Ziel: User sollte zunächst keine Unterschiede sehen

- Zeitrahmen: bis zum Beginn des nächsten Reaktor-Zyklus (Mitte April)

- Danach: "go/not go" Entscheidung und Entwicklung eines Zeitplans

- Abstimmung mit der TUM erfolgt kontinuierlich

# EtherCAT Feldbusknoten: Entwicklung, Systemunterstützung und -kompatibilität

Peter Kaever, Helmholtz-Zentrum Dresden-Rossendorf; März 2012

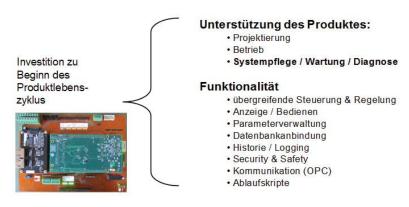

Abstract: Die Verwendung selbst entwickelter Feldbusknoten und deren Einbindung in kommerzielle Automatisierungssysteme erfordert in der frühen Phase des Produktlebenszyklus einen erhöhten Entwicklungsaufwand. Nach erfolgreicher Integration bieten Hersteller von Automatisierungssystemen eine langfristig stabile und leistungsfähige Umgebung zur Projektierung und Programmierung von Anlagen, welche langfristig den Aufwand zur Pflege minimiert. Zur Überprüfung der Funktionsfähigkeit des Gesamtsystems ist die durch Testwerkzeuge unterstützte Systemkompatibilität eine entscheidende Voraussetzung. Die Vorgehensweise bei der Systemintegration eines Slave Device und der Prüfung der Systemkompatibilität wird im Folgenden vorgestellt.

Die Verwendung industrieller Automatisierungssysteme ist im Helmholtz-Zentrum Dresden-Rossendorf (HZDR) fester Bestandteil von Anlagen, für den wissenschaftlichen Gerätebau. Mit der Entwicklung Ethernet-basierter Feldbussysteme [5], [6], [7], [8] bietet sich die Möglichkeit, leistungsfähige Geräte für spezialisierte Funktionen zu entwickeln. Hierzu wurde ein EtherCAT Slave Device mit unterschiedlichen analogen und digitalen Schnittstellen entwickelt und dessen Systemkompatibilität über das Testwerkzeug der EtherCAT Technology Group validiert.

Im HZDR wurden Steuerungslösungen auf Basis industrieller Leitsysteme und Komponenten in einer Vielzahl von Anlagen unterschiedlicher Größe realisiert. Beispielsweise wurde die umfangreiche Automatisierungsinfrastruktur des Beschleunigers ELBE mit mehreren zehntausend I/O-Punkten unter Verwendung eines industriellen SPS-Systems aufgebaut. Die Realisierung der Flüssigmetallanlage LIMMCAST oder der Steuerung für das Hochfeldlabor erforderten gleichfalls sichere und nicht sichere Komponenten, bei denen der Einsatz industriell erprobter und zertifizierter Systeme einen großen Realisierungsvorteil im Bezug auf rasche Umsetzung und langfristige Unterstützung bot.

Bild 1: Motivation zur Entwicklung spezialisierter Feldbusknoten

In vielen Forschungseinrichtungen liegt der Schwerpunkt der Entwicklungstätigkeit auf der Bereitstellung der spezifischen Funktionalität. Berücksichtigt man die Langlebigkeit der Experimente und die Notwendigkeit, nachträglich Funktionalität zu erweitern, so ergibt sich auch im wissenschaftlichen Umfeld die Notwendigkeit zum effizienten Einsatz von Ressourcen. Eine

Gesamtbetrachtung des Aufwands zeigt sich auch hier, dass der Aufwand für Integration und Wartung der Anlagen erheblich ist.

Bei systemkonformer Realisierung spezifischer Gerätefunktionen kann, beginnend mit der Projektierung über den Betrieb bis zu Systempflege mit Wartung und Diagnose, der komplette Lebenszyklus des Gerätes unterstützt werden. Die Überprüfung der Systemkonformität stellt somit einen wesentlichen Aspekt der Entwicklung von Feldbusgeräten dar.

Naturgemäß konnte im HZDR das künftige Einsatzgebiet derartiger Feldbusgeräte bei einer ersten Abschätzung von Einsatzmöglichkeiten nicht eingegrenzt werden. Im Umfeld eines Forschungszentrums gibt es Anwendungen, die aufgrund der schnell ablaufenden Prozesse auch kurze Buszyklen erfordern. Andere Anwendungen stellen hohe Anforderungen an die zeitliche Genauigkeit bzw. an den die Obergrenze des Jitters beim Ausgeben von Signalen. Daher erschien es wünschenswert, Feldbusknoten zu entwickeln, die im Falle von EtherCAT statt im Modus "Sync Manager" zur Minimierung des Jitters auch mit "Distributed Clock" betrieben werden können. Schnelle Applikationen erfordern es, Buszyklen <= 200 µs zu nutzen.

Die Entwicklung von Feldbusknoten für EtherCAT ist auf unterschiedlichen Wegen möglich. Kommerziell verfügbare Module erlauben eine raschere Realisierung der Funktionalität innerhalb eines vorgegebenen Rahmens. Der Zeitgewinn wird durch Verzicht auf die Beeinflussung der oben erwähnten Kommunikationsdetails wie Aktualisierungsrate und der Verwendung unterschiedlicher Buszyklen erkauft. Anders als einige am Markt verfügbare Fertigmodule ist der im HZDR entwickelte Feldbusknoten parametrierbar und in der Lage, auch in Systemen mit schnellen oder synchronisierten Buszugriffen zu arbeiten und bietet so die erforderliche Flexibilität für den Einsatz im wissenschaftlichen Gerätebau.

Anhand der Entwicklung dieses EtherCAT Slave Device werden im Folgenden die wichtigsten Schritte bei der Implementierung beschrieben.

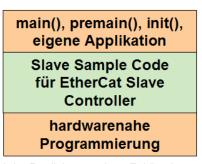

Zunächst sind bei der Adaptierung von Software an einen neuen Controller durch Anpassung von Byte-Order und Alignment bzw. dem Packen von Datenstrukturen im Falle von Feldbusknoten zusätzliche Funktionen zu implementieren. Wichtig sind hier der Datenverkehr zum Feldbus sowie die Definition der Prozessdatenobjekte und Datenstrukturen für asynchronen Datenverkehr. Das Abbild der Prozessdatenobjekte auf die Peripherie des Mikrocontrollers ist neben der Einhaltung der zeitlichen Randbedingungen durch die Interruptserviceroutine eines Timers ein weiterer funktionaler Bestandteil. Da die Kommunikation mit dem Feldbus innerhalb eines zeitlich festgelegten Rasters erfolgen muss, wird auch diese in einer Interruptserviceroutine durchgeführt.

Bild 2: Anpassungsbedarf bei der Realisierung eines Feldbusknotens

Daraus folgt die in Bild 2 veranschaulichte Notwendigkeit, den Slave Sample Code für einen EtherCAT Feldbusknoten mit hardwarenahen Funktionen und solchen Funktionen zu ergänzen, die hier der Applikationsschicht zugeordnet sind. Bei Veränderung des Slave Sample Codes sind ggf. Änderungen in allen Teilen des Programms vorzunehmen.

Innerhalb der ersten Realisierungsstufe wurde in [1] auf einem ARM9 Mikrocontroller die Übertragung der Prozessdatenobjekte die Integration in eine SPS-Steuerung implementiert und

somit die prinzipielle Funktionsfähigkeit gezeigt. Bis März 2011 wurde auch die Einbindung auf einen OPC –Server zum Austausch der Prozessdaten realisiert. Auf Basis dieser Ergebnisse konnte die Entscheidung für eine weitergehende Implementierung getroffen werden. Diese beinhaltet vor allem die Fähigkeit zur asynchronen Übertragung von Strukturinformationen des Data Dictionary über die Mailbox und eine Absicherung der Systemkompatibilität durch das Conformance Test Tool.

Für eine Realisierung von EtherCAT Slave Devices sind der Zugang zu detaillierten Spezifikationen und die Verfügbarkeit des Slave Sample Code wichtige Voraussetzungen. Durch die Mitgliedschaft in der EtherCAT Technology Group wird der Zugang hierzu freigegeben. Ausgehend vom Slave Sample Code V4i30 wurde für das hier realisierte Device eine erste Implementierung durchgeführt und auf einen ARM9 [1], [2] portiert. Im Zuge der Aktualisierung des Slave Sample Code auf V4i42 im März 2011 wurde diese Realisierung in allen Ebenen von Bild 2 angepasst. Eine Realisierung mit Hilfe des zur Zeit neuesten Release des Slave Sample Code Vi50 vom November 2011 wurde bislang noch nicht durchgeführt.

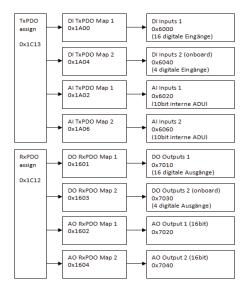

Unterstützend werden Workshops [9],[10] zur Vermittlung der Technologie und Terminologie angeboten, auf denen vor allem die verschiedenen Komponenten und deren Zusammenspiel im System erläutert werden. Naturgemäß bilden Komponenten, welche eine Beschreibung des Verhaltens beinhalten oder an der Kommunikation beteiligt sind, die Basis für das Verständnis und sind zentrale Elemente der Schulung. Neben dem System Manager gehören hierzu die FMMU sowie die Komponenten des EtherCAT Slave Controllers EProm, SyncManager und der Slave Sample Code mit der State Machine. Dies bietet eine gute Basis zur Implementierung des Austauschs von Prozessdatenobjekten. Mailbox-Datenverkehr ist zur asynchronen Übertragung von Strukturinformation des Data Dictionary, wie er beispielsweise in Bild 3 zu sehen ist, erforderlich und wird erst für eine Implementierung mit erweitertem Funktionsumfang von Interesse. Detaillierte Informationen hierzu können abgefragt werden; sie sind als solche aber kein zentraler Bestandteil des Workshops.

Bild 3 Beispielhaftes Data Dictionary für ein EtherCAT Device des HZDR

An die CANopen Spezifikation angelehnt stellt CANopen over EtherCAT Kommunikationsmechanismen zur Verfügung, wie sie von CANopen her bekannt sind. Damit werden Objektverzeichnis (Data Dictionary), Prozessdatenobjekte und Servicedatenobjekte transferiert. Mit Hilfe der Mailbox wird beispielsweise der Datenaustausch von

Servicedatenobjekten realisiert, der von verschiedenen EtherCAT Mastern zum Auslesen der Struktur des Data Dictionary genutzt wird.

Die Parametrierung von EtherCAT Devices lässt sich über den azyklischen Mailbox-Datenaustausch günstig verwirklichen. Da es möglich ist, die Parametrierung auf sinnvolle Device-Zustände einzuschränken und zudem ein zyklischer Austausch von Parametern unnötig Bandbreite benötigt, bietet dieser Datenaustausch einen sicheren und effizienten Realisierungsweg.

Wie bereits erwähnt ist die Absicherung der Systemkonformität ein wesentlicher Schritt bei der Entwicklung von Feldbusknoten. Nur bei konformer Realisierung lässt sich die beabsichtigt Nutzung der Funktionalität des Herstellereigenen Automatisierungssystems absichern. Im Falle von EtherCAT Slave Devices ist die Prüfung der Systemkonformität mit Hilfe des sogenannten Conformance Test Tools bei jedem Device-Hersteller hausintern durchführbar. Das Conformance Test Tool unterliegt ebenfalls der Systempflege und Weiterentwicklung und wurde während der am HZDR laufenden Entwicklung von V1.20.52 im Februar auf V1.20.62 aktualisiert.

Das Conformance Test Tool unterzieht das zu testende Gerät einem Black-Box-Test ohne die Notwendigkeit oder Möglichkeit einer Anpassung auf die spezifische Struktur der implementierten Prozessein- und –ausgangsgrößen. Das Hauptaugenmerk liegt auf einer Überprüfung der systemseitigen Schnittstellen in Bild 4. Hierzu wurden von der EtherCAT Technology Group über 9000 verschiedene Testcases implementiert, welche die Beschreibung des Feldbusknotens prüfen oder Telegramme an diesen versenden und mit erwarteten Antworten vergleichen.

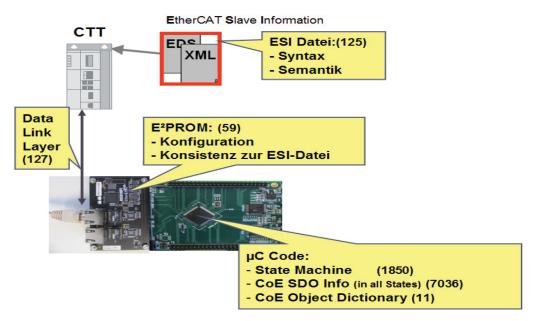

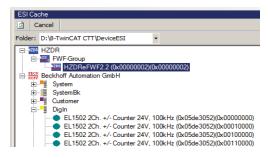

Im ersten Schritt werden zur Identifikation der Geräte die Beschreibungsdateien der Geräte eingelesen (ESI = Electronic Slave Information). Diese werden nach Prüfen der Syntax und wichtiger Teile der Semantik im Cache der ESI-Dateien abgelegt und angezeigt. Ca. 125 Testcases entfallen auf diese Prüfung; etwa weitere 127 auf die Prüfung des in der ESI angegebenen Kommunikationskanals zum EtherCAT Device (Data Link Layer).

#### Conformance Test Tool => CTT Tests

Bild 4: Anwendung des Conformance Test Tool

Im E²Prom sind wichtige Informationen zur Identität des Gerätes (Vendor ID, Product Code, Revision Number, ggf. Serial Number) und zur Adressierung der Kommunikationskanäle für synchronen und asynchronen Datentransfer hinterlegt. Diese werden ausgelesen und mit den Angaben der zugehörigen ESI-Datei im ESI-Cache verglichen.

Mit Hilfe dieser Zuordnung kann zunächst der Zustandsautomat des EtherCAT Device überprüft werden. Die hohe Anzahl der Testcases (1850) belegt die Sorgfalt, mit der an dieser Stelle auf Konformität geachtet wird. Falls CANopen over EtherCAT implementiert ist, wird eine Reihe von Prüfungen durchgeführt, welche Schreib- und Lesezugriffe auf Servicedatenobjekte in den unterschiedlichen Zuständen veranlassen. Abschließend erfolgen einige Zugriffe auf das Obiektverzeichnis.

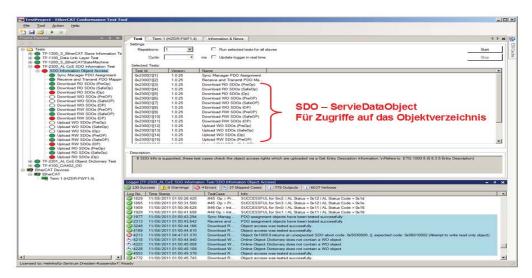

Beim ersten Testlauf unter Verwendung des Conformance Test Tool wurde bei unserer Implementierung ein Fehler während des Herunterladens eines Servicedatenobjektes festgestellt. Auch bei guter Gliederung und detaillierter Angabe von Randbedingungen des Testcase im Conformance Test Tool kann die Auswertung von Black Box Tests und die Beseitigung von Fehlern schwierig sein, da eine weitere Detaillierung von Informationen naturgemäß nicht möglich ist. In dem in Bild 5 gezeigten Fall kam es unter bestimmten Randbedingungen zur zeitlich nicht korrekten Bearbeitung von Interruptserviceroutinen.

Bild 5: Einsatz des Conformance Test Tool bei einem fehlerhaften Slave Device

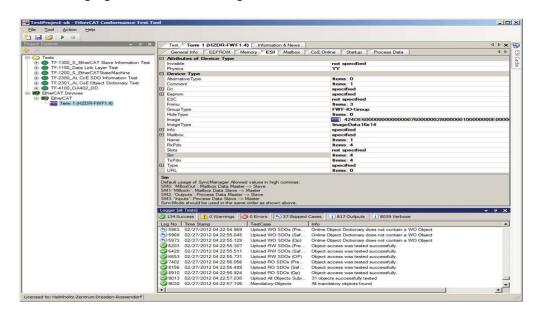

Nach Korrektur dieses Fehlers wurden alle Testcases erfolgreich durchlaufen. Das Conformance Test Tool erlaubt darüber hinaus auch die Überprüfung einer Reihe für die Entwicklung wichtiger Informationen. Bild 6 zeigt in dessen Hauptfenster neben den links angeordneten Testcases rechts eine Reihe von Karteikarten, die unterschiedliche Aspekte des Slave Device zeigen. Diese reichen von Inhalten des E²Prom über Inhalte der ESI-Datei, den Mailboxadressen sowie deren Länge und Möglichkeiten zur Anzeige von CANover EtherCAT Kommunikation und Prozessdaten.

Bei der Entwicklung des Slave Device war neben der Realisierung von Interrupt Service Routinen eine weitere Hürde beim Erstellen einer korrekten ESI Datei zu nehmen. Die Dokumentation [4] zur Beschreibung der ESI-Datei enthält auf 92 Seiten eine Fülle von Informationen, wie die einzelnen Teile der ESI-Datei aufgebaut sind. Diese Spezifikation detailliert in der Art eines Nachschlagewerkes oder einer Prüfvorschrift die einzelnen Elemente, kann aber aufgrund der Fülle möglicher Geräte keine vollständige Implementierungsempfehlung für Einzelgeräte geben.

Bei vorliegender Gerätebeschreibungsdatei ist deren Prüfung anhand der Spezifikation möglich, aber in unserem Falle bei einer Länge von etwa 900 Zeilen zeitraubend. Fehler bei der Erstellung

führten zeitweise zur Instabilität der Testumgebung, welches erst nach Löschen von Konfigurationsdateien wieder funktionsfähig war.

Zur Prüfung einer ESI-Datei und des EtherCAT Slave Device stellt das Conformance Test Tool eine wertvolle Hilfe dar. Nebenbei sei erwähnt, dass die EtherCAT Technology Group für die Inverkehrbringung von Geräten einen erfolgreich bestandenen Test vorschreibt.

Bild 6: Informationen im Conformance Test Tool

Anhand eines Vergleiches mit Geräten von Beckhoff war eine rasche Anpassung zur Darstellung von Slave Devices des HZDR in der ESI Datei möglich. Diese ist in Bild 7 zu sehen.

Bild 7: Hierarchische Anordnung von HZDR Feldbusknoten im Conformance Test Tool

Mit Erstellung einer funktionsfähigen ESI-Datei wurde die Entwicklung des Feldbusknotens zunächst abgeschlossen, da hiermit alle wesentlichen Kriterien für einen erfolgreichen Einsatz erfüllt waren:

- Registrierung des Gerätes mit Vendor-Id, Product Code, Revision Number

- Zyklischer Transfer der Prozeßdaten in verschiedenen Zugriffsmodi

- Azyklischer Transfer von Mailboxdaten, z.B. zum Auslesen des Objektverzeichnisses

- Einbinden in OPC Server

- Einbinden in SPS Steuerung mit TwinCAT PLC Control

Offen bleibt die Anbindung an andere EtherCAT Master um Anwendern einen leichteren Zugang zur Programmierung zu ermöglichen. Wichtig sind insbesondere die Kopplung zu LabVIEW zur graphischen Programmierung und die Anbindung an den Kithara Master Monitor zur alternativen Verwendung unter Windows. Hier besteht zur Zeit noch Klärungsbedarf, da diese EtherCAT Master unsere Geräte nicht verwenden konnten.

Abschließend sei bemerkt, dass im aktuellen Feldbusknoten die Ankunft von EtherCAT-Frames zur Übertragung der Prozessdaten und der Timer-Interrupt die einzigen Ereignisse im Microcontroller sind. Komplexere Verarbeitungsfunktonen und ggf. darüber hinausgehende Funktionalität zur Übertragung von Massendaten sollen unter Beibehaltung einer klaren internen Strukturierung durch ein Betriebssystem implementiert werden.

Am Helmholtz-Zentrum Dresden-Rossendorf werden aktuell auch Profinet Geräte entwickelt. Siemens bietet ERTEC-Chips zur Realisierung von Profinet Devices an, die intern einen ARM9 verwenden und bis zu Profinet IRT [6] einsetzbar sind. Eine bestehende freie Portierung von ECOS für diesen ARM9 motiviert dessen Auswahl als Betriebssystem auch für EtherCAT Slave Devices. Die Anbindung eines Ethernet-Anschlusses ist dabei in ECOS bereits vorgesehen und erlaubt perspektivisch die Übertragung von Massendaten auf einem separaten Kanal.

Auf diese Weise ist unter Nutzung gleichartiger Module die Realisierung von Feldbusknoten für EtherCAT und Profinet möglich, was den Entwicklungs- und Pflegeaufwand minimiert.

#### Ouellen:

- [1] **Meyer, M.** Aufbau eines EtherCAT-Slave mit Beckhoff ASIC und Integration in TwinCAT; Beleg zum praktischen Studiensemester Fachbereich Elektrotechnik der Hochschule für Technik und Wirtschaft Dresden (FH); 4.3.2011

- [2] Kaever, P. EtherCAT for Science Entwicklung von Feldbusknoten für den wissenschaftlichen Gerätebau; 102. Tagung der Studiengruppe elektronische Instrumentierung im Frühjahr 2011 DESY-PROC-2011-02 ISBN 978-3-935702-58-4

- [3] **Beckhoff Automation GmbH**: *Hardware Data Sheet ET1100 EtherCAT Slave Controller*. www.beckhoff.com

- [4] Beckhoff Automation GmbH: ETG2000\_S\_R\_V1i0i2\_EtherCATSlaveInformationSpecification.pdf

- [5] **EtherCAT Technology Group**: *EtherCAT Slave Information Specification*. Mai 2009. www.ethercat.org

- [6] **Siemens** Profinet IRT www.automation.siemens.com/mcms/automation/de/industrielle-kommunikation/profine

- [7] **B&R** Ethernet Powerlink www.br-automation.com

- [8] **Rockwell** EtherNet/IP<sup>TM</sup> www.ab.rockwellautomation.com/Networks-and-Communications/Ethernet-IP-Network

- [9] **EtherCAT** Seminar: EtherCat Technology Basics for Developers

- [10] **EtherCAT** Evaluation Kit Workshop (Hardware & Software)

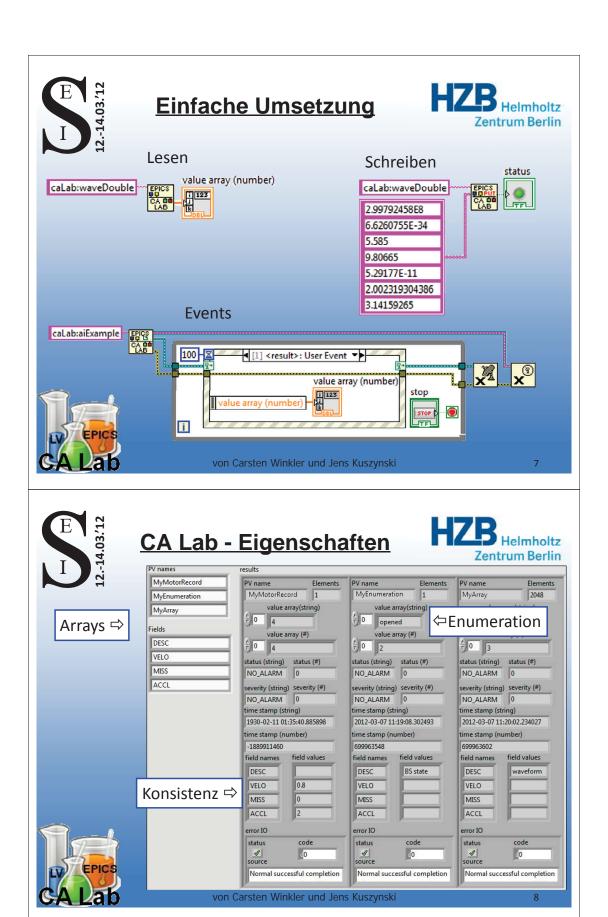

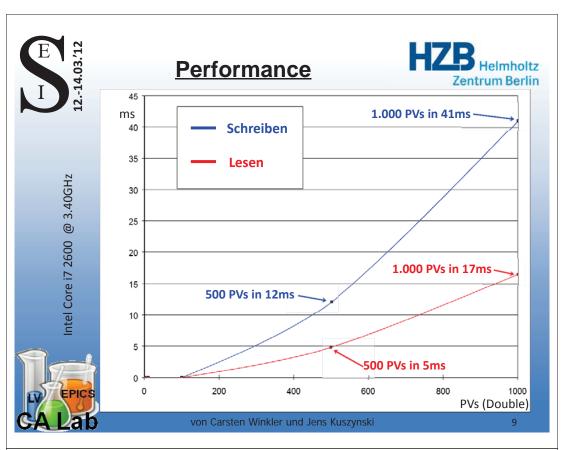

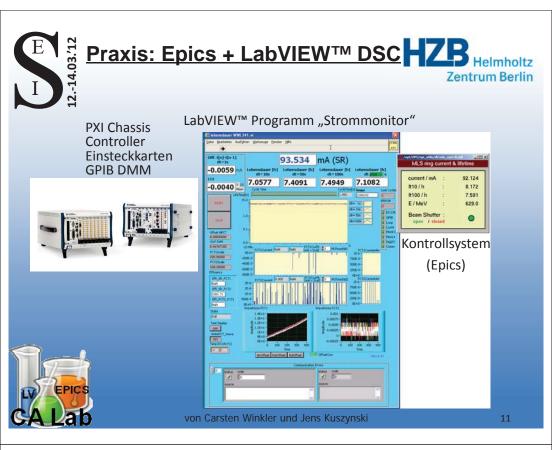

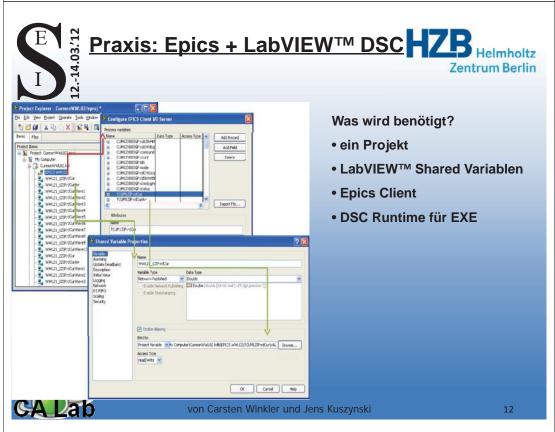

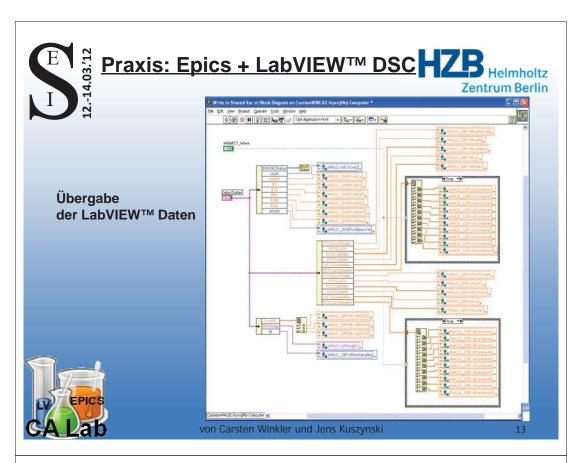

### **Motivation**

- Gastwissenschaftler nutzen LabVIEW™

- Beamline z.T. via EPICS steuerbar

- Betriebsstatusinformationen via EPICS

- Unkomplizierte EPICS-Schnittstelle aus LabVIEW™ gesucht

- Ohne Zusatzkosten

von Carsten Winkler und Jens Kuszynski

2

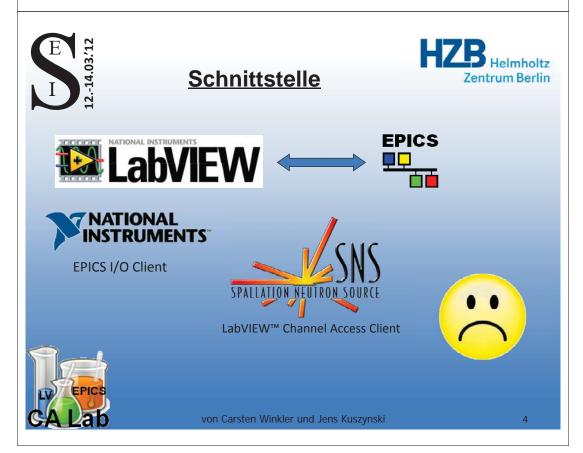

#### **Auftretende Probleme**

Bisherige Lösungen haben alle einen Haken

- Abhängigkeit von externen Services

- Fehlerträchtig für Neueinsteiger

- Kostenlose Schnittstellen sind unvollständig implementiert (Datentypen, Datenfelder, Enumerations)

von Carsten Winkler und Jens Kuszynski

\_

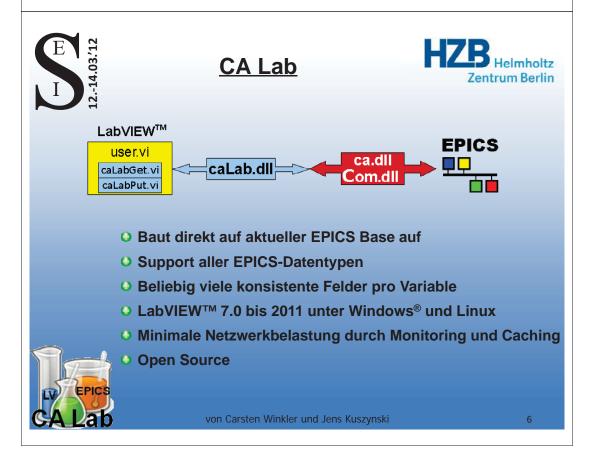

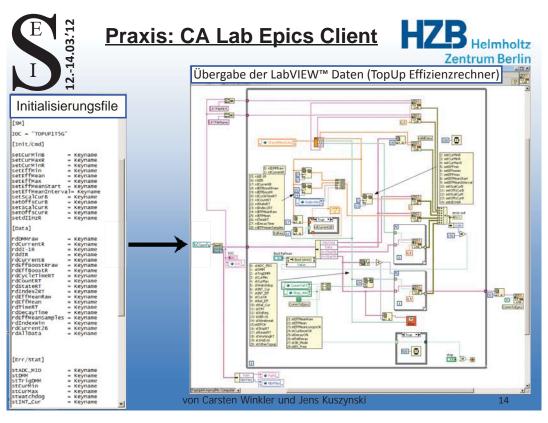

# CA Lab Vorteile gegenüber DSC aus Anwendersicht

- Keine zusätzlichen Kosten durch DSC (und Runtime)

- Einfachere Handhabung während der Programmentwicklung

- Klonen bzw. Überführen der Programme auf andere Rechner ist einfacher, da meist nur die (ASCII-) Initialisierungsdatei angepasst werden muss

- Eigenschaften der Epics PVs werden besser unterstützt

#### Nachteil:

LabVIEW™ RealTime wird zur Zeit nicht unterstützt (ein einfacher Epics Client und Epics Server ist im RealTime Modul enthalten)

http://tinyurl.com/calab2012

von Carsten Winkler und Jens Kuszynski

15

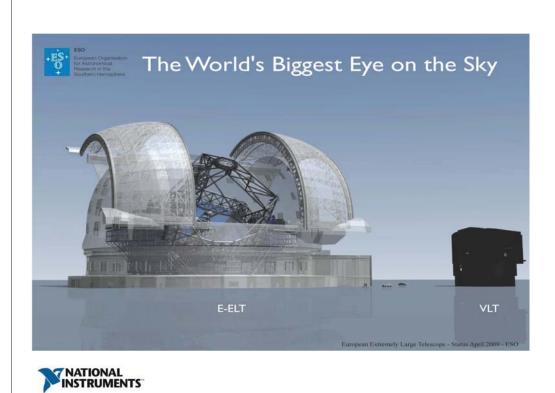

# Customized Off-The-Shelf Technologies for building system platforms for Big Physics experiments

**Leif Johansson** – European Segment Manager Big Physics

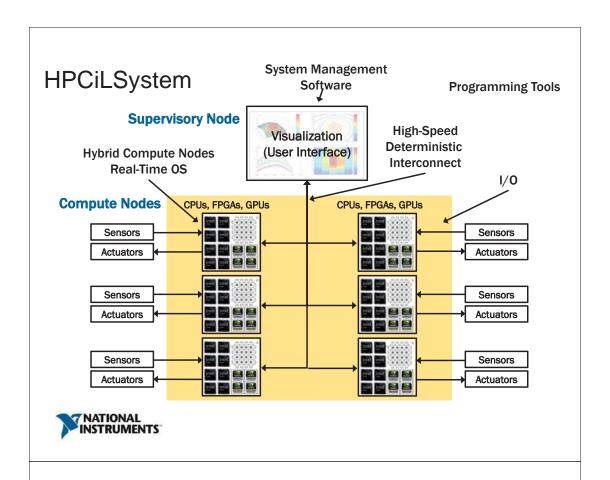

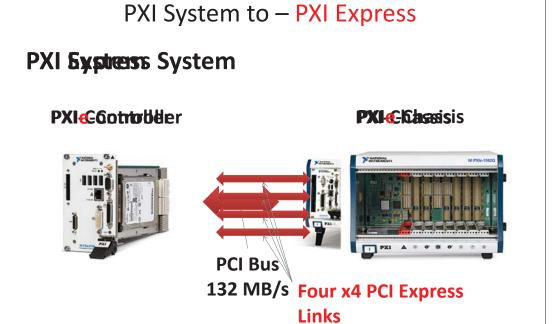

# Science Big Physics System

ITER - Plasma Diagnostics & Control

ESO Extremely Large Telescope - Mirror Control

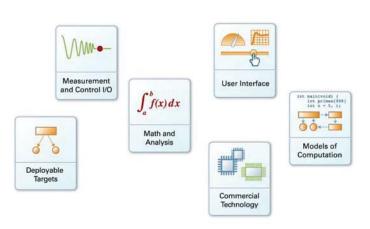

## Today's Engineering Challenges

- Doing more with less

- Time to experiment

- · Managing global projects

- Adapting to evolving application requirements

- Delivering on increasingly complex initiatives

- Maximizing operational efficiency

- Protecting system and resource investments

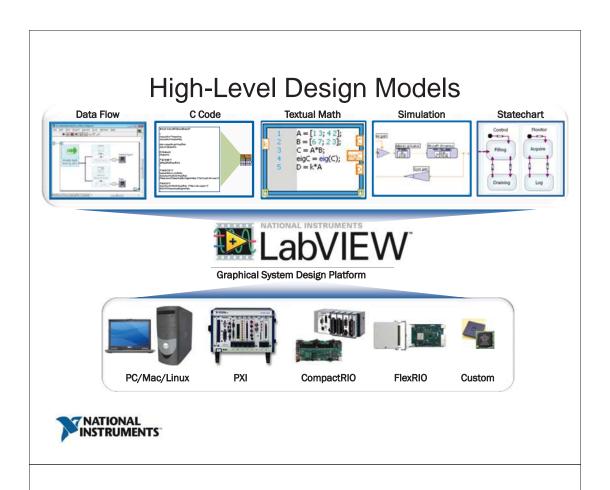

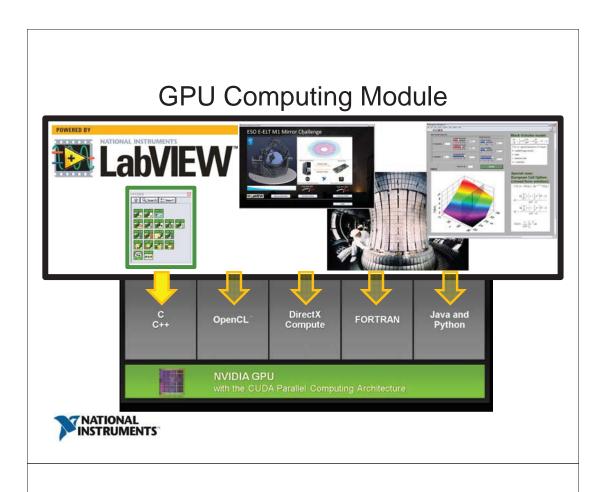

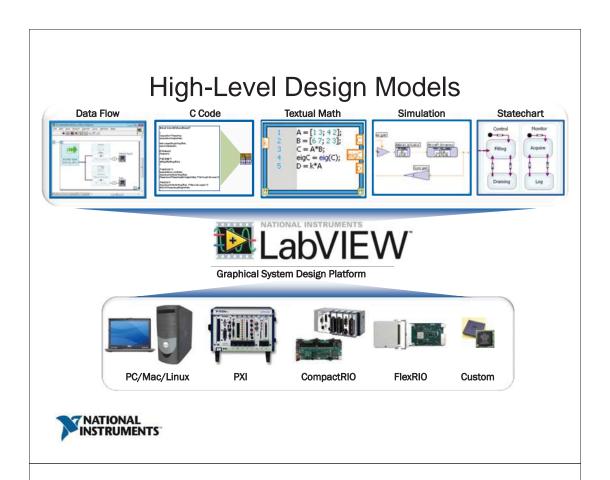

## The National Instruments Vision, Evolved... Graphical System Design

Measurement

Diagnostics

Data Acquisition

Reconfigurable

Instruments

Real-time Measurements Embedded Monitoring Hardware-in-the-loop Industrial Embedded

Industrial Control (PAC)

Machine Control

Electronic Devices

Code Generation

"To do for test and measurement what the spreadsheet did for financial analysis." "To do for embedded what the PC did for the desktop."

# **Open Architecture**

- Controls standards

- EPICS, TANGO, CORBA, TINE, C

- Connectivity to different devices

- OPC, Modbus, TCP/IP, UDP, EtherCAT, Serial

- Flexibility

- Windows, Linux, RTOS, FPGA

# OFF-THE-SHELF TECHNOLOGIES LEVERAGING INDUSTRY

# Leveraging Industry Relationships

- Apply technologies from wide array XILINX of vendors

- Next generation FPGAs, ADCs, GPUs and processors

- **ANALOG**DEVICES

- High access to information

- Regular executive meetings

- Ability to influence roadmaps

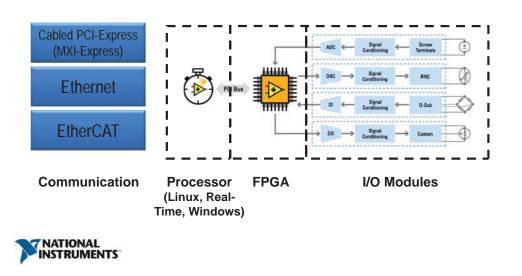

# Putting it together.....

Embedded Controller (Processor)

Chassis with T&S (Communication Bus)

I/O Modules (ADC/DAC)

NATIONAL INSTRUMENTS 4 GB/s bidirectional

# Ongoing project NI and CERN White Rabbit

- Partnering with CERN in developing White Rabbit (WR)

- Performance

- Distance: > 10 kmScale: > 2000 nodes

- Accuracy: < 1ns skew, < 100 ps jitter</li>

- Compensates for propagation delay (cable length, temperature variation, etc.)

- Leverage Industry standards (802.x, IEEE 1588, SyncE)

- Gigabit Ethernet communication with deterministic capability

- Generally Applicable

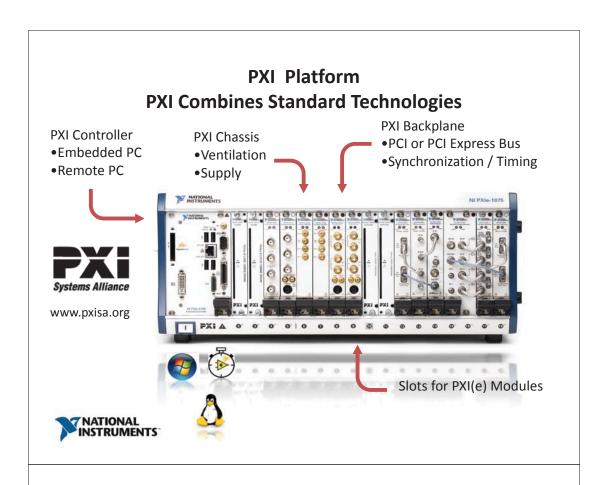

- Leverage for future PXIe modules

### White Rabbit: Synchronization over Distance

# The Next Step PXI Multi-Controller (PXImc)

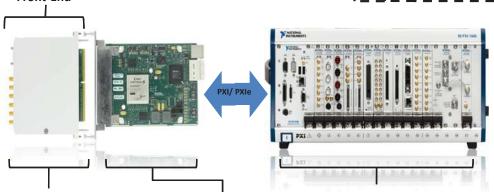

# FPGA on PXI

**NI FlexRIO Architecture**

Customizable Front-End

#### NI FlexRIO Adapter Module

- Interchangeable I/O

- Digital or analog

- NI FlexRIO Adapter Module Development Kit (MDK)

#### NI FlexRIO FPGA Module

- Virtex-5 FPGA

- 132 digital I/O lines • Up to 512 MB of DRAM

- Peer-to-peer data streaming

#### **PXIe Platform**

- Data transfer

- Synchronization

- Clocking/triggersPower/cooling

# **Integrating Elements**

# Combining COTS With Your Design: *RIO Architecture*

# Benefits of FPGAs

- Massively parallel

- Reconfigurable

- Digital signal processing

- ♦ High-speed control

- Faster time to experiment

- Typically require digital design expertise

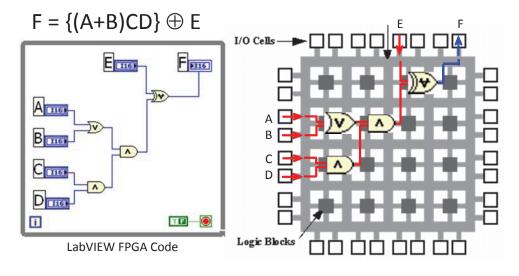

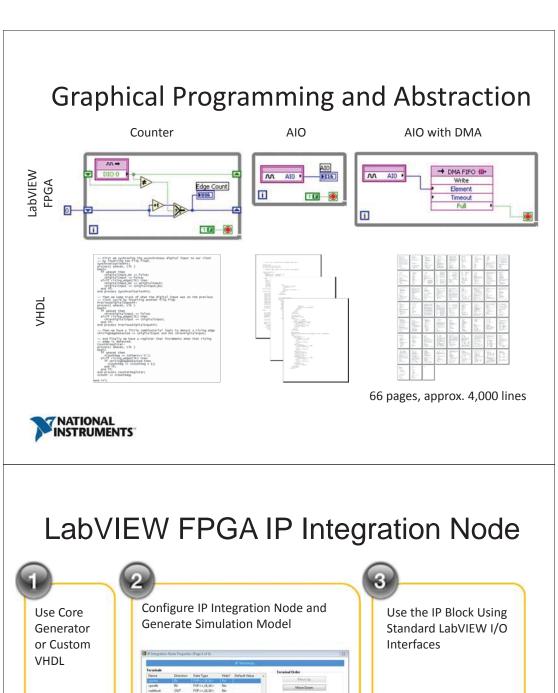

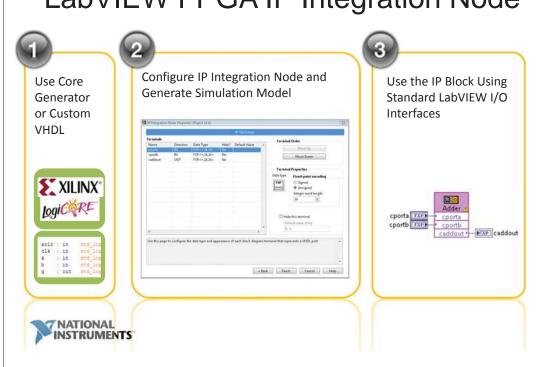

# FPGAs are Dataflow Systems

Implementing logic

# **Customized Off-The-Shelf Technologies**

## systerra computer

#### **Engineering & Consulting**

- Beratung

- Machbarkeitsstudien

- Systemdesign

- Prototypenbau

#### systerra computer GmbH

Kreuzberger Ring 22 65205 Wiesbaden T: 0611 9748-470 E: info@systerra.de www.systerra.de

#### **Systemintegration**

- Europas größtes embedded Produktspektrum

- OEM-Dienstleistungen

- Technische Dokumentation

#### Vertriebsbüros:

- Hannover

- Jena

- München

#### Life-Cycle-Management

- Revisionsüberwachung

- Ersatzteilversorgung

- Reparatur

- Nachproduktion

#### Qualitätssicherung

- ISO 9001:2008 zertifiziert

- 8D Reporting

www.systerra.de

## 4 kompakte Formfaktoren – 5 Basiskonfigurationen

#### Standalone Applikationen

#### UEILogger

Auf PC konfigurierte Anwendung läuft standalone

#### UEIPAC

► Embedded I/O Anwendung läuft standalone unter LINUX auf Cube/Rack

#### UEISIM

Mit Simulink/HIL erzeugte Anwendung läuft standalone auf Cube/Rack

#### **Host basierte Applikationen**

#### PowerDNA

► Datenerfassungs-Anwendung läuft auf Host Computer

#### UEIModbus

► Modbus TCP I/O-Anwendung läuft auf Host Computer

## www.systerra.de

**UEI DAQ-Lösungen**

## **PowerDNA Cube Architektur**

#### Eigenschaften:

- Zwei Baugrößen: 3 oder 6 I/O Steckplätze

- PowerPC 8347@400 MHz, 128 MB RAM

- Dual Gigabit Ethernet, Dual USB 2.0

- SD-Karten Steckplatz

- Serieller Diagnose-Port

- SYNC Port (Karte zu Karte und Cube zu Cube)

- 9-36 VDC Speisung

- Low Power (ab 15 Watt), AC/DC-Betrieb

- Anbindung: 100 m via Ethernet, 20 km via LWL

www.systerra.de

## **PowerDNA Cube Features**

#### Eigenschaften:

- Kompakt: 102 x 102 x 153 mm

- Hohe Kanaldichte mit bis zu :

- ▶ 150 A/D, 192 D/A, 288 DIO,

- ▶ 48 seriellen Schnittstellen

- ▶ 72 ARINC-429

- Extrem Robust:

- ▶ -40...+85°C Umgebungstemperatur

- ▶ 5g Vibration, 50g Schock

- ► MTBF > 34 Jahre

- ▶ 21.300 m Betriebshöhe

- ► Strahlungsgetestet für Raumfahrtanwendungen

CPU- und I/O-Karten werden als "Stack" in das Cube-Chassis eingebaut.

www.systerra.de

**UEI DAQ-Lösungen**

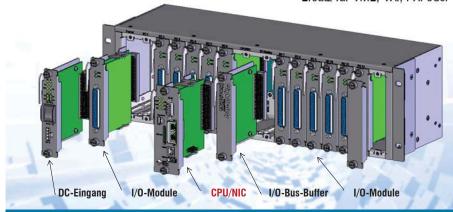

# **RACKTangle und Half-RACK**

**DNR-6-1G**

#### Eigenschaften:

- Basiert auf bewährter Technik der Cubes

- 6 oder 12 I/O Steckplätze

- Passive Backplane

- Temperaturgeregelte Lüfter

- CPU/NIC Karte mit GigE Cube identisch

- 19" Einbau möglich

www.systerra.de

## **RACKTangle Features**

#### Eigenschaften

- 3HE Aluminium Chassis:

- Geringe Masse: 12-Slot Chassis ~2,3 kg

- Dual Gigabit Ethernet, Dual USB 2.0

- PowerPC 8347@400 MHz, 128 MB RAM

- Hohe Kanaldichte mit bis zu:

- ▶ 300 Als, 384 AOs, 576 DIOs

- ▶ 144 ARINC 429 Kanälen

- ▶ 96 seriellen Ports

- MTBF = 130,000 h

- Ersatz für VME, VXI, PXI oder SCXI Systeme

www.systerra.de

**UEI DAQ-Lösungen**

## I/O-Module für Cubes und Racks

Cube I/O-Karte

#### Eigenschaften:

- Cube und RACKtangle Systeme haben elektrisch identische I/O Karten

- Unterschiede nur in Busstecker/Montage

- Isolation pro Karte oder Kanal

- Integrierte Signal-Konditionierung

- Softwarekonfigurierbar

- 3 oder 6 I/O-Karten pro Cube und

6 oder 12 I/O-Karten pro RACKtangle Chassis

- Standard DB-37 oder DB-62 Stecker

- Beliebige I/O-Kartenkombinationen möglich

www.systerra.de

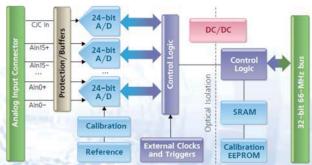

## **Analoge Eingangskarten**

Für die PowerDNA I/O-Cubes und RACKtangle I/O-Chassis gibt es eine breite Auswahl an analogen Eingangskarten:

- Alle Karten sind werksseitig vorkalibriert und verfügen über bis zu 25 Kanäle mit max. 24-bit Auflösung und max. 250 kHz Abtastrate.

- Verfügbare Eingangskartentypen:

- ► Universal Eingänge

- ► Thermoelement Eingänge

- ▶ Dehnungsmesstreifen

- ▶ LVDT/RVDT

- ► ICP/IEPE

- ▶ Synchro/Resolver

- ▶ Simultane Abtastung

- ► Hohe Abtastrate

- ► Hochauflösend

Beispiel: 16-Kanal 24-bit Analog-Eingangskarte

## www.systerra.de

**UEI DAQ-Lösungen**

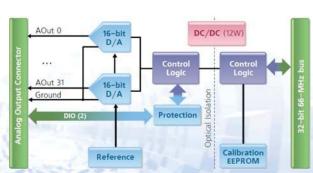

## **Analoge Ausgangskarten**

Analoge Ausgangskarten bieten bis zu 32 Kanäle und sind werksseitig vorkalibriert:

- Es stehen zahlreiche Varianten mit unterschiedlichen Auflösungen und Ausgangsspannungen/Strömen zur Verfügung:

- ▶ ±10 V

- ▶ 4...20 mA

- ► Hohe Ausgangsspannungen

- ► Hohe Ausgangsströme

- ► Externe Pufferverstärker

Beispiel: 32-Kanal 16-bit Analog-Ausgangskarte

www.systerra.de

## Digitale I/O-Karten

Die Palette der digitalen I/O-Karten umfasst neben reinen Ein- und Ausgängen auch intelligente Zähler/Timer und Encoder-Karten:

- Hohe I/O-Dichte

- Industrielle I/O-Pegel

- Hochstrom

- PWM-Ein- und Ausgänge

- Zähler/Timer

- Quadratur Encoder

- LVDT/RVDT

- Synchro/Resolver

- Relais

Beispiel: 24-Kanal Digital-I/O-Karte

## www.systerra.de

**UEI DAQ-Lösungen**

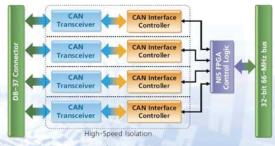

## Serielle I/O-Karten

#### **CANbus Schnittstellen:**

- DNx-CAN Karten sind elektrisch zu on-board Bussystemen von Kraftfahrzeugen kompatibel

- Support durch UEIDAQ Framework-Bibliothek

- Support für alle gängigen Betriebssysteme und Programmiersprachen inkl. LabVIEW/DASYLab

#### Serielle Schnittstellen:

- Asynchrone und synchrone RS-232/422/485 Schnittstellenkarten.

- Im synchronen Betrieb werden SDLC, HDLC und generische Clk/Data Konfigurationen unterstützt

- Asynchron bis zu 4 Mbaud

**Beispiel: 4-Kanal CANbus-Karte**

## www.systerra.de

## **Intelligente I/O-Karten**

**Avionik Schnittstellen**

- AFDX / ARINC664

- MIL-1553, ARINC-429, ARINC-708

**Navigation, Position und Zeit**

- GPS

- IRIG-B Slave oder Master

**Drahtlose Kommunikation**

■ WLAN und GSM Module

#### **FPGA**

"Custom" FPGA Karten

DC/DC Konverterkarten

■ Hilfsenergieerzeugung für Ausgangskarten

**Guardian Serie**

■ Analoge und digitale Ausgänge mit Spannungs-/Stromrücklesefunktion

## www.systerra.de

**UEI DAQ-Lösungen**

### Zubehör

Zum Anschluss von Ein- und Ausgängen, der Signalkonditionierung und der Synchronisation steht eine umfangreiche Zubehörpalette zur Verfügung:

- Anschlussterminals

- Signal- und Datenkabel

- Steckverbinder

- Stromversorgung

- Pufferverstärker

- Synchronisationskarten

- Befestigungs-Kits

www.systerra.de

## **Software Basiskonfigurationen**

#### **Autonome Systeme**

#### **UEI PAC**

- ► Linux-basierte Automationssteuerung

- ► Cube- oder RACKTangle-Bauform

- ▶ Standard Linux 2.6 OS mit Echtzeit-Kern

- ▶ Bis zu 576 KHz Abtastrate

#### UEI Logger

- ▶ Standalone oder Netzwerk-Datalogger

- ► Cube-Bauform

- ▶ Bis zu 1000 Samples/s pro Kanal

#### UEI SIM

- ► Matlab/Simulink RTW-Target-System

- ► Cube- oder RACKTangle-Bauform

- ► Standard Linux 2.6.x Betriebssystem

- ► Target für Matlab/Simulink Entw.-Umgebung

- ▶ Bis zu 5 kHz Abtastrate

#### Host gesteuerte Systeme

#### ■ PowerDNA/DNR

- ▶ Messen, Steuern, Regeln via Ethernet

- ► Cube- oder RACKTangle-Bauform

- ► Echtzeitfähig: < 1 ms Abtastzeit für 1000 I/Os

- ► LabVIEW, MATLAB, DASYLab Support

#### ■ UEI Modbus

- ► Modbus/TCP I/O-Lösung

- ► Cube- oder RACKTangle-Bauform

- Modbus/TCP Interface

## www.systerra.de

**UEI DAQ-Lösungen**

## **Software Architektur**

www.systerra.de

### **PowerDNA Software Suite**

#### Eigenschaften:

- Durchgängige Softwareplattform

- Support für Windows, Linux, RTX, ...

- Keine Lizenzgebühren Open Source

- Quellcode Beispiele für alle Module

- PowerDNA Explorer

- Spectrum Analyzer Software

- I/O-Simulation unter Windows

- Ain, Aout, DIO, Serial, ARINC, 1553

- ► Software kostenlos testen

Kostenloser Download: www.ueidaq.com/download

## www.systerra.de

**UEI DAQ-Lösungen**

# Langzeitverfügbar

UEI garantiert den Nachkauf aller RACKTangle und Cube Produkte für mindestens 10 Jahre!

- Sofern beim Kauf nicht anders ausgewiesen, können alle DNA/DNR Komponenten mindestens 10 Jahre lang nachgekauft werden

- Langfristige Planungssicherheit für Projekte

- Investitionsschutz für Hard- und Software

- Sichere Versorgung mit Ersatzteilen

www.systerra.de

# Messdatenerfassung in schweren Tagebaufahrzeugen

Ein führender Anbieter von Flurförderzeugen setzt den UEI Datalogger zur Überwachung einer Vielzahl an Funktionen in seinen Fahrzeugen ein.

- Die Applikation erfordert einen kompakten, äußerst robusten Datalogger

- Neben analogen und digitalen I/Os werden auch CANbus, RS-232 und GPS-Daten aufgezeichnet

- Die Umsetzung ist mit einem UEILogger 600 mit 16 analogen 18-bit Eingängen, 4 CANbus und 4 RS-232 Ports, 8-Kanal Zähler/Timer, GPS und 24-bit digital Eingangskarten realisiert

- Die Datenaufzeichnung erfolgt mit Zeitstempeln

www.systerra.de

# **MSR-System für Flugsimulatoren**

- In enger Zusammenarbeit zwischen FlightSafety und UEI wurde das RACKTangle System in eine neue Simulatorgeneration integriert

- Geringes Gewicht, schnelle GbE Kommunikation, und hohe I/O-Dichte ermöglichen den Einsatz direkt an der Kabine

- Kurze Kabelwege sparen Gewicht und schützen vor Einstrahlung/Übersprechen

- Der wartungsfreundliche Aufbau spart im langjährigen Betrieb enorme Kosten

Installation direkt in der beweglichen Kabine

www.systerra.de

**UEI DAQ-Lösungen**

## **Onboard In-flight Messdatenerfassungssystem**

Das System sammelt im Flug Daten aus dem neuen Modell 162 SkyCatcher™ und erfüllt dabei alle Anforderungen des Kunden:

- Systemaufbau auf kleinstem Raum

- Geringe Leistungsaufnahme

- Bedienbarkeit im Flug

- Portabilität und flexible Rekonfiguration

- Verarbeitung von ARINC 429 Telegrammen

www.systerra.de

www.systerra.de

## Zusatzfolien

Details zu den Basiskonfigurationen

## **Host-controlled Cube oder RACK**

#### **Features:**

- Standard Netzwerkinterface: (1000BaseT, 100BaseT oder 100BaseFX)

- Hohe Performance: Scan/Update 1000 I/O Messstellen in < 250  $\mu$ S

- Low-Cost: Cubes ab 1000 EUR

- Exzellenter Software Support

- Betriebssystemsupport für Windows, Linux, QNX

- Support für die verbreiteten Programmiersprachen

## **UEIPAC (Programmable Automation Controller)**

#### **Features:**

- Standalone-Betrieb (ohne Host-PC)

- Cube- und Rackbauform

- Open source, Applikationsentwicklung in C auf einem Linux-PC oder Windows PC mit Cygwin Umgebung

- Standard Fedora/Suse Linux 2.6.28 mit Xenomai RT extensions

#### **Anwendungsbeispiele:**

- Maschinenüberwachung

- Regelungstechnik

- Autonome Land-, See- und Luft-Fahrzeuge

- Avionik Testequipment

- Emulation/Ersatz alter I/O Systeme

- Robuste, portable Messsysteme

## www.systerra.de

**UEI DAQ-Lösungen**

## **UEILogger Cube**

# 2068 100

#### Features:

- Einfache Anwendung, keine Programmierung erforderlich

- Programmierung via Ethernet oder Start von SD-Karte

- Speicherung auf 4 GByte SD-Karte

- 1000 Samples/s pro Kanal

- Systempreis ab ~1600 EUR

- Download der Daten über Ethernet, WLAN, GSM oder SD-Karte

- Aufzeichnung von A/D, DI, Serial, CAN und ARINC 429 Daten, ...

- Automatische Konvertierung in SI-Einheiten

- Betrieb als PowerDNA Cube an Host-PC möglich

www.systerra.de

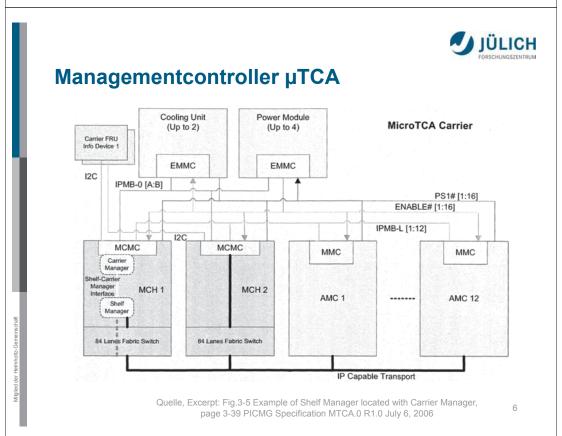

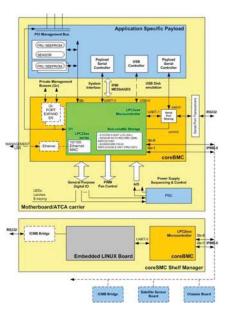

# µTCA Management Aktuelle Entwicklungen im ZEL

SEI Dresden 13. März 2012 | Matthias Drochner & Peter Kämmerling

## **Inhalt**

- ATCA und µTCA

- IPMI

- IPMI-Testsoftware

- MMC und coreIPM

- Entwicklungsarbeiten

led der Helmholtz-Gemeinschaft

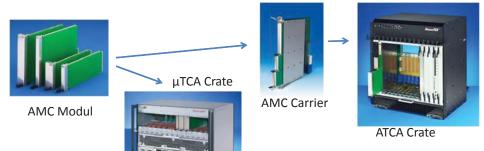

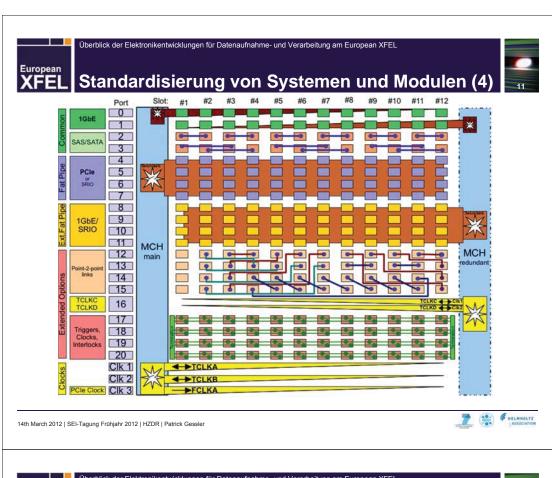

# ATCA und µTCA: kommender Standard für Physik-Instrumente

- Von vielen Labs für Neuentwicklungen favorisiert

- Erlauben den Einsatz moderner serieller Busse: 10Gb/s Ethernet, PCI Express, Serial Rapid IO, Serial ATA

- Für ATCA auch InfiniBand und StarFabric

- Integrierte Fernüberwachung

-

# ATCA und µTCA:

- primär Ersatz für VME

- Signifikant h\u00f6here Bandbreite

- Multiprocessing ist möglich, beschränkt mit PCIe

- Auch Ersatz f

ür compactPCI und serielle Derivate

- wenig industrielles I/O verfügbar

- Steckverbinder sind weniger robust

- nur eine Versorgungsspannung: 12VDC oder 48VDC

- Entwicklungen im ZEL sind für μTCA

Mitglied der Helmholtz-Gemeinscha

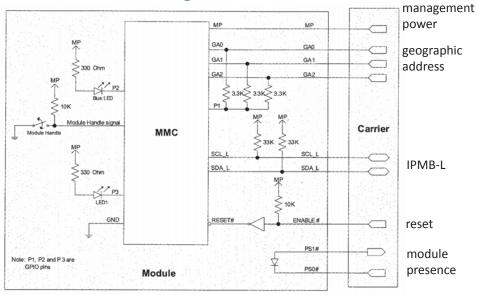

#### IPMI – Intro

- Protokoll zur Fernwartung von PCs von Intel, HP, NEC, Dell

- Modell: Mikrocontroller als Teil des Systems, Verbindungen zu

- Aktoren, Sensoren und Meßwerte wie Spannungen, Temperaturen, Lüfter, Schalter ...

- ROM für "Inventardaten" (FRU); NV-RAM für Protokoll und veränderliche Daten wie Event-Log, SensorData Record

- Kontrolle von außen über LAN, RS232 ...

- Kontrolle durch OS im PC "System Interface": Register, Kommandoblöcke, UART, I2C, SMBus ...

- Kommunikation mit anderen Management-Controllern, Subsysteme oder übergeordnet

- Kommandos "Messages" über mehrere Controller geroutet

7

# **IPMI – Kommandogruppen**

- - Identifikation, Power, Reset

- FRU (Field Replaceable Unit) Inventory: r/w

- SDR (Sensor Data Record) Repository: r/w

- Sensor device: r, ggf. Schwellen & Events

- Events: set Receiver, Event Message

- SEL (System Event Log): r/w/löschen

- Messaging support: send/receive "raw" Message

litglied der Helmholtz-Gemeinschaf

# **IPMI – Transportprotokolle**

- IPMB, Intelligent Platform Management Bus

- I2C-basiert, zwischen Modulen im Crate

- RMCP, Remote Management Control Protocol

- UDP/IP-basiert, f

ür Kontrolle von au

ßen

über LAN

- Durch Paßwort oder cryptographisch schützbar

- Unterstützt "Sessions", d.h. mehrere unabhängige Transaktionen über dasselbe Interface

- Terminal Mode

- UART-basiert als "System Interface"

- Üblich für Verbindungen zur CPU auf µTCA-Processorboards

- Eingeschränkt für Menschen tauglich, weil Hex-kodiert

9

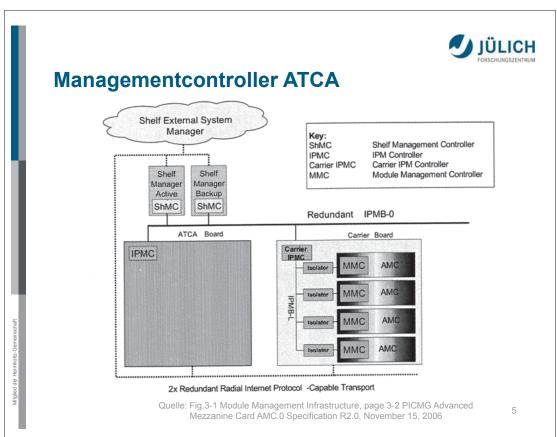

# ATCA & µTCA, relevante Spezifikationen

- IPMI v2.0: 644 S.

- Platform Management

FRU Information Storage Definition v1.0: 33 S.

- ATCA Base 3.0 "PICMG3.0"

- AMC Base 2.0 "AMC.0"

800 Seiten

- µTCA Base 1.0 "MTCA.0"

- Ergänzungen für serielle Protokolle "AMC.1" ... "AMC.4", Physics "MTCA.4"

- HPM.1 Hardware Platform Management

Mitglied der Helmholtz-Gemeinsch

# xTCA-spezifische Einträge im FRU-Inventory

- Verbindungen Punkt-zu-Punkt

- Multidrop für "Physics"

- Slots inclusive Geometrie

- Belegung der Backplane-Verbindungen in den Modulen Protokoll, Channels / Lanes, upstream / downstream fuer PCle

- Ähnlich für Clocks

- Power management: "Channels" von Netzteilen und Verbindungen mit Maximalstrom, Bedarf der Module, Verzögerungen für sequentielles Einschalten

- I2C-Adressen der Komponenten im Crate

- IP-Adresse des Shelf-Managers für Kontrolle von aussen HotSwap-Schalter-Sensor, Events für HotSwap

11

# **IP-Adresse des Shelf-Managers**

- EEPROM mit Adress-FRU-Record an Backplane

- Spezifikation empfiehlt deren Bevorzugung

- Backplanes werden mit 192.168.16.17 oder 0.0.0.0 ausgeliefert; Spezifikation empfiehlt ersteres

- NAT-MCHs erlauben Ignorieren der IP-Adresse der Backplane und die eigene Adresse zu bevorzugen

- Standard ist auf Produktionsumgebungen ausgerichtet mit austauschbaren MCHs