# Development of CMOS Pixel Sensors for High-Precision Vertexing & Tracking Devices

M. Winter (PICSEL team of IPHC-Strasbourg)

- Sensor design : coll. with IRFU-Saclay - (ALICE-MFT) - Ladder design : coll. with DESY - Oxford - Bristol - Tests : coll. with LBNL/STAR - Frankfurt/CBM - CERN-INFN/ALICE - DESY/AIDA

DESY - 3rd May 2012

# Contents

- Reminder: initial motivation & main features of CMOS sensors

- Architecture developped state of the art

\* MIMOSA-26 (EUDET chip applications) \* MIMOSA-28 (STAR-PXL, AIDA)

- Application to an ILC vertex detector

- \* MIMOSA-30 (inner layers) \* MIMOSA-31 (outer layers) \* 2-sided ladders

- On-going R&D and plans until  $2014/15 \Rightarrow$  Milestones !

- \* ALICE-ITS & -MFT \* CBM-MVD \* AIDA \* ILC/CLIC \* SuperB-SVT

- Summary (subatomic physics tracking devices)

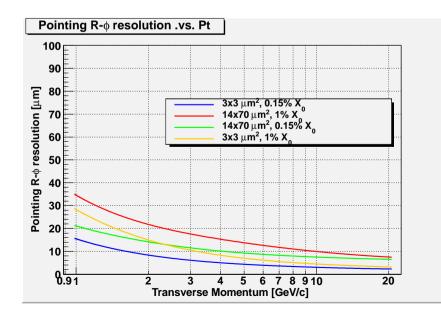

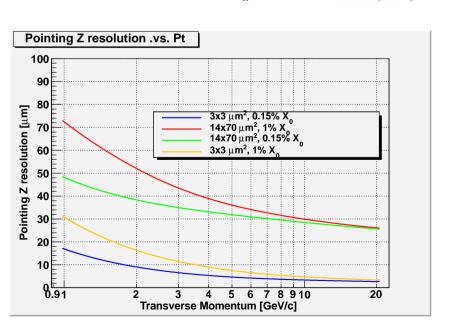

## **ILC Vertexing Performance Goals**

- CMOS PIXEL SENSORS (CPS) devt triggered by ILC vertex detector requirements :

- \* unprecedented granularity & material budget (very low power)

- \* much less demanding running conditions than at LHC

- $\Rightarrow$  alleviated read-out speed & radiation tolerance requests

- Vertexing goal:

- \* achieve high efficiency & purity flavour tagging  $\rightarrow$  charm & tau !!!

- $\hookrightarrow \sigma_{R\phi,Z} \leq 5 \oplus 10/p \cdot \sin^{3/2}\theta \ \mu m \quad \rhd \ \text{LHC:} \ \sigma_{R\phi} \simeq 12 \oplus 70/p \cdot \sin^{3/2}\theta$

- $\triangleright$  Comparison:  $\sigma_{R\phi,Z}$  (ILD) with VXD made of ATLAS-IBL or ILD-VXD pixels:

# **CMOS Pixel Sensors: Main Features**

- Prominent features of CMOS pixel sensors:

- \* high granularity  $\Rightarrow$  excellent (micronic) spatial resolution

- st very thin (signal generated in 10-20  $\mu m$  thin epitaxial layer)

- \* signal processing  $\mu$ -circuits integrated on sensor substrate

- $\Rightarrow$  impact on downstream electronics ( $\Rightarrow$  cost)

- CMOS pixel sensor technology has the highest potential

- ⇒ R&D largely consists in trying to exploit potential at best with accessible industrial processes

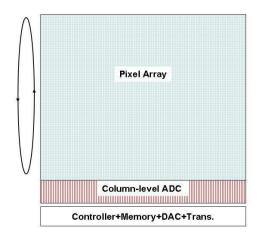

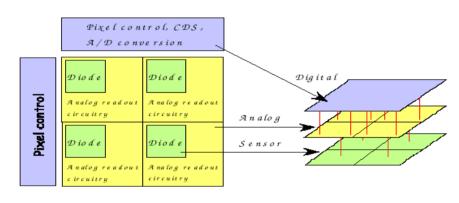

- Organisation of MIMOSA sensors:

- \* manufactured in 0.35  $\mu m$  OPTO process (mainly)

- \* signal sensing and analog processing in pixel array

- \* mixed and digital circuitry integrated in chip periphery

- \* read-out in rolling shutter mode

- (pixels grouped in columns read out in //)

- $\Rightarrow$  impact on power consumption

# **CPS R&D: A Long Path with Numerous Intermediate Steps**

- Main objective: ILC, with staggered performances

- MAPS applied to other experiments with intermediate requirements

<u>ILC >2020</u> Internatinal Linear Collider

**EUDET (R&D for ILC, EU project)** STAR (Heavy Ion physics) **CBM** (Heavy Ion physics) **ILC (Particle physics)** HadronPhysics2 (generic R&D, EU project) AIDA (generic R&D, EU project) FIRST (Hadron therapy) ALICE/LHC (Heavy Ion physics) **EIC (Hadronic physics) CLIC** (Particle physics) SuperB (Particle physics)

STAR 2012 Solenoidal Tracker at RHIC

CBM 2017 Compressed Baryonic Matter

➔ Spinoff: Interdisciplinary Applications, biomedical, space ...

# **CMOS Pixel Sensors: Established Architecture**

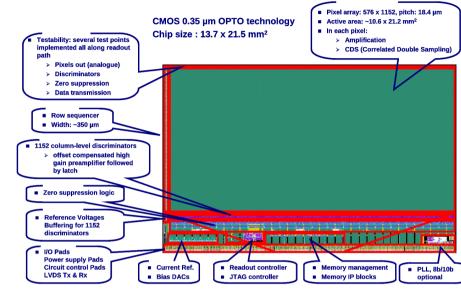

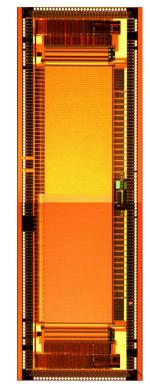

- Main characteristics of MIMOSA-26 sensor equipping EUDET BT:

- \* 0.35  $\mu m$  process with high-resistivity epitaxial layer (coll. with IRFU/Saclay)

- \* column // architecture with in-pixel amplification (cDS) and end-of-column discrimination, followed by  $\emptyset$

- \* binary charge encoding

- \* active area: 1152 columns of 576 pixels (21.2 $\times$ 10.6 mm<sup>2</sup>)

- st pitch: 18.4  $\mu m

ightarrow$   $\sim$  0.7 million pixels

- Dash charge sharing  $\Rightarrow~\sigma_{sp}\sim$  3.-3.5  $\mu m$

- \*  $t_{r.o.} \lesssim 100 \ \mu s$  (~10<sup>4</sup> frames/s) suited to >10<sup>6</sup> part./cm<sup>2</sup>/s

- \* JTAG programmable

- \* rolling shutter architecture

- $\Rightarrow$  full sensitive area dissipation  $\cong$  1 row

- $ho~\sim$  250 mW/cm $^2$  power consumption (fct of N $_{col}$ )

- $\ensuremath{\, \mathrm{ \mbox{ } }}$  thinned to 50  $\ensuremath{\mu m}$

- \* various appli. : VD demonstr., NA63, oncotherapy, dosimetry, ...

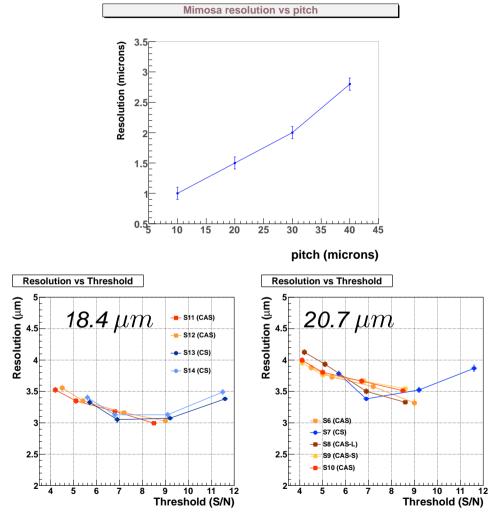

# **Measured Spatial Resolution**

- Compare position of impact on sensor surface predicted with BT to hit reconstructed with sensor under test : clusters reconstructed with eta-function, exploiting charge sharing between pixels

- Impact of pixel pitch (analog output) :  $rac{1}{}$  ho

ho

ho $\sigma_{

m sp} \sim 1 \ \mu m$  (10  $\mu m$  pitch)  $ightarrow \lesssim 3 \ \mu m$  (40  $\mu m$  pitch)

- Impact of charge encoding resolution :

- hinspace ex. of 20  $\mu m$  pitch  $\Rightarrow \sigma^{digi}_{sp}$  = pitch/ $\sqrt{12}$  ~ 5.7  $\mu m$

| Nb of bits    | 12                     | 3-4                  | 1                      |

|---------------|------------------------|----------------------|------------------------|

| Data          | measured               | reprocessed          | measured               |

| $\sigma_{sp}$ | $\lesssim$ 1.5 $\mu m$ | $\lesssim$ 2 $\mu m$ | $\lesssim$ 3.5 $\mu m$ |

$\triangleright \triangleright \triangleright$

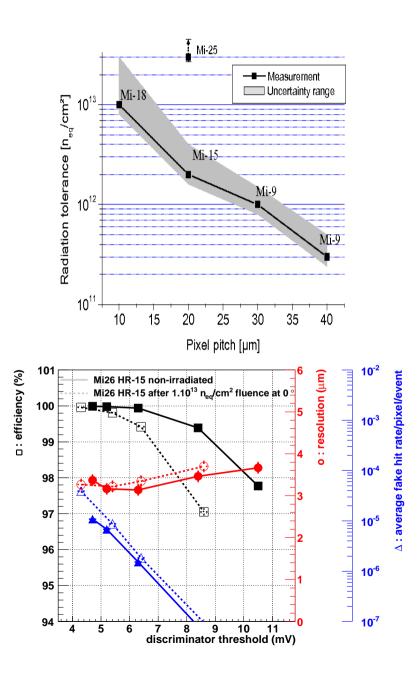

# **Observed Radiation Tolerance**

$\triangleright \triangleright \triangleright$

$\triangleright \triangleright \triangleright$

- Introductory remarks :

- \* still evolving (csq of CMOS industry process param. evolution)

- \* CMOS technology expected to tolerate high ionising radiation doses (>> 10 MRad), in particular at <  $0^{\circ}$ C and short t<sub>integ</sub>

- \* main a priori concern : NON-ionising radiation

(in absence of thick depleted sensitive volume)

• Influence of pixel pitch :

\* fig: all measts done with low resistivity epitaxial layer, but 1

- ⇒ high density sensing diodes (≡ small pitch) improves non-ionising radiation tolerance

- Influence of epitaxial layer resistivity :

\* ex: 1 kΩ · cm & O(1)V depletion voltage

- $\mbox{ * trend : }\gtrsim$  1  $k\Omega\cdot cm$  & >> 10 V

$$\Rightarrow$$

tolerance to  $\gtrsim$  10 $^{14-15}$  n $_{eq}$ /cm $^2$  not excluded

## State-of-the-Art: MIMOSA-28 for the STAR-PXL

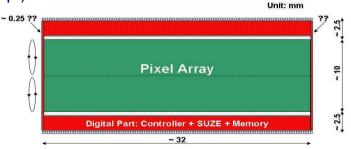

- Main characteristics of ULTIMATE ( $\equiv$  MIMOSA-28):

- \* 0.35  $\mu m$  process with high-resistivity epitaxial layer

- \* column // architecture with in-pixel cDS & amplification

- \* end-of-column discrimination & binary charge encoding

- \* on-chip zero-suppression

- \* active area: 960 colums of 928 pixels (19.9 $\times$ 19.2 mm<sup>2</sup>)

- st pitch: 20.7  $\mu m

ightarrow \sim$  0.9 million pixels

- $\hookrightarrow$  charge sharing  $\Rightarrow$   $\sigma_{sp} \gtrsim$  3.5  $\mu m$

- \* JTAG programmable

- \*  $t_{r.o.} \leq 200 \ \mu s$  (~ 5×10<sup>3</sup> frames/s)  $\Rightarrow$  suited to >10<sup>6</sup> part./cm<sup>2</sup>/s

- \* 2 outputs at 160 MHz

- $st \lesssim$  150 mW/cm $^2$  power consumption

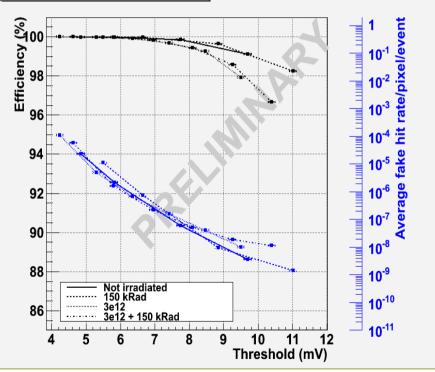

- $\triangleright \triangleright \triangleright$  Sensors fully evaluated : (50  $\mu m$  thin)

- \* N  $\leq$  15 e<sup>-</sup> ENC at 30-35<sup>o</sup>C (as MIMOSA-22AHR)

- \*  $\epsilon_{det}$ , fake &  $\sigma_{sp}$  as expected

- $-\infty$  Rad. tol. validated (3.10<sup>12</sup> n<sub>eq</sub>/cm<sup>2</sup> & 150 kRad at 30°C)

- $-\infty$  All specifications are met  $\Rightarrow$  40 ladders under construction

- **DDD** Start of data taking early 2013

Mimosa 28 - epi 20 um - NC

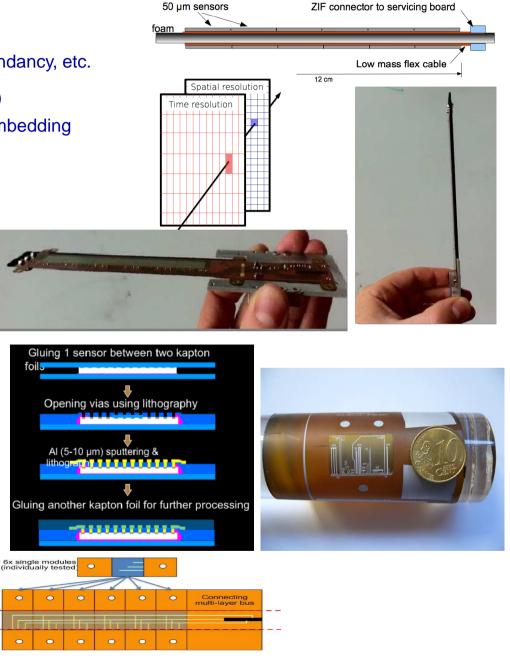

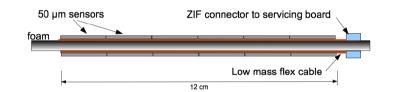

# **Sensor Integration in Ultra Light Devices**

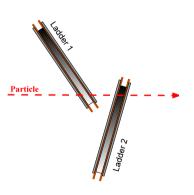

- 2-sided ladders with time stamping for the ILD-VXD :

- \* manyfold bonus expected from 2-sided ladders:

- compactness, alignment, pointing accuracy (shallow angle), redundancy, etc.

- ★ studied by PLUME coll. (Oxford, Bristol, DESY, IPHC) & AIDA (EU)

- Pixelated Ladder using Ultra-light Material Embedding

- \* square pixels for single point resolution on beam side

- \* elongated pixels for 4-5 times shorter r.o. time on other side

- \* correlate hits generated by traversing particles

- $\textit{\texttt{*}}$  expected total material budget  $\sim$  0.3 % X\_{0}

- $\hookrightarrow$  1st proto. (0.6 % X<sub>0</sub>) fabricated & operationnal

- ▷ beam tests at CERN-SPS (traversing m.i.p.) in Nov. '11

- Unsupported ladders (Hadron Physics 2 / FP-7)

- \* 50  $\mu m$  thin CMOS sensors embedded in thin kapton and cabled with redistributed connections  $\rightarrow$  suited to curved surfaces ?

- \* expected total material budget  $\lesssim$  0.15 % X $_0$

- \* 1st single sensor mechanical prototype fabricated

- \* 1st 3-sensor electrical proto. expected by Summer 2012

Final

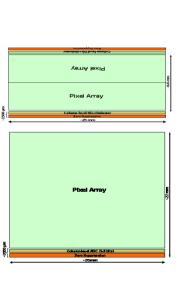

# **CMOS Pixel Sensors for the ILD-VXD**

### • Two types of CMOS Pixel Sensors (CPS):

- ★ Inner layers (≤ 300 cm<sup>2</sup>) : priority to read-out speed & spatial resolution

→ small pixels (16×16 / 80 µm<sup>2</sup>) with binary charge encoding

→ t<sub>r.o.</sub> ~ 50 / 10 µs;  $\sigma_{sp} \leq 3 / 6 µm$ ★ Outer layers (~ 3000 cm<sup>2</sup>) : priority to power consumption and good resolution

- $\hookrightarrow\,$  large pixels (35  $\!\times$  35  $\mu m^2$  ) with 3-4 bits charge encoding

- $\hookrightarrow$  t<sub>r.o.</sub>  $\sim$  100  $\mu s; ~\sigma_{sp}\lesssim$  4  $\mu m$

- \* Total VXD instantaneous/average power < 700/20 W (0.35  $\mu m$  process)

### • 2-sided ladder concept for inner layer :

★ Square pixels (16×16  $\mu m^2$ ) on internal ladder face ( $\sigma_{sp}$  < 3  $\mu m$ ) & Elongated pixels (16×80  $\mu m^2$ ) on external ladder face (t<sub>r.o.</sub> ~ 10  $\mu s$ )

### • Sensor final prototypes : fabricated in Q4/2011

- \* MIMOSA-30: inner layer prototype with 2-sided read-out  $\triangleright$   $\triangleright$   $\triangleright$

- ← one side : 256 pixels (16×16  $\mu m^2$ ) other side : 64 pixels (16×64  $\mu m^2$ )

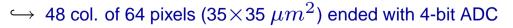

\* MIMOSA-31: outer layer prototype

|>

## **CMOS Pixel Sensors: Status of Baseline Devt**

- MIMOSA-30: prototype for ILD-VXD innermost layer  $\triangleright$   $\triangleright$   $\triangleright$ \* 0.35 CMOS  $\mu m$  process with high-resistivity epitaxy \* in-pixel CDS, rolling shutter read-out, binary sparsified output \* high resolution side : pixels of 16×16  $\mu m^2 \Rightarrow$  expect  $\sigma_{sp} < 3 \,\mu m$ • 128 columns (discri) & 8 col. (analog) of 256 rows (final scale) • read-out time  $\leq$  50  $\mu s$ \* time stamping side : pixels of 16×64  $\mu m^2 \Rightarrow t_{r.o.} \sim$  10  $\mu s$ • (expect  $\sigma_{sp} \sim$  6  $\mu m$ ) • 128 columns (discri) and 8 col. (analog) of 64 rows (final scale) • lab tests positive : N  $\sim$  15 e<sup>-</sup> ENC & discri. all OK for  $t_{r.o.} = 10 \mu s$ \* beam tests (CERN-SPS) in June/July '12  $\Rightarrow \sigma_{sp}, \epsilon_{det}$ , fake rate MIMOSA-31: prototype for ILD-VXD outer layers  $\triangleright$  $\triangleright$

- \* pixels of  $35 \times 35 \ \mu m^2$  (power saving)

- \* 48 columns of 64 pixels ended with 4-bit ADC (1/10 of full scale chip)

$\hookrightarrow$  expect  $\sigma_{sp} \lesssim 3.5 \, \mu m$

- \*  $t_{r.o.} \sim 10 \ \mu s$  (1/10 of complete column)

- \* beam tests (DESY) in Q1/2013  $\Rightarrow \sigma_{sp}, \epsilon_{det}$ , fake rate

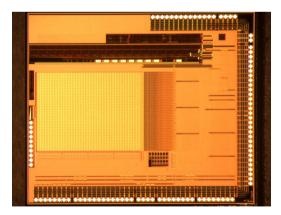

# **2-Sided Ladder Beam Test Results**

### • PLUME prototype-2010 tested at SPS in Nov. 2011:

- \* Beam telescope : 2 arms, each composed of 2 MIMOSA-26 sensors

- \* DUT : 1 PLUME ladder prototype (0.6 %  $X_0$ )

- $\hookrightarrow$  6 MIMOSA-26 sensors on each ladder face (> 8 Mpixels)

- \* CERN-SPS beam :  $\gtrsim$  100 GeV " $\pi^-$  " beam

- st BT (track extrapolation) resolution on DUT  $\sim$  1.8  $\mu m$

- \* Studies with PLUME perpendicular and inclined ( $\sim$  36°) w.r.t. beam line

\* Preliminary results (no pick-up observed): combined impact resolution & pointing resolution

• New PLUME proto. under construction with 0.35 %  $X_0$  (X-sect.)  $\rightarrow$  beam tests in Q4/2012 (SPS ?)

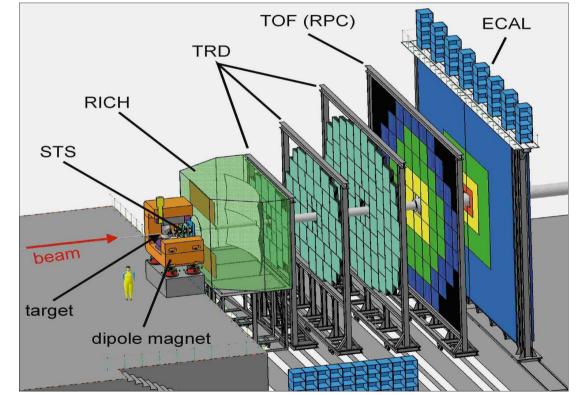

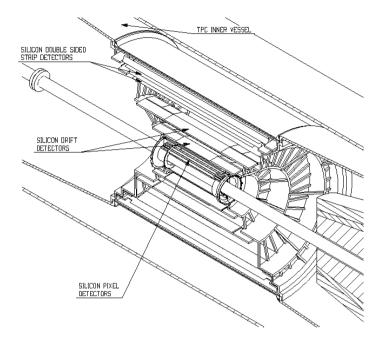

# Applications of CPS : the CBM H.I. Experiment

- Cold Baryonic Matter (CBM) experiment at FAIR/GSI:

- \* Micro-Vertex Detector (MVD) made of 2 or 3 stations located behind fixed target

- \* double-sided stations equipped with CMOS pixel sensors

- \* operation a negative temperature in vacuum

- st each station accounts for  $\lesssim$  0.5 % X $_0$

- \* sensor architecture close to ILC version

- Most demanding requirements :

- \* ultimately ( $\gtrsim$  2020): 3D sensors  $\lesssim$  10  $\mu s, >$  10  $^{14}{\rm n}_{eq}/{\rm cm}^2, \gtrsim$  30 MRad

- \* intermediate steps: 2D sensors  $\lesssim$  30-40  $\mu s$ , > 10 $^{13}$ n $_{eq}$ /cm $^{2}$ ,  $\gtrsim$  3 MRad

- \* 1st sensor for SIS-100 (data taking  $\gtrsim$  2018)

# **Applications of CPS : ALICE-ITS Upgrade**

- ITS upgrade : envisionned for "2017-18" LHC long shutdown

- \* exploits space left by replacement of beam pipe with small radius (19 mm) section

- \* consists (at least) in adding L0 at  $\sim$  22 mm radius (potentially : replace part of the ITS)

- \* 2 main pixel options considered (CDR) :

- ♦ Hybrid pixel sensors with reduced material budget & pitch

- ♦ CPS derived from STAR-PXL (ULTIMATE/MIMO-28)

### • Differences w.r.t. ULTIMATE/M-28 :

\* > 1 MRad & 10<sup>13</sup>n<sub>eq</sub>/cm<sup>2</sup> at T = 30°C (target values)

$\hookrightarrow$  0.18  $\mu m$  triple-well HR-epi techno. (instead of 0.35  $\mu m$  double-well hR-epi)

- $st \sim$  1 imes 3 cm  $^2$  large sensitive area (instead of 2 imes 2 cm  $^2$ )

- st double-sided read-out (instead of single-sided)  $\rightarrowtail$   $\lesssim$  10  $\mu s$

- \* 1 or 2 output pairs at  $\geq$  300 MHz (instead of 1 output pair at 160 MHz)

- \* possibly: 2-sided ladder derived from PLUME (< 0.5 %  $X_0$ )

$rac{1}{2}$  > Conceptual Design Report delivered to LHCC in March 2012 > > > techno. choice  $\leq$  Q1/2013 (?)

#### $\hookrightarrow$ includes Muon Forward Tracker (MFT) based on CPS

# **Read-Out Acceleration**

- Motivations (w.r.t. occupancy) :

- \* required for ALICE-ITS & -MFT and CBM-MVD (and SuperB-SVT)

- \* robustness w.r.t. predicted hit rates (e.g. beam BG)

- $\hookrightarrow$  ILC beam BG ( $\gtrsim$  1 TeV)  $\gtrsim$  3×BG (500 GeV)

- \* standalone inner tracking capability (e.g. soft tracks)

- How to accelerate the elongated pixel read-out

- \* elongated pixel dimensions allow for in-pixel discriminators  $\Rightarrow$  2 faster r.o.  $\triangleright \triangleright$

- \* read out simultaneously 2 or 4 rows  $\Rightarrow$  2-4 faster r.o./side

- \* subdivide pixel area in 4-8 sub-arrays read out in //  $\Rightarrow$  2-4 faster r.o./side

- $\vartriangleright\,$  0.18  $\mu m$  CMOS process needed

- $\hookrightarrow$  6-7 ML, Ion. Rad. tol., design compactness, in-pixel PMOS T, ...

- \* conservative step: 2 discri./column end (22  $\mu m$  wide)

$\Rightarrow$  read out 2 rows simultaneously

$\hookrightarrow$  1st stage improvement: 50/10  $\mu s \rightarrow$  25/5  $\mu s$

(5  $\mu s$  also achievable with 0.35  $\mu m$  technology)

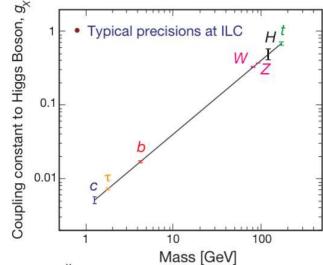

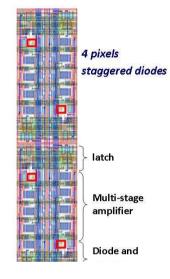

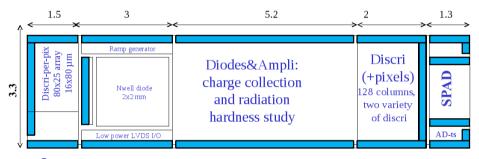

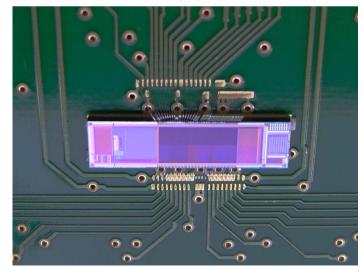

# MIMOSA-32 : Prototyping a 0.18 $\mu m$ Process

- 0.18  $\mu m$  imaging technology options used :

- \* Epitaxial layer: High-Resistivity (1-5  $k\Omega \cdot cm$ ) & "18  $\mu m$ " thick  $\Rightarrow$  SNR, rad. tol., ...

- \* Quadruple well: deep P-type skin embedding N-well hosting P-MOS transistors  $\Rightarrow$  compactness, power, ...

- \* MIM capacitors

- \* start with 4 Metal Layers (6 ML run in 2012 chips)

- ★ etc.

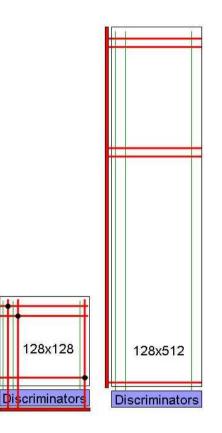

- Prototype sub-divided in several blocks :  $\triangleright \triangleright \triangleright$

- \* Sensing elements and in-pixel amplifiers :

- --> pixel dimensions : 20imes20/40/80  $\mu m^2$

- –o 2 different types of sensing elements : diodes of  $\sim$  9–15  $\mu m^2$

- -- N-MOS and P-MOS transistor based amplifiers

- \* Discriminators :

- -- Col. // pixel array ended with 1 discriminator/col. (2 variants)

- Pixel array with in-pixel discriminator (16imes80  $\mu m^2$  pixels)

- \* Total surface  $\sim$  43  ${\rm mm}^2$

- Mimosa-32 fabricated in Q4/2011  $\Rightarrow$  Laboratory tests since April '12

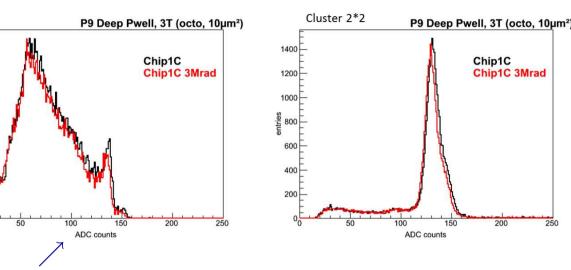

# Preliminary 0.18 $\mu m$ Process Test Results

• MIMOSA-32 lab tests ( $^{55}$ Fe source) of pixel matrix with analog output ightarrow Very preliminary results :

500

400

300

200

100

seed

- \* Observed CCE (20×20  $\mu m^2$  pixels) :

- $\circ$  seed pixel :  $\sim$  40–50 %  $\triangleright$   $\triangleright$   $\triangleright$

- $\circ$  2×2 pixel cluster : nearly 100 %  $\triangleright$   $\triangleright$   $\triangleright$

- $\Rightarrow$  confirms Epi. layer 1-5  $k\Omega \cdot cm$

- No parasitic charge coll. seen with Deep P-well

- $_\circ\,$  CCE of 20imes40  $\mu m^2$  pixels

- $\hookrightarrow\,$  seed  $\sim$  30 % and with 1st crown  $\sim$  75 %

- $\ensuremath{\,\times\,}$  Noise  $\sim$  20 e  $^-$  ENC at 20  $^\circ\text{C}$  , unchanged at 35  $^\circ\text{C}$  (tbc !)

- \* Irradiation: 0.4/1/3 MRad  $\rightarrow \sim$  no effect up to 35°C (tbc !)

- \* Difficult to find operating regime of in-pixel ampli. due to inaccurate simul. **models**  $\Rightarrow$  pixel design optimisation?

- Next steps :

- \* Beam tests of pixel matrix foreseen in June-July 2012 (incl. NI radiation tolerance assessment)

- \* Lab and beam tests of digital matrix through Summer 2012

- \* Lab tests of in-pixel discriminator array in Q3-Q4/2012 (tbc)

- \* MIMOSA-32bis fab. in Spring'12 with standard epitaxial layer  $\rightarrow$  lab tests in Summer 2012

- \* Submission of MIMOSA-32ter (July 2012) with alternative in-pixel amplification schemes

# **MISTRAL: 0.18** $\mu m$ Architecture Prototyping

- 1st Objective : MISTRAL  $\equiv$  Mimosa for the Inner Silicon TRACKER of ALICE

- MIMOSA-22THR (Upstream part of MISTRAL) :

- \* Col. // pixel array with in-pixel ampli + pedestral subtraction (cDS)

- \* Each of 128 columns ended with discriminator + 8 columns without discri.

- \* Pixel array sub-divided in sub-arrays featuring different pixel designs (22×22/44  $\mu m^2$ )

- \* 2 options for July'12 submission :

- $\circ$  end of column discriminator  $\equiv$  translation of MIMOSA-22AHR (0.35 techno.)

- $\circ$  simultaneous 2-row encoding & 2 discriminators/column  $\Rightarrow$  twice faster

- AROM-1 (Accelerated Read-Out Mimosa)

\* in-pixel discri. & simultaneous 4-row encoding  $\Rightarrow$  8 times faster

\* submission in Octobre'12

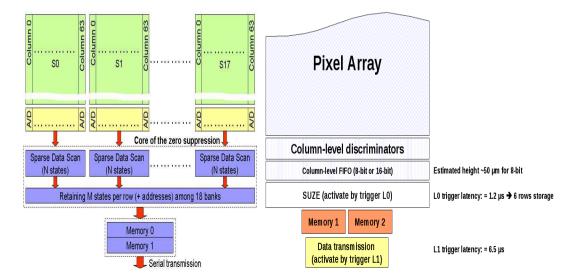

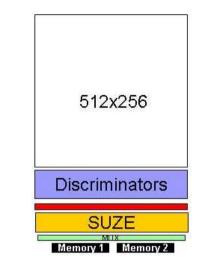

- SUZE-02 (Downstream part of MISTRAL) :

- \* Ø  $\mu$ -circuits & output buffers ( $\equiv$  SUZE-01)

- ★ add trigger L0 info after discriminators for

data filtering ⇒ flow & power reduction

- \* add trigger L1 downstream of output buffers for further filtering  $\Rightarrow$  flow & power

- \* submission in Octobre'12

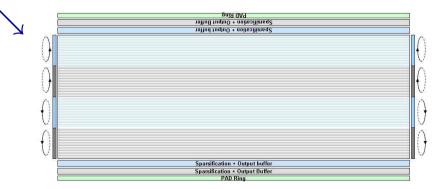

# **MISTRAL : Final Steps**

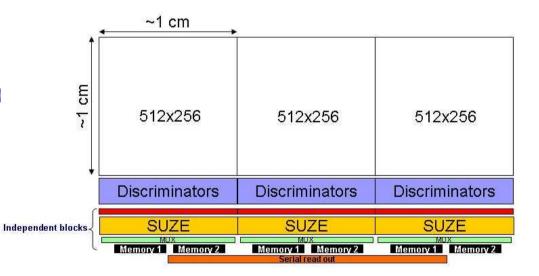

- FSBB (Full Scale Basic Block) :

- \* Composition :

- ightarrow Pixel array with  $\sim$  final pixel design ( $\sim$  1 cm $^2$ )

- $-\infty$  Final r.o. circuitry ( $\emptyset$ , filtering, data transmission, ...)

- → All read-out circuitry split in elementary blocks

according to stitching design rules → AIDA-BT

- \* Submission : Summer 2013 (?)

- MISTRAL :

- \* Composition :

- 3 full-size adjacent FSBB (1-sided read-out)

or 6 half FSBB (2-sided read-out)

- --- Complemented with serial r.o. circuitry

- \* Submission : Summer 2014 (?)

- Start MIMAIDA & MIMOSIS designs (+ others ?) :

- $\hookrightarrow$  submission in 2015

# **AIDA Project : Assessment of Stitching & 2-Sided Ladder**

### • Single Arm Large Area Telescope (SALAT) :

- st 2048imes3072 pixels ( $\sim$  20  $\mu m$  pitch)

- $\Rightarrow$  4×6 cm<sup>2</sup> sensitive area, ~ 3.5  $\mu m$  spatial resolution

- \* requires combining several reticules (based on FSBB)

- $\Rightarrow$  stitching process  $\Rightarrow$  establish proof of principle

- st 2-sided read-out of 1024 rows in  $\sim$  200  $\mu s$

- $\Rightarrow$  3 planes of Large Area Telescope for AIDA project (EU-FP7)

- st windowing of  $\lesssim$  1imes6 cm $^2$  (collimated beam)

- $\Rightarrow$   $\sim$  50  $\mu s$  r.o. time

- \* 50-100  $\mu m$  pitch variants under consideration (trackers)

### • Alignment Investigation Device (AID) :

- \* box allowing to mount 3-4 pairs of ladders arranged in 3-4 consecutive layers  $\equiv$  VTX sector

- \* can be equipped with PLUME (2-sided) ladders

- \* ladders mounted on movable micrometric supports

- ⇒ investigate alignment with particles traversing overlapping regions of neighbouring ladders

- \* allows developing clustering, tracking & vertexing algo. with particle beams

|                  |                | SIOLEN BURNESS         | SUZE                    | NICCLIMINATION         | SICULUIUSIC    | BING STREET     |

|------------------|----------------|------------------------|-------------------------|------------------------|----------------|-----------------|

|                  | 212×212        | 915×915                | 212×213                 | 915×915                | 915×915        | 212×612         |

| Discriminators   | 212x512        | 612×612                | 612×612                 | 612×612                | £12x512        | e15×e12         |

| 512x512          | 512x512        | 512x512                | 512x512                 | 512x512                | 512x512        | 512x512         |

| Discriminators   | 512x512        | 512x512                | 512x512                 | 512x512                | 512x512        | 512x512         |

| SUZE             | Discriminators | Discriminators<br>SUZE | Discriminators<br>SU7E  | Discriminators<br>SUZE | Discriminators | Discriminato    |

| (emaine (emaine) | IONORA IONORA  | 1000000 (0000000)      | Contraction Contraction | Ganada Ganada          |                | (001100 (001100 |

# Synergy with ILC Vertex Detectors

• Specs of ALICE-ITS/-MFT, CBM-MVD, SuperB-SVT, AIDA, ... overlap those of ILC Vertex Detectors

### Example of ILD-VXD

# **MIMOSA & AROM Sensors for an ILC Vertex Detector**

- Assuming MIMOSA and AROM variants to equip innermost and outer layers

- \* MIMOSA-in and AROM-1 equip innermost layer

- \* MIMOSA-out and AROM-2 equip outer layers

| Sensor version                       | MIMOSA-in    | MIMOSA-out   | AROM-1    | AROM-2    |

|--------------------------------------|--------------|--------------|-----------|-----------|

| Active area dimensions $[mm^2]$      | 8.7×31.0     | 19.6×31.0    | 10.9×31.0 | 20.8×31.0 |

| Pixel dimensions $[\mu m^2]$         | 17×17        | 34×34        | 17×85     | 34×72     |

| Single point resolution $[\mu m]$    | $\lesssim$ 3 | $\lesssim$ 4 | 5-7       | $\sim$ 10 |

| Read-out time $[\mu s]$              | 50           | $\sim$ 100   | 1.5       | 7         |

| Power consumption: instantaneous [W] | $\sim$ 1.8   | $\sim$ 0.6   | 2.7       | 0.7       |

| average [mW]                         | 36           | 12           | 55        | 14        |

- Power consumption (average value stands for 5 ms long power-on periods  $\equiv$  2% duty cycle):

- \* layer 1: 250 W (inst.)  $\Rightarrow$  5 W (average)

- \* layer 2: 120 W (inst.)  $\Rightarrow$  2.4 W (average)

- \* layer 3: 200 W (inst.)  $\Rightarrow$  4 W (average)

- $\Rightarrow$  Complete detector instantaneous power  $\lesssim$  600 W  $\Rightarrow$  <12 W in average  $\Rightarrow$  air cooling OK

- $\triangleright$   $\triangleright$   $\triangleright$  power cycling still needs being investigated  $\rightarrow$  power > 100 ladders (<10 g) with ~200 A in 3.5 T !!!

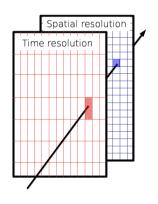

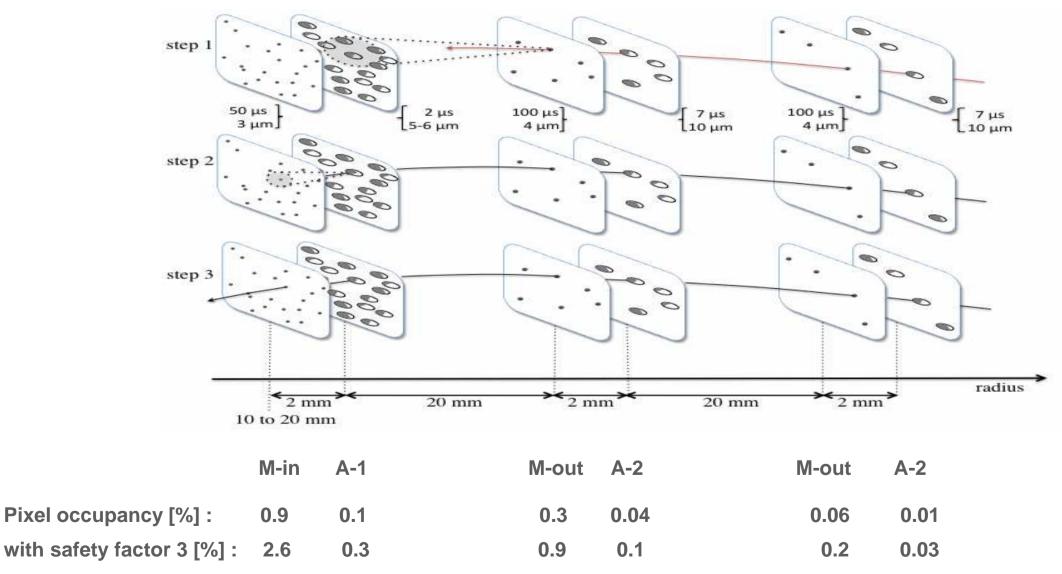

# **Tracking through ILD-VXD**

• Tracking from outside towards IP combining MIMOSA spatial resolution & AROM timestamp

\* AROM provides < 2 or 7  $\mu s$  time stamping

# **Using 3DIT to reach Ultimate CMOS Sensor Performances**

- 3D Integration Technologies allow integrating high density signal processing  $\mu$ circuits inside **small** pixels by stacking (~ 10  $\mu$ m) thin tiers interconnected at pixel level

- 3DIT are expected to be particularly beneficial for CMOS sensors :

- \* combine different fab. processes  $\Rightarrow$  chose best one for each tier/functionnality

- \* alleviate constraints on peripheral circuitry and on transistor type inside pixel, etc.

- Split signal collection and processing functionnalities

- \* Tier-1: charge sensing

- \* Tier-2: analog-mixed  $\mu$  circuits

- \* Tier-3: digital  $\mu$ circuits

Conventional MAPS 4 Pixel Layout

3D 4 Pixel Layout

- The path to nominal exploitation of CMOS pixel potential :

- \* fully depleted 10-20  $\mu m$  thick epitaxy  $\Rightarrow$  t<sub>collect</sub>  $\lesssim$  5 ns, rad. hardness > Hybrid Pixel Sensors ???

- \* FEE with  $\leq$  10 ns time resolution  $\rightarrow$  solution for CLIC & HL-LHC specifications ???

- 3DIC coordinated by FNAL produced painfully 1st generation of chips (debugging process) Devt of CAIRN = CMOS Active pixel sensors with vertically Integrated Read-out & Networking functionnalities

## **SUMMARY** (MIMOSA/AROM based Subatomic Phys. Trackers)

- Increasing demand for highly granular & thin (low power) pixel devices (charm tagging) :

- $\Rightarrow$  CPS offer the highest potential for these applications (also for large areas  $\rightarrow$  cost, power)

- R&D of 1st generation CPS (0.35  $\mu m$ )  $\sim$  completed: STAR-PXL, CBM-MVD1, ...

- $\hookrightarrow$  **ILD-VXD sensors** comply with all specs for 500 GeV :  $\sigma_{sp}$ , thickness, rad.tol., speed, power

- 2-sided ladder (0.3% X<sub>0</sub>) & unsupported ladder (0.15 % X<sub>0</sub>) devts progressing : PLUME, SERNWIETE

$\hookrightarrow$  allows for < 3  $\mu m$  / 2  $\mu s$  in ILD-VXD innermost layer ( < 3.5  $\mu m$  / 7  $\mu s$  in outer layers )

- R&D of 2nd generation CPS (0.18  $\mu m$ ) started with MIMOSA-32: radiation tol. & read-out speed

- Several MIMOSA-32 lab test results encouraging : CCE, Ion. Rad. tol., noise at 35°C

- Beam tests in Summer 2012 for m.i.p. detection performance assessment (incl. NI rad. tol.)

- Present sources of investigation : inaccurate in-pixel  $\mu$ circuitry modeling, noise  $\geq$  30 % too high at 20°C

- Next steps of 0.18  $\mu m$  based sensor devt  $\equiv$  important milestones :

- Establish high-performance in-pixel signal amplification  $\mu$ -circuitry in Q3/Q4 2012

- Mid-scale prototypes validating architectures (MIMOSA-22THR, AROM-1, SUZE-02) in Q3/Q4 2012

- Full Scale Basic Block (FSBB) expected to be fabricated in 2013

- Dedicated sensors ≥ 2014: ALICE-ITS/-MFT, CBM-MVD2/-MVD3, ILC-500/1000, AIDA, SuperB-SVT, eIC, ...

- Long term R&D : 3D sensors for CLIC, HL-LHC, etc.  $\rightarrow$  CAIRN chips under devt

# **Towards a Large Pitch**

- Large pitch : Motivations

- \* elongated pixels allow faster read-out

```

times trackers (e.g. ILD-SIT) require \sigma_{sp}\gtrsim 10 \mu m

```

- $\Rightarrow$  minimise number of pixels for the sake of power dissipation, integration time and data flow

- Large pitch : Limitations (besides spatial resolution)

- \* DANGER: increasing distance inbetween neighbouring diodes

- $\Rightarrow$  particles traversing sensor "far" from sensing diodes may not be detected because of e<sup>-</sup> recombination

- \* "fragile" detection efficiency, exposed to losses due to irradiation, high temperature operation & "slow" read-out

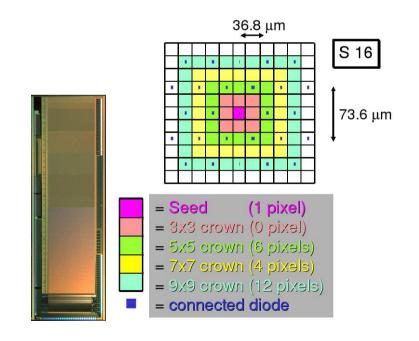

- Elongated pixels : Test results

- \* elongated pixels allow minimising the drawbacks of large pitch

- \* concept evaluated with MIMOSA-22AHR prototype, composed of a sub-array with 18.4×73.6  $\mu m^2$  pixels  $\triangleright \triangleright \triangleright$

- times m.i.p. detection performances assessed at CERN-SPS (T  $\sim$  15 $^{\circ}$ C)

- ---  $\epsilon_{det}\sim$  99.8 %

- $ightarrow \sigma_{sp}\sim$  5-6  $\mu m$  (binary charge encoding)

- Square pixels : prototype back from foundry

- \* MIMOSA-29 : fabricated on high-resistivity epitaxy in Summer '11 \* pixels of 64×16/32/64  $\mu m^2$  and 80×16/48/80  $\mu m^2$

- \* chips back from foundry  $\Rightarrow$  test preparation under way <sub>26</sub>

# **VXD - SIT Variant Composed of CPS**

- ILD-SIT : baseline assumes 2 double-sided  $\mu$ strip detector layers

- \* try understanding if CMOS sensors could improve performance with their high spatial resolution

- \* advantage : spatial resolution  $\vartriangleright$  4×4  $\mu m^2$  instead of 7×50  $\mu m^2$

- $\Rightarrow$  improved soft track reconstruction (p) and TPC link

- potentially : material budget, cost

- \* disadvantage : time resolution  $\triangleright$  7  $\mu s$  instead of O(100)ns Is power a pb ?

- Variant of VXD–SIT design made of CMOS pixel sensors (other variants give similar performances)

| Layer | $\sigma_{sp}$   | $t_{int}$       | Occupancy [%]          | Power              |

|-------|-----------------|-----------------|------------------------|--------------------|

|       | MIMOSA/AROM     | MIMOSA/AROM     | w/o safey factor       | inst./average      |

| VXD-1 | 3 / 5-6 $\mu m$ | 50 / 2 $\mu s$  | 0.9(2.6) / 0.1(0.3)    | 250/5 W            |

| VXD-2 | 4 / 10 $\mu m$  | 100 / 7 $\mu s$ | 0.3(0.9) / 0.04(0.1)   | 120/2.4 W          |

| VXD-3 | 4 / 10 $\mu m$  | 100 / 7 $\mu s$ | 0.06(0.2) / 0.01(0.03) | 200/4 W            |

| SIT-1 | 4 / 15 $\mu m$  | 100 / 7 $\mu s$ | $\lesssim$ 0.01        | $\sim$ 1.3 kW/26 W |

| SIT-2 | 4 $\mu m$       | 100 $\mu s$     | $\lesssim$ 0.01        | $\sim$ 2.5 kW/50 W |

- ILD-SIT : power consumption (average  $\lesssim$  100 W for  $\gtrsim$  4 m  $^2$  coverage) seems affordable

- $\Rightarrow$  need benchmark event study with beam BG to evaluate track reconstruction performance