## 10GbE for data streaming in European XFEL DAQ System

Patrick Gessler (XFEL)

- The European XFEL Project

- Detectors and photon diagnostics providing data

- Beam time structure drive DAQ and control

- Architecture concept

- Hardware overview

- Processing and streaming

- The big picture

- Conclusion

HELMHOLTZ ASSOCIATION

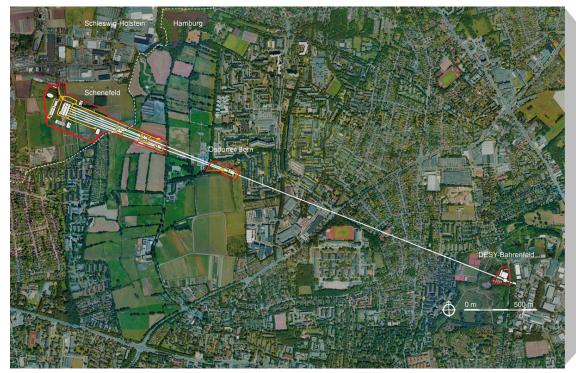

| Length                           | 3.4km         |

|----------------------------------|---------------|

| Depth of tunnels                 | 6m bis 38m    |

| Costs (Construction, Commission) | > 1 Mrd. Euro |

| Wave length Photons              | 0.05nm – 6nm  |

| Users' operation                 | 2016          |

CRISP

24th May 2012 | 10GbE Workshop | DESY Seminar room 1 | Patrick Gessler

4

HELMHOLTZ

CRISP

## XFEL Der European X-Ray Free Electron Laser

#### Optics (WP73)

- KB mirrors for focusing

- Refractive lens focusing

- Monochromator

- Collimator

- Slits

European

Attenuators

Vacuum systems (WP73)

- Turbo pumps

- Ion pumps

#### Beam diagnostics (WP74)

- Intensity monitors

- Beam positioning monitor

- Photon-electron spectrometers

- K-monochromator and cameras

- Screens and camera

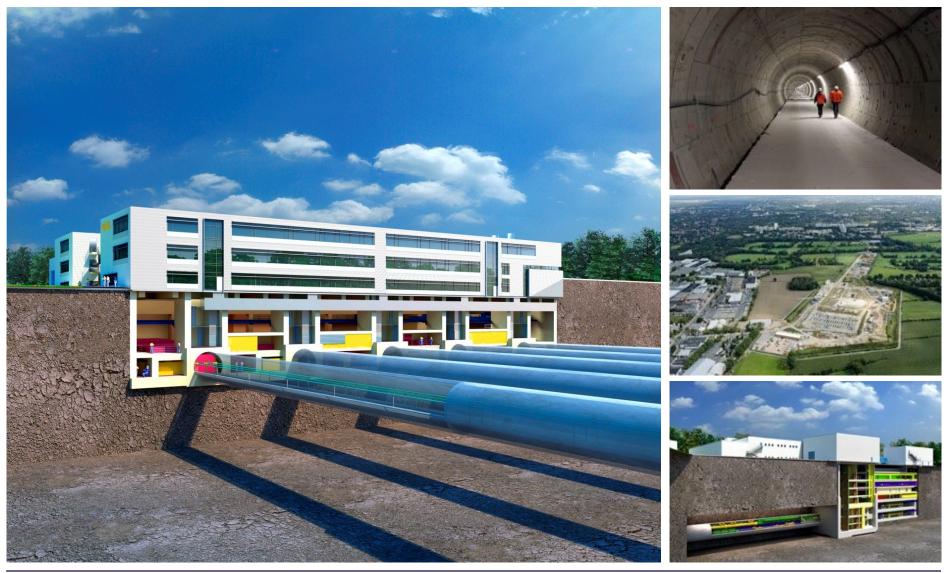

#### Tunnels contain components listed above

Laser systems (WP78)

Pump laser and diagnostics

#### Sample environment (WP79)

- Particle injector

- Cryostat

Detectors and photon diagnostics providing data

Precision stages

#### Experiment detectors (WP8x)

- e- and ion TOF

- Point detectors (diodes)

- Spectrometers

#### Experiment 2D detectors (WP75)

- AGIPD

- LPD

- DSSC

- pnCCD

DAQ significant

Experiment hutches contain components above + many of the tunnel instruments

10GbE for data streaming in European XFEL DAQ System

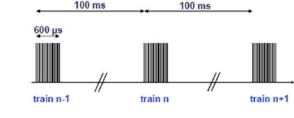

### **XFEL** Beam time structure drive DAQ and control

- Readout rate driven by bunch structure

- 10 Hz train of pulses

- 4.51 MHz pulses in train

- Data volume driven by detector type and use of data

| Detector type        | Sampling | Data/pulse | Data/train | XFEL/sec |

|----------------------|----------|------------|------------|----------|

| 1 Mpxl 2D camera     | 4.5 MHz  | ~ 2 MB     | ~ 1 GB     | ~ 10 GB  |

| 1 channel digitizer  | 5 GS/s   | ~ 2 kB     | ~ 6 MB     | ~ 60 MB  |

| Low latency feedback | 5 GS/s   | ~ 2 B      | ~ 4 KB     | ~ 40 KB  |

| Screen camera        | 10 Hz    | ~ 2 MB     | ~ 2 MB     | ~ 20 MB  |

- Experiment detectors are characterized by large data sizes (PBS)

- Need to acquire, long term storage required, offline analysis, multi-user full AAA s/w framework

- Feedback systems are characterized by low data rates and low send latency (machine+PBS)

- Use on-the-fly, no need to store, trigger level with limited analysis, single user

- Diagnostic devices are characterized by low data sizes (machine+PBS)

- Use on-the-fly, possibly short term storage, on-the-fly analysis, single user

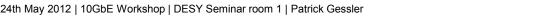

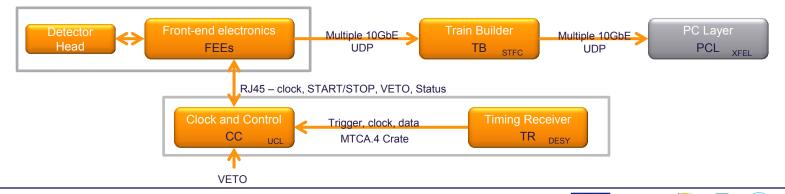

## XFEL Architecture concept

HELMHOLTZ

ASSOCIATION

CRISP

Large data volumes, their acquisition, storage and analysis and changing experiment configurations are issues the PBS system architecture is trying to solve

- Multiple layers with well defined APIs 1 slice

- to allow insertion of new technology layers

- Multiple slices for partitioning and scaling

- camera sizes will increase and slice replication will be one solution

- Allow full speed write through to online storage, but discourage usage

- sometimes this capability is needed to understand measurement

- Enforce data reduction and rejection in all layers

- early data size reductions and data rejection are needed to reduce storage resources

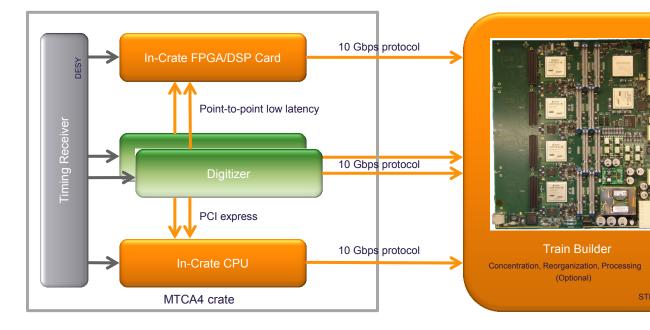

### **XFEL** MicroTCA.4 as main platform

- MicroTCA.4 allows

- High-bandwidth communication between

- Boards and CPU via PCIe

- Boards via point-to-point connections

- Synchronization via Timing Receiver

- Trigger

- Clocks

- Machine parameters

- Bunch structure

- Remote control and monitoring

- Module changes during operation (Hotplu

- Functional extension via RTMs

(University Collage London)

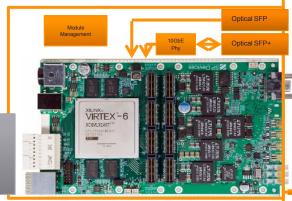

DAMC2 – Universal digital AMC (DESY)

(Stockholm University / DESY)

SIS8300 – ADC AMC (Struck Innovative Systems)

High-performance DSP and FPGA board (DMCS/DESY)

### **XFEL MTCA.4 High-Speed Digitizer developments**

#### • A development with SP Devices Sweden AB just started

| Product | Resolution | Maximum<br>Sample Rate | Analog<br>Bandwidth | Channels | On-Board<br>Memory Size | Interface             |

|---------|------------|------------------------|---------------------|----------|-------------------------|-----------------------|

| SDR14   | 14bit in   | 800 MSPS in            | 500 MHz             | 2 in     | 2 x 500 Mbyte           | USB, cPCle/PXle, PCle |

| 301(14  | 14bit out  | 1600 MHz out           |                     | 2 out    | 2 x 300 Mbyte           |                       |

| ADQ108  | 8 bit      | 7 GSPS                 | 2 GHz               | 1        | 1024 MS                 | USB, cPCIe/PXIe, PCIe |

| ADQ412  | 12 bit     | 1.8/3.6 GSPS           | 2/1.3 GHz           | 4/2      | 700 MS                  | USB, cPCIe/PXIe, PCIe |

| ADQ1600 | 14 bit     | 1.6 GSPS               | 800 MHz             | 1        | 500 MS                  | USB, cPCIe/PXIe, PCIe |

| ADQ DSP | -          | -                      | -                   | -        | 1 GByte                 | USB, cPCIe/PXIe, PCIe |

- They will design an AMC version of their digitizer family

- Additional interfaces and MTCA.4 connectivity added

- Final products expected end of Q4 2012

Development of an MTCA.4 compatible AMC

#### Applications

- Photon Diagnostics

- XGMD

- XBPM

- PES

- Detectors

- 0D (e.g. APD)

- 2D (e.g. pnCCD)

HELMHOLTZ

ASSOCIATION

Experiments

CRISP

• eTOF, iTOF

HELMHOLTZ

ASSOCIATIO

#### AGIPD Adaptive Gain Integrating Pixel Detector (AGIPD)

#### Energy range 3 - 13 keV Dynamic range 10<sup>4</sup>@12 keV Single Photon Sens.<sup>xyGap</sup> Storage Cells © 300<sup>20 × 2561</sup>

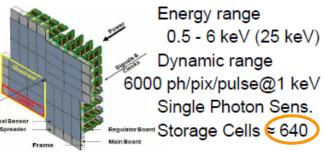

#### DEPFET Sensor with Signal Compression (DSSC)

#### Large Pixel Detector (LPD)

Energy range 5 (1) - 20 keV (25 keV) Dynamic range 10<sup>5</sup>@12 keV Single Photon Sens. Storage Cells ≈ 512

#### **Other Detectors**

- 0D/1D detectors for high repetition rate applications (e.g. veto, dispersive spectrometers)

- Small areas, low rep. rate, low energy 2D imaging detectors

CRISP

Particle detectors (eTOF, iTOF)

#### Control and DAQ features

- 2D: custom systems (ASICs, capacitive and digital pipelines), acquire (imited) number of pulses per train; modular design = 16 modules per Mpxl

- 1D: strip detectors

- OD (diodes...) and Particle detectors: use Fast ADCs or Digitizers

#### European **2D** detector control, processing and streaming FEL

- Control and synchronization

- Clock and Control RTM

- Synchronized with Timing Receiver

- One RTM controls a 1 Mpixel Detector

- Data reorganization and processing in Train Builder

- Partial frames will be reassembled

- A complete train put into memory

- Transmitted via 10GbE to PC Layer

- Dual 10GbF FMCs from DESY/FFA

CRISP

Clock and Control RTM (UCL)

DAMC2 (DESY/FEA)

HELMHOLTZ

ASSOCIATION

# European

### **XFEL** Data processing and transmission concept

- In-crate processing

- In FPGAs of Digitizer

- In local CPU

- In a DSP/FPGA Board

- Processing of multiple sources

- Processing in FPGAs

- **Multiple Boards**

- Communication between all **FPGAs**

- DDR and QDR Memory

PC Layer

PC Layer

PCL XFE

Software

HELMHOLTZ

ASSOCIATION

- **CPUs**

- **GPUs**

DESY

HELMHOLTZ

CRISP )

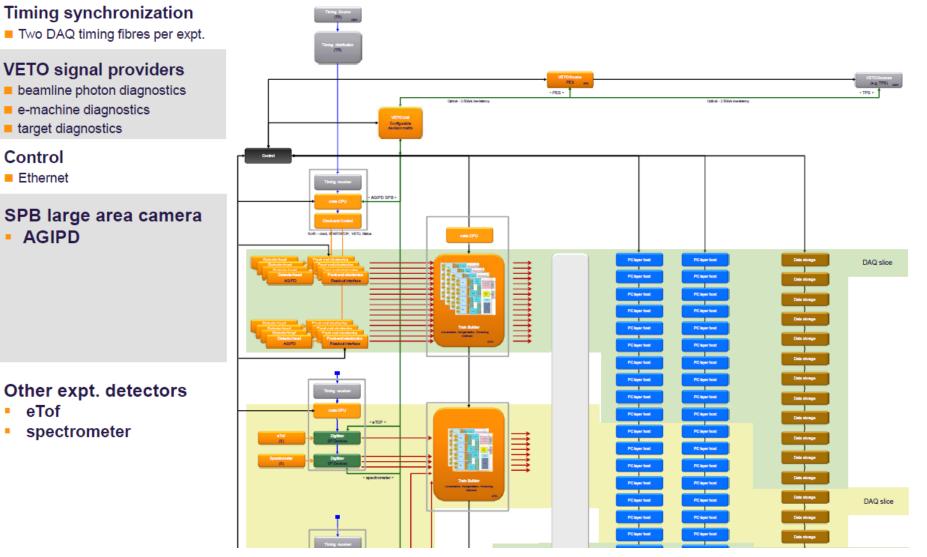

### **XFEL** The big picture – DAQ and control part 1

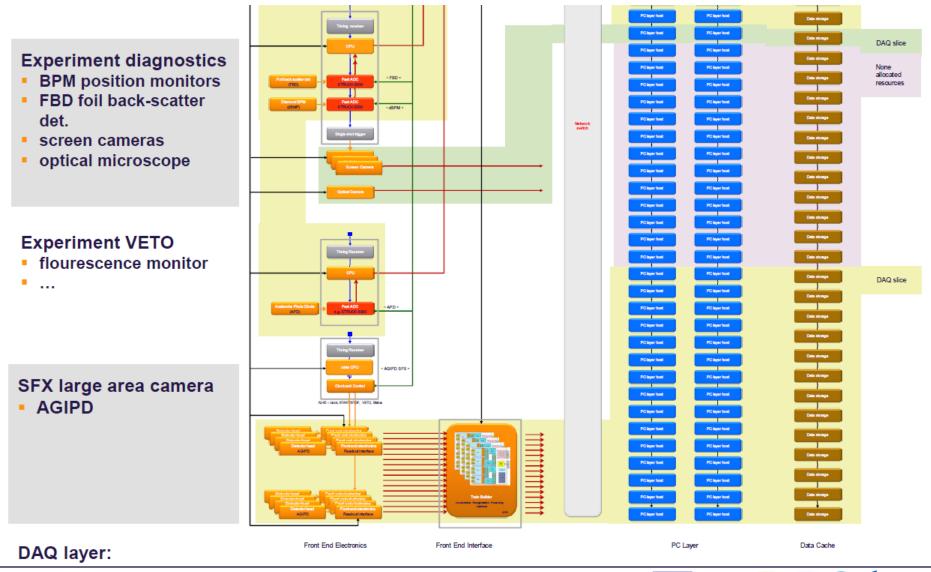

### **XFEL** The big picture – DAQ and control part 2

### **XFEL** Conclusion

15

- 10GbE interface rare on standard modules (PC, Digitizer)

- Manufacturers thinking about adding it

- Has to be requested in most cases

- Add-on boards might be needed

- 10GbE provides a standard to stream data to FPGAs and PC

- FPGA stages could be replaced with PCs for testing

- COTS hardware available

- Bandwidth is sufficient for current sources but at limit

- Future detector generations will require more

- Currently only UDP/IP implemented

- Fine for FPGA  $\rightarrow$  FPGA with no switch

- TCP/IP via switch and to PC layer required/desired

Thank you for your attention!

Questions?

24th May 2012 | 10GbE Workshop | DESY Seminar room 1 | Patrick Gessler