## **SIS8300L Design Status**

Frank Ludwig – DESY for the LLRF Team

## **Starting Point - SIS8300\_V2**

FIL

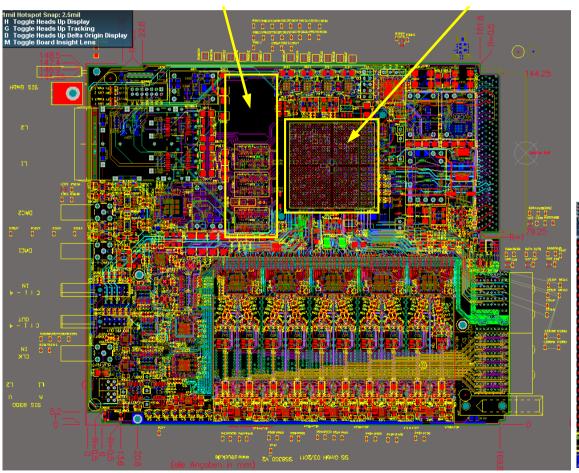

(1) FPGA and RAM ----

FPGA has to be changed to type Xilinx Virtex 6 VLX130, 70% done (more DSP slices, 3Gbps-> 6GBps link, compatible to uTC V7)

RAM has to be changed to DDR3 type 5x16 chips (Nanya NT5CB256M16BP-CG), 70% done

3Gbps -> 6Gbps (via feed throughs recommended from Xilinx) needs space

(2) Improving CMR ----- (FL, 18.04.12)

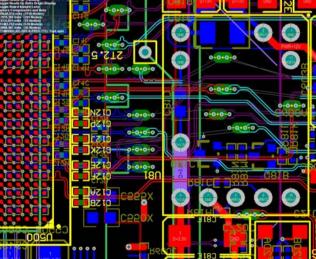

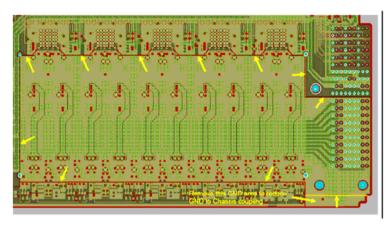

√ - Replace 10x AC input transformer T41...T61 to TC1-1T+ (mini-circuits), no universal footprint (improved CMR by >10dB due to better imbalance), primary middle side not connected to GND

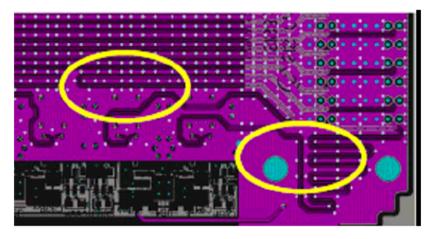

√ - CLK shielded with more vias (yellow marked)

X - Improve differential signal routing symmetries (yellow marked)

can not rearranged because of compatibility to Z3 pin assignment

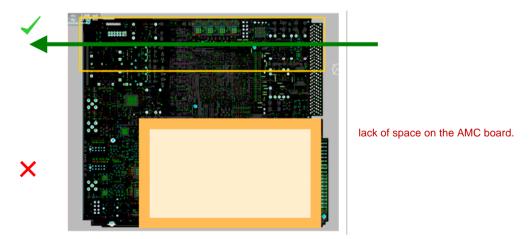

x can not realized because of lackof space on the AMC board

(2) CLK tan points ----- (FL 18 04 12)

✓ - Small additional tap points for R70M ... R74M for CLK prober

(3) Remove DC-length compensation ----- (FL, 18.04.12)

- DC channel support stays, but all length compensation can be removed.

(4) Replace local DC regulators to a global one for DC front-end OPVs ----- (FL, 18.04.12)

- Remove DC stabilizers (U95A ... U99A) sections and replace by one big +5,-5V driver. Preferred position on the bottom side (may be conflict with device height)

lack of space on the top side of the AMC board

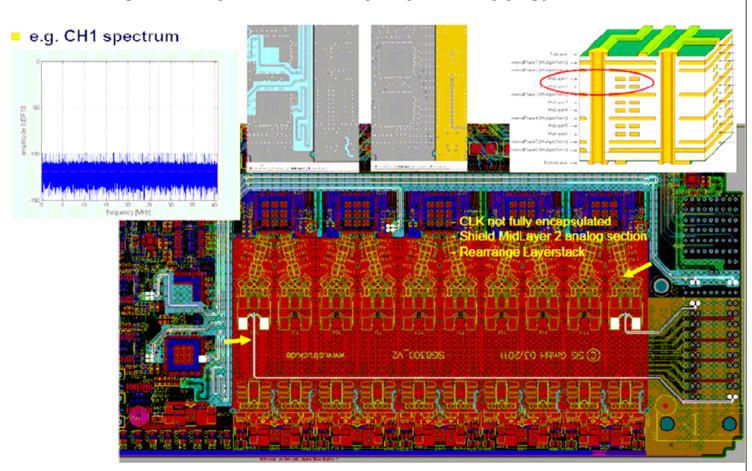

(5) (CLK crosstalk on channel 0,1,9) ---- is not proven by measurements ----- (FL, 18.04.12)

- CLK has to be fully encapsulated

- Shield Midlayer 2 analog section or layerstack rearrangement

- Shield Midlayer 1 analog section within split plane using polygones

(6) Reduce Transformer channel crosstalk ----- (FL, 18.04.12)

- Wider solder stop and fixing wires for shielding on top

- Complete frame for solderstop timplate housing (assembly option)

lack of space on the top side of the AMC board

(7) Front-Panel Connectors ----- (FL, 18.04.12)

- Front Panel connectors 2xSFP cages, CLK\_IN, DAC1, DAC2, 2x Harling Interface stays.

- Assembly variants:

- (1) LLRF assembly variant (Option 1):

- CLK IN (SMA not assembled or footprint-compatible to SMA)

- DAC1, DAC2, Digital Interface not assembled

- EMI Block installed

- (2) Other application assembly variant (Option 2):

- CLK IN, DAC1, DAC2 (SMA) fixed on panel

- Digital Interface (Harling) assembled

- EMI Block installed

- 4x LEDS replaced by 1x4 row light pipe smaller ones (MTCA like) rejected from Struck FPGA JTAG stays internal not on the front panel

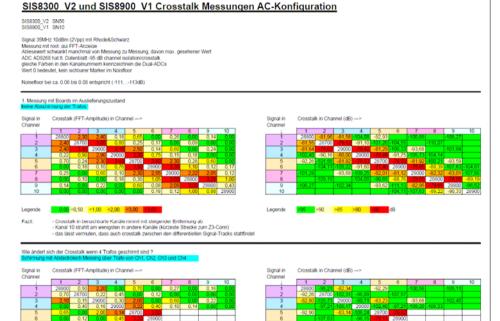

SIS8300 V2 und SIS8900 V1 Crosstalk Messungen DC-Konfiguration

SIS8300\_V2 SN27 (modifiziert) SIS8900\_V1 SN10 (OpAmps AD8139 mit 1pF Feedback-C's)

Antialiasingfilter auf dem SISS300 so modifiziert, wie im Datenblatt des ADCs für DC mit 100MHz Bandbreite vorgeschlagen (nicht unser Ausliefenungszustandf) 1. sichtbarer Effekt, es gibt kaum Marker mehr in der FFT, die evtl. von der SampleandHold-Shufe kommen (sonst verschiedenste Frequenzen)

Signal 35MHz 12 2dRm (2Vpp) mit Rhode&Schwarz

Signai 35MHz 12 200m (r/vpp) mit knodea/schwarz Messung mit root\_gui FFT-Anzeige Ablesewert schwarkt manchmal von Messung zu Messung, davon max, gesehener Wert

ADC AD9268 hat it. Datenblatt -95 dB channel isolation/cro gleiche Farben in den Kanalnummem kennzeichnen die Dual-ADCs Wert 0 bedeutet, kein sichbarer Marker im Noisfloor

#### 1. Messung mit modifiziertem Antialisaingfilter auf der SIS8300

Crosstalk (FFT-Amplitude) in Channel --->

- Crosstalk besteht nur in geringem Maß zum Nachbarn des gespeisten Kanals ( >90dB)

- -baputechnisch geseinen ist eine Verbribung zwischen den zur geraben oder zur ungeraben kanzlei er zu 23-Connector zu finden zwischen berachtsaften zur ein 23-Connector zu finden zwischen berachtsaften zugenaben Kanzlein ergibt sich ein Crosstalk von zu -75-7766 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 24-85-69 -

- wichtig. Vorraussetzung für diese Messergebnisse ist das korrekte Antialiasingfilter It. Datenblatt des ADCs für DC-Kopplung

#### Messung, Kanal 3 modifiziert, Verbindungsfeitungen des OpAmps zum Z3-Conn am OpAmp getrennt (499 Ohm raus) und Input-Pins des OpAmps mit 499 Ohm zu GND totgelegt OpAmps sind ADR136 (etwas höheres Rauschen)

| Signal in<br>Channel | Crosstalk (FFT-Amplitude) in Channel> |       |      |              |       |       |       |       |       |      |

|----------------------|---------------------------------------|-------|------|--------------|-------|-------|-------|-------|-------|------|

| 1                    | 1                                     | 2     | 3    | 4            | 5     | 6     | 7     | 8     | 9     | 10   |

| 1                    | 31000                                 | 0,40  | 0,00 | 0,00         | 1,30  | 0,00  | 0,60  | 0,00  | 0,35  | 0,0  |

| 2                    | 0,80                                  | 31000 | 0,50 | 1,50<br>0,35 | 0,00  | 0,35  | 0,00  | 0,00  | 0,00  | 0,0  |

| 3                    | 4,50                                  | 0,00  | 4,60 | 0,35         | 4,50  | 0,00  | 1,20  | 0,00  | 0,50  | 0,0  |

| 4                    | 0,00                                  | 1,40  | 0,80 | 31500        | 0,50  | 1,50  | 0,00  | 0,40  | 0,00  | 0,0  |

| 5                    | 1,30                                  | 0,00  | 0,00 | 0.95         | 31500 | 0,30  | 4,60  | 0,00  | 1,30  | 0,0  |

| 6                    | 0,00                                  | 0,00  | 0,00 | 1,40         | 0,65  | 31500 | 0,50  | 1,60  | 0,00  | 0.5  |

| 7                    | 0,50                                  | 0,00  | 0,00 | 0,00         | 4,50  | 0,55  | 31500 | 0,00  | 5,00  | 0,5  |

| 8                    | 0,00                                  | 0,00  | 0,00 | 0,40         | 0,00  | 1,30  | 0,50  | 31500 | 0,70  | 1,6  |

| 9                    | 0,00                                  | 0,00  | 0,00 | 0,00         | 1,30  | 0,00  | 4,60  | 0,80  | 31800 | 0,0  |

| 10                   | 0.00                                  | 0,00  | 0.00 | 0.00         | 0.00  | 0.35  | 0.00  | 1,50  | 0.55  | 3180 |

- Crosstalk von Channel 1 auf Channel 3 ist letzt weg. d.h. der Crosstalk kommt vor dem OnAmp in den Signalweg

- coossile van valente in au Calama Sa (nat way in the Coossile in north you delt pyrithin delt agraining).

bei Speisung von Kanal 3 kommt trotz getrenter Leitungen noch etwas durch (4,60), Signal geht aber sehr dicht an die Inputplins (Übersprechen?

blau markierte Werte sind die durch die Modifikation veränderten Messwerte

- 0,00 <1,00 <2,00 <3,00 =4,00 =4,00 ohne Füllung = unverändert

- downth Karnal 3 mur die Leitung bis voor door voor voor moortenand voor deem Op-Amp specist und danach der Signatweg endet, dindert sich dass Übersprechen in die anderen Kanalië ausser dem Nachbankanal 2 nic -daraus muss man schliessen, dass das grosse Übersprechen vor dem Op-Amp verursacht wird und auch nicht über die Stromversorgung stattfindet

- Messung, Verbindung am Kanal 3 zum 23-Conn wieder hergestellt auf dem 8900 den OpAnn-Auspaing zum 23-Conn abgehennt (z.v.) O hhm-Ris raus) auf dem 8900 der differenteilen Signatietungen zum 23-Conn an der Trennstelle des OpAmps auf GND gelegt.

- Speisung in Ch3 ergibt FFT-Wert 0.8 (-91.77dB) in Ch3 (Übersprechen trotz aufgetrennter OpAmp-Outputs in gegroundete Signalfeitungen)

Speisung in Ch3 ergibt FFT-Wert 0.5 (-96dB) in Ch4 (Übersprechen über gemeinsame Stromversorgung, immer 2 Kanāle mit A+5V und A-5V)

- Speisung in Ch3 ergibt in allen anderen Kanälen keinen messbaren Crosstalk

- Speisung aller anderen Kanäle ergibt in Ch3 den schon vorher gemessenen Crosstalk

- der Crosstalk kommt also auf der Leitung vom 8900-OpAmp-Output zum 8300-OpAmp-Input (incl. Z3) zustande

ag 16.02.2012

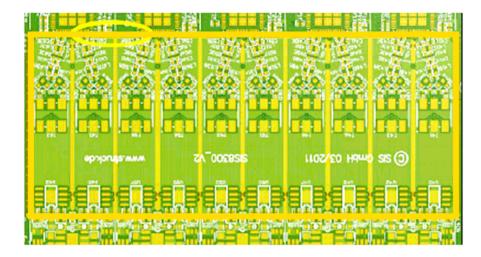

### ... courtesy of A.Grüttner (Struck)

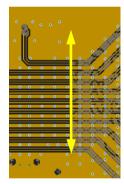

Transformer to be shielded or bridged!

- bei geschirmten Trafos ergibt sich zwischen benachbarten ungeraden Kanälen ein Crosstalk von ca. -82..-83dB

Crosstalk dominated by CHx coupling via LO in DWC.

bei geschirmten Trafos ergibt sich zwischen benachbarten geraden Kanälen ein Crosstalk von ≻95dB (kleiner als ADC channel/isiotation crosstalk

TIL.

(8) EMI Block ----- (FL, 18.04.12

- EMI metal block (c) DESY GND to chassis connection (yellow marked) (Option), Add solderstop exactly near the hot-swap, space (9mm x 13mm), distance pcb edge to middle hole 8mm, hole size for a 3mm screw massive connected to GND,

- Front panel hole and screw (3mm) for massive GND/Chassis connection

#### (8) DAC Z3 Option ----- (FL, 18.04.12)

- Dual DAC output (QDACO+, QDACO-, IDACO+, IDACO-) option 3 options: Front Panel, Z3 or with GND option

- Dual DAC output (QDAC1+, QDAC1-, IDAC1+, IDAC1-) at Zone 3

- Existing DAC Latency of SIS8300V2 with about 115ns was accepted

Unclear, because of lack of space on the top side of the AMC board.

#### (9) CLK External CLK input degradation ----- (FL, 18.04.12)

- Remove external CLK input clock spurious by rearrange the clock chips power supply (ADCLK946, MUX D, MUX E) -> spend own power supply regulator

#### (10) 3.3V Logic Levels Incompatibility to Virtex V6/7 ----- (FL, 25.04.12)

- Delay and trigger section stays (ADCLK946, MUX D, MUX E) compatibility to SIS8300V2

- RTM CLK0, RTM CLK1 stays, both signals will be delivered by DWC8300 V2.0

- MLVDS Ports 17-20 (Trigger, Clock, Interlock), MLVDS 125MHz is recommended.

- Timing distribution section clock-Divider, Clock-Divider, Clock-Path Multiplexer stays. The lines used only for slow parameter communication.

So an I2C expander to reduce FPGA pins or level shifter can be taken into account.

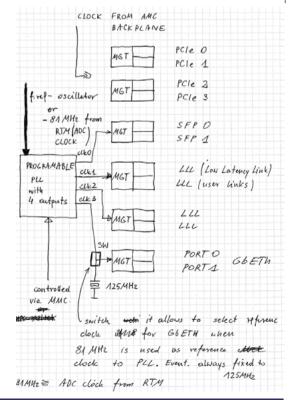

#### (11) Compatibility to V5/V6/V7, SFP, P2P (LLL) ----- (FL, TJ 26.04.12)

MGT frequencies at CLK0, CLK1, CLK2, CLK3 for V6 to V5,V6,V7 communication. External operation for all CLKx outputs: 125.xxxxMHz x20 (40) = 3 GHz (6GHz), 20 or 40 is a factor in the PLL chip 106.5MHz 250.0MHz 2x81.25MHz x n = 3GHz(6GHz)

81.25MH

There will be boards based on Virtex 5,6 and 7, so we need flexibility to be able to set a different link speed. This is valid for SFPs and P2P (LLL) links. Means clock divider or switchable oscillators have to be used.

# S15338 Functional Block Diagram

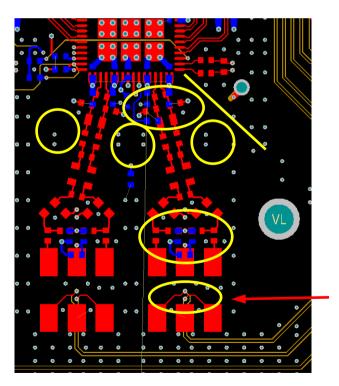

(13) Increase Split-plane distance for reduced rf-coupling ----- (FL, 07.05.12)

- Increase slit of the GND signal area from 0.29mm to 1mm

- Change the split plane near the guiding pin to reduce GND to chassis coupling

- Add more Multilayer Vias in the marked zone (top box) for bypassing Chassis to GND distortions from the ADC signal zone. Digital back currents will flow back more on top side.

\*\*2: Decision : Z3 pin assignment recommendation for Digitizers ------ (FL, 18.04.12)

SIS8300 V3 pin assignment: (grey marked signals changed to SIS8300V2)

|     | SIS8300L   |         |     |         |        |     |         |         |     |

|-----|------------|---------|-----|---------|--------|-----|---------|---------|-----|

| J76 | а          | b       | ab  | С       | d      | cd  | е       | f       | ef  |

|     | 1 PWR+12V  | PWR+12V | GND | PS#     | SDA    | GND | SDA_E   | SDA_I   | GND |

|     | 2 PWR+12V  | PWR+12V | GND | MP+3.3V | SOL    | GND | SQ_E    | SQT_I   | GND |

|     | 3 D0+      | D0-     | GND | D1+     | D1-    | GND | D2+     | D2-     | GND |

|     | 4 D3+      | D3-     | GND | D4+     | D4-    | GND | D5+     | D5-     | GND |

|     | 5 D6+      | D6-     | GND | D7+     | D7-    | GND | D8+     | D8-     | GND |

|     | 6 D9+      | D9-     | GND | D10+    | D10-   | GND | D11+    | D11-    | GND |

|     | 7 RESET+   | RESET-  | GND | GND     | GND    | GND | GND     | GND     | GND |

|     | 8 NC       | NC      | GND | alk2+   | ak2-   | GND | NC      | NC      | GND |

|     | 9 CLK0+    | CLKO-   | GND | NC      | NC     | GND | CLK1+   | CLK1-   | GND |

|     | 10 GND     | GND     | GND | GND     | GND    | GND | GND     | GND     | GND |

| J75 |            |         |     |         |        |     |         |         |     |

|     | 1 CH0_PA+  | CHO_PA- | GND | QDAC+   | QDAC-  | GND | CH9_TF+ | CH9_TF- | GND |

|     | 2 CH8_TF+  | CH8_TF- | GND | GND     | GND    | GND | CH1_PA+ | CH1_PA- | GND |

|     | 3 CH2_PA+  | CH2_PA- | GND | QDAC1+  | QDAC1- | GND | CH7_TF+ | CH7_TF- | GND |

|     | 4 CH6_TF+  | CH6_TF- | GND | GND     | GND    | GND | CH3_PA+ | CH3_PA- | GND |

|     | 5 CH4_PA+  | CH4_PA- | GND | IDAC1+  | IDAC1- | GND | CH5_TF+ | CH5_TF- | GND |

|     | 6 CH4_TF+  | CH4_TF- | GND | GND     | GND    | GND | CH5_PA+ | CH5_PA- | GND |

|     | 7 CH6_PA+  | CH6_PA- | GND | QDACO+  | QDACO- | GND | CH3_TF+ | CH3_TF- | GND |

|     | 8 CH2_TF+  | CH2_TF- | GND | GND     | GND    | GND | CH7_PA+ | CH7_PA- | GND |

|     | 9 CH8_PA+  | CH8_PA- | GND | IDACO+  | IDACO- | GND | CH1_TF+ | CH1_TF- | GND |

|     | 10 CH0_TF+ | CHO_TF- | GND | GND     | GND    | GND | CH9 PA+ | CH9_PA- | GND |

QDACx, IDACx GND Zone3 connection degradation

- 10/05/12: (AG-Struck), Common mode of LVDS inputs (cd-5,cd-3,cd-1) can be done.

FIL

(99) Unclear things ----- (FL, 03.07.12)

- RESET Option via Z3 decided, proposed Z3 pins 7a (RESET+), 7b (RESET-)

- RTM Management, RTM current readback ? TBD, no common solution

```

DAMC2 - TPS2568RHBT - current limiter

uTC - LTC4223 - current limiter

sIS8300 - TDS22943 - current limiter

```

- Analog cell bypass via complete via track frame, ADCs are not included at the moment. Complete via track frame around the crucial section. Short at Z3 TBD.

- Z3 J75, 1cd, 3cd, 5cd optional future DACs output placeholders. Can be GND at SIS8300\_Vx but not DWC83000\_Vx.

- AMC Connector GND thermal reliefs Y/N ? unclear from EMI -> Reliefs

- +1 DAC, Calibration Method or regulation purpose

- RTM8900 DAC Output test Pickups

- MLVDS Driver between FPGA and AMC should be replaced by faster ones

- DWC Z3 SIS8300L, Z3 differential level to be checked -> QA & QC

- AMC Rx19 RESET distribution (HK)

- FPGA load performance measurements with SIS8300 V2 with different spurious

- SIS8300L (HVF) Jitter section <80fs, no DC-channels, bypass sections for EMI

## Thanks for your attention!