## Overview of the MTCA.4 and ATCA based DAQ electronics and concepts for the XFEL

*MicroTCA Workshop for Industry and Research* 11<sup>th</sup> – 12<sup>th</sup> December 2012

> Patrick Gessler European XFEL GmbH

### XFEL Agenda

- Usual applications at photon experiments and diagnostics

- DAQ challenge and data management architecture

- MTCA and ATCA hardware and concepts to implement the DAQ

- Architecture

- MicroTCA and ATCA Modules and Interfaces

- VETO System

- High-level FPGA firmware development

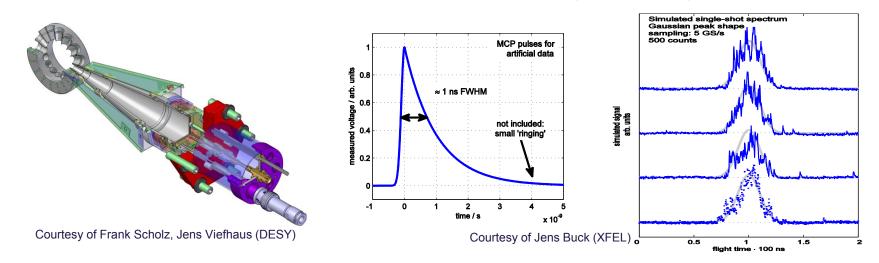

### **XFEL** Usual Applications at Experiments

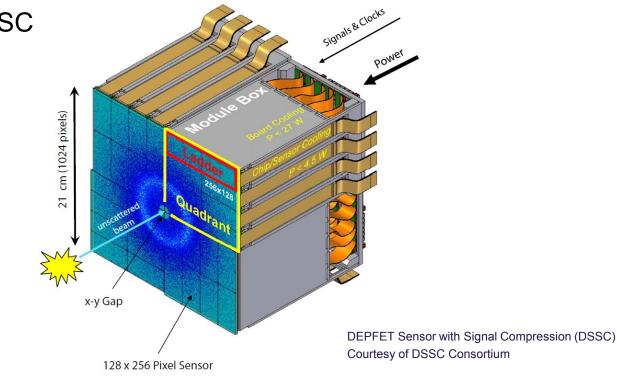

- Energy measurement

- Photon counting

- Time of Flight type measurements

- 2D picture detection

- → Example: DSSC

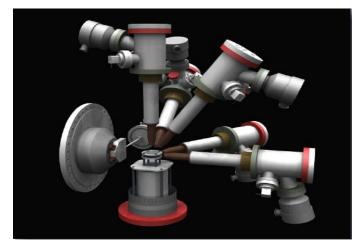

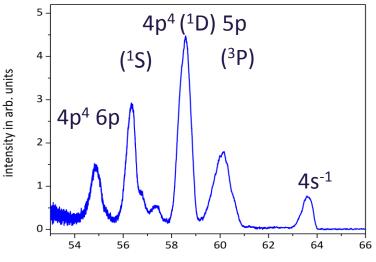

### **XFEL** Applications: Time of Flight measurements

Courtesy of John Bozek (AMO endstation at LCLS)

#### Kinetic energy (eV) Courtesy of T. Mazza, M. Meyer SQS (XFEL)

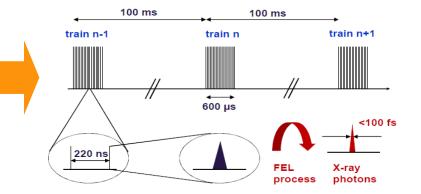

## EuropeanXFELDAQ challenge

- Readout rate driven by bunch structure

- 10 Hz train of pulses

- 4.51 MHz pulses in train

- Data volume driven by detector type

| Detector type       | Sampling | Data/pulse | Data/train | XFEL/sec | LCLS/sec |

|---------------------|----------|------------|------------|----------|----------|

| 1 Mpxl 2D camera    | 4.5 MHz  | ~2 MB      | ~1 GB      | ~10 GB   | ~300 MB  |

| 1 channel digitizer | 5 GS/s   | ~2 kB      | ~6 MB      | ~60 MB   | ~0.2 MB  |

#### Challenges:

- Per detector data volumes are large, sometimes very large

- Modular and electronic design of large detector front ends requires

- down stream image building, pixel reordering

- multiplexing of control signals

- Overcoming limitations in front end signal (pipeline) storage depth

- Gathering and storing of data from many detectors per experiment

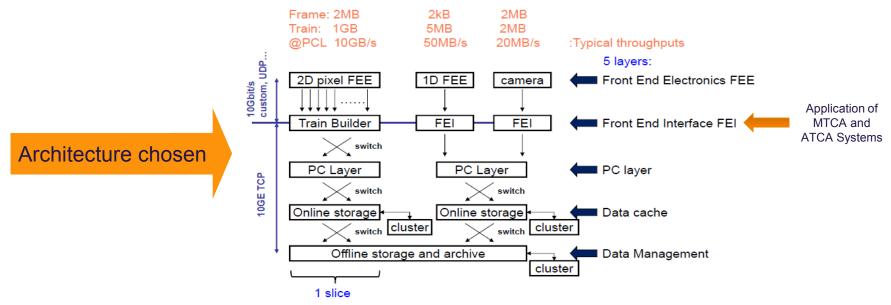

### **XFEL** Data management architecture

Large data volumes, their acquisition, storage and analysis and changing experiment configurations are issues the PBS system architecture is trying to solve

- Multiple layers with well defined APIs

- to allow insertion of new technology layers

- Multiple slices for partitioning and scaling

- camera sizes will increase and slice replication will be one solution

- Allow full speed write through to online storage, but discourage usage

- sometimes this capability is needed to understand measurement

- Enforce data reduction and rejection in all layers

- early data size reductions and data rejection are needed to reduce storage resources

Day one 2015/16 10PB offline disk storage.

Overview of MTCA.4 and ATCA based DAQ electronics and concepts for the XFEL

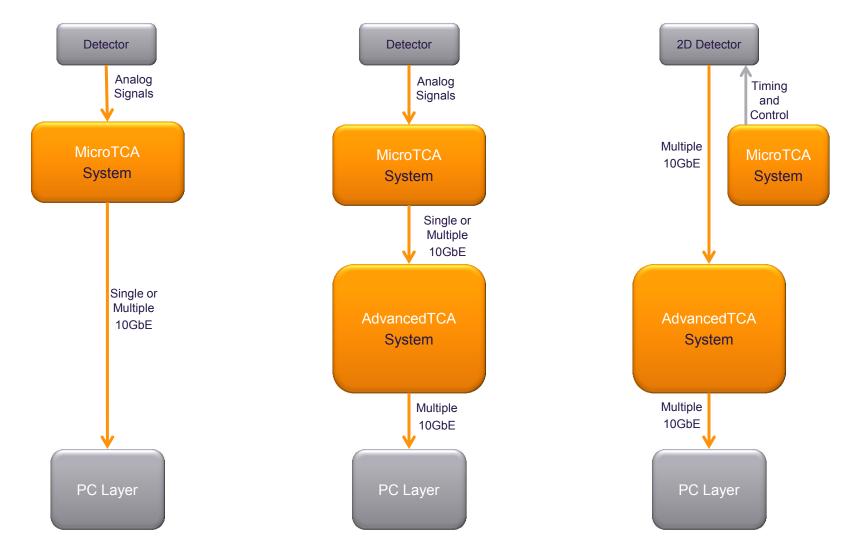

# **XFEL MTCA and ATCA Hardware and Concepts**

Overview of MTCA.4 and ATCA based DAQ electronics and concepts for the XFEL

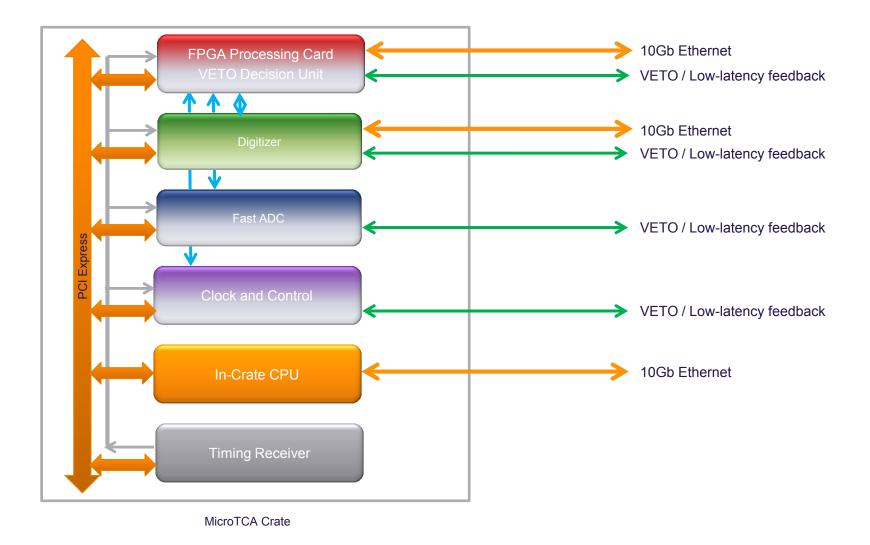

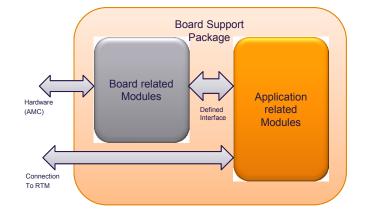

### **XFEL** MicroTCA Modules and Interfaces

11th December 2012 | MTCA Workshop @ DESY | Patrick Gessler (European XFEL)

### **XFEL** MicroTCA Modules and Interfaces

- Digitizers

- ADQ Family from SP Devices

- → 1.6GSPS / 14bit / 1 channel

- 2GSPS / 12bit / 4 channels

- → 4GSPS / 12bit / 2 channels

- → 7GSPS / 8bit / 1 channel

- 10GbE on front panel (SFP+)

- VETO / Low-latency feedback on front panel (SFP)

- Xilinx Virtex 6 FPGA

- FPGA access for custom algorithms

- Fast ADCs

- SIS8300 from Struck Innovative Systems

- 125MSPS / 16bit / 10 channels

- Xilinx Virtex 5 FPGA

- Full access to FPGA for custom firmware

- RTM support

- Used for signal shaping (pulse stretching)

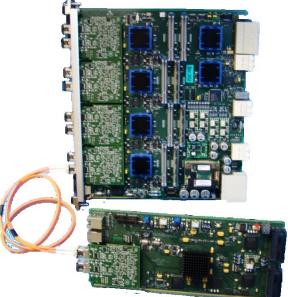

ADQ412-3G from SP Devices Sweden AB

(Peter Goettlicher, DESY)

### **XFEL** MicroTCA Modules and Interfaces

- Timing Receiver

- Development of DESY and Stockholm University

- Providing facility wide synchronized

- Clocks

- Triggers

- Machine information

- Clock and Control System

- Based on DAMC2 (DESY) and custom RTM (UCL)

- Synchronizes to the Timing Receiver

- Provides 16 outputs to a 1MPix 2D detector for

- Reference clock

- → Triggering

- Machine information

- VETO information

- For larger detectors multiple modules are used and synchronized in a crate

XFEL Timing Receiver (X2TIMER) (Stockholm University/DESY)

Clock and Control RTM (University College London)

DAMC2 (DESY, FEA)

#### European **XFEL** MicroTCA Modules and Interfaces

- FPGA Processing Card and

- **VETO Decision Unit**

- uTC Module from DMCS and DESY

- Planning to use the upcoming version (not shown)

- Provides

- Many input/output high-speed serial links ->

- Powerful FPGA

- **On-board Memory**

#### CPU

- Looking for a standard CPU (usually i7 based) with

- 10GbE (maybe dual) support

- Unfortunately not found yet!

- Currently

- Using Concurrent and ADLink CPUs (1GbE only)

- Investigating QorIQ based module from N.A.T. with -10GbE

High-performance DSP and FPGA board (uTC) (DMCS/DESY)

## **XFEL** ATCA Module and Interfaces

- Train Builder Blade

- Used for data concentration and processing

- Mostly 2D detectors, but also

- Digitizer data

- Module from Rutherford Appleton Lab (STFC)

- With FMC Modules from DESY/FEA

- Provides

- → Up to 8x 10GbE on SFP+

- → 4x Xilinx Virtex 5 FPGAs for processing

- DDR2 and QDR memories

- Crosspoint switch for flexible interconnections to Zone 3 connector used to

- Connect to further Train Builders

- IGbE interface to 5<sup>th</sup> FPGA for management and control

LPD Front-end module (FEM)

ASSOCIATION

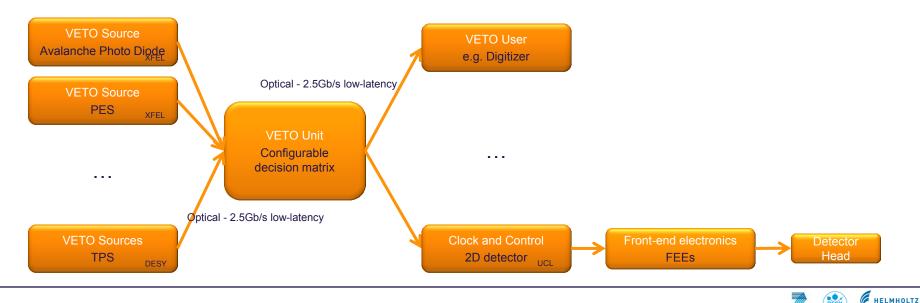

## European XFEL VETC

#### L VETO System for data reduction and memory optimization

- Optimize picture quality of 2D detectors

- Limited frame capacity in ASICs (~300-700 frames)

- Replace bad frames with new ones in ASIC before read out and transmission

- Data reduction

- Discard useless data before transmission

- Implementation

- FPGAs of diagnostics and detectors provide bunch information with low-latency

- Configurable central VETO unit per experiment decides on bunch quality

- FPGAs of detectors (maybe also diagnostics) receive the decision and react on it

- Using a common protocol with beam based feedback system

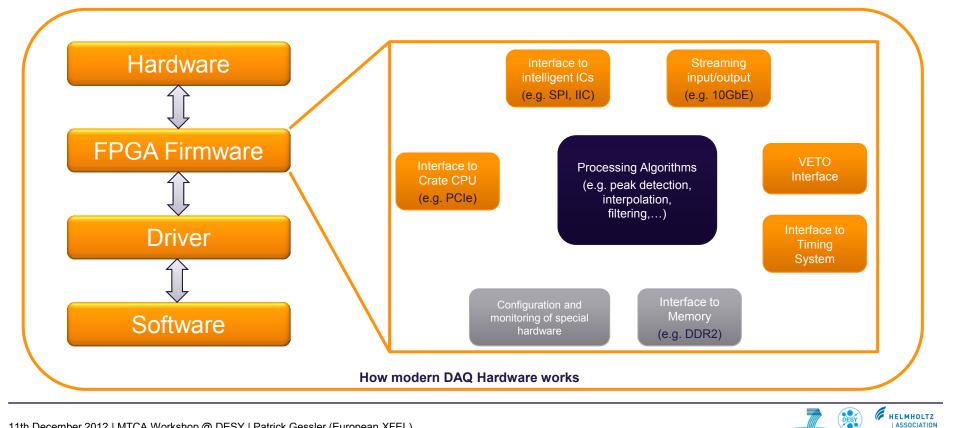

#### European FEL FPGA Framework - Overview

- Three important factors

- 100% of the DAQ related modules use FPGAs (Complex programmable logic)

14

- FPGA programming is time intensive and requires specialized people

- Many hardware is used in different projects by different people

#### **XFEL** FPGA Framework – Status (Low-Level)

- Implementation of low-level Framework ready

- Includes code from DESY, XFEL, Collaborators, Open platforms

- Tutorials had been done

- Improvements and adding of features ongoing

- Limited documentation available

- Software tools developed and available

- Register/Memory access with plotting

- Register and memory map generation

- Firmware upload

- PCle and driver management

| Proj.<br>Boa | ID<br>rd, Project : |                    | NoBoard,  | NoProject                                                               | About.                     |                                                 |        |  |  |

|--------------|---------------------|--------------------|-----------|-------------------------------------------------------------------------|----------------------------|-------------------------------------------------|--------|--|--|

| ile Operatio | ns                  |                    |           | Version Num                                                             |                            |                                                 |        |  |  |

| Type: App    | Open File           | Vie <u>w</u> Table | Gen. VHDL | Major 1 🔅                                                               | Мар                        | ) 🔅 Min                                         | or 0 🔹 |  |  |

|              |                     |                    |           | Type<br>Name<br>Datasize<br>Arraysize<br>Access<br>Register<br>Wordtype | Welc<br>1<br>1<br>WN<br>RE | WORD a<br>ome!<br>OACCESS<br>XTERNAL<br>ISIGNED |        |  |  |

| Board             | < Click to togale be | hunne Daniel | and Anni  |         | Open file        | Board Info |  |  |

|-------------------|----------------------|--------------|-----------|---------|------------------|------------|--|--|

| Doard             | Click to toggie be   | eween board  | and App:  |         | Obsu me          | geara inte |  |  |

| Device:           |                      |              |           |         | Open <u>D</u> ev | About      |  |  |

| Board/Application | Info                 |              |           | -       |                  |            |  |  |

| Board             |                      |              | Board Cor | ntact [ |                  |            |  |  |

| App               |                      |              | App Cont  | act [   |                  |            |  |  |

| ist Entries       |                      | PCle Option  | 15        |         |                  |            |  |  |

|                   |                      | RESET        | Bar:      | 0       | Data Mode        | 32 -       |  |  |

|                   |                      | Entry Value  | 15        |         | 1                |            |  |  |

|                   |                      |              | Addr:     | 0       |                  |            |  |  |

|                   |                      | Size         |           |         | Offset:          | 0 0        |  |  |

|                   |                      | Mask         |           |         | Shift:           | 0 1        |  |  |

|                   |                      | Data:        | 0x        |         | -                | Hex -      |  |  |

|                   |                      |              |           |         |                  |            |  |  |

|                   |                      | Read         | i Write   |         | Plot             | List       |  |  |

|                   |                      | Script Oper  |           |         |                  |            |  |  |

|                   |                      | Script:      |           |         |                  |            |  |  |

|                   |                      | Choose S     |           | Edit S  |                  | Bun Script |  |  |

| Output       Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -        | ile Edit View Project Source Process Tools Win |          | -                        |               |       |            |           |        |      |         |       |       | 8       | 쏊  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------|----------|--------------------------|---------------|-------|------------|-----------|--------|------|---------|-------|-------|---------|----|

| Wexet         Binglementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | N. a X 0 0 X 1 9 1                             | P        | 8 8                      | 1 3 2         | 13    | 8 0 9      | P N?      | 1      | T    | 1 0     |       |       |         |    |

| Werker         Souther & Bindeline         Bindeline           Werker         Herecky         Souther                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Des      | ign HDØX                                       | 41       | 20                       | const         | ant   | HORD PRO   | I PROFT   |        |      | atura   | 1     | 20.   |         |    |

| Wenchy         9         20         constant WOD_TAG_TCK         i natural i = 22;           Wenchy         9         constant WOD_TAG_TWS         i natural i = 22;           Wenchy         constant WOD_TAG_TWS         i natural i = 23;           Wenchy         constant WOD_TAG_TWS         i natural i = 23;           Wenchy         constant WOD_TAG_TWS         i natural i = 23;           Wenchy         constant WOD_TAG_TWS         i natural i = 25;           Wenchy         si natural i = 25;         constant WOD_TAG_TWS         i natural i = 25;           Wenchy         si natural i = 25;         constant WOD_TAG_TWS         i natural i = 25;           Wenchy         si natural i = 25;         constant WOD_TAGATY         i natural i = 25;           Wenchy         si natural i = 26;         constant WOD_TAGATY         i natural i = 25;           Wenchy         si natural i = 26;         constant WOD_TAGATY         i natural i = 26;           Wenchy         si natural i = 26;         constant WOD_TAGATY         i natural i = 26;           Wenchy         si natural i = 26;         constant WOD_TAGATY         i natural i = 26;           Wenchy         si natural i = 26;         si natural i = 26;         i natural i = 26;           Wenchy         si natural i = 10;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 117      | View:                                          |          |                          |               |       |            |           |        |      |         |       |       |         |    |

| Generod HANTLUS                                                                                                         |          | Historethu                                     | <b>F</b> |                          |               |       |            |           |        |      |         |       |       |         |    |

| ActivitySo 391136       Constant WOD_TAC_TDI : instural := 25;         ActivitySo 391036       ActivitySo 340, TOP Behavioral (ENT SG 35, TOP SG 340, TOP                                                                                                                                                                                                                                                                                  | 8        |                                                |          |                          |               |       |            |           |        |      |         |       |       |         |    |

| Constant WORD_ATAG_TOO : in Adult ::= 25;<br>Constant WORD_ATAG_TOO : | G        |                                                |          |                          |               |       |            |           |        |      |         |       |       |         |    |

| <pre>Solution State Stat</pre>                                                                                        | un       |                                                | 10       |                          |               |       |            |           |        |      |         |       |       |         |    |

| <ul> <li>S. NST_BOADD_BET_GOADS_AKE_NERT</li> <li>S. NST_BOADD_BET_GOADS_AKE_NERT</li> <li>S. NST_BOADD_BET_GOADS_AKE_NERT</li> <li>S. NST_BOADD_COOK (DATA AND NOT DOADSD_NOT DOADSD_</li></ul>                                                                                                    | -        |                                                |          |                          | CONSC         | ant   | NORD_OTA   | 3_100     |        | • •  | acura   |       | 20,   |         |    |

| Image: Solution of the                                                                                                                      |          |                                                |          |                          |               |       |            | 17.1      |        |      | 114     |       | 1     |         |    |

| Image: Solution: Soluti                                                                                                                     | <i>a</i> |                                                | 10       |                          |               |       |            |           |        |      |         |       |       |         |    |

| Wit_coop         Wit_coop         Nonp_coop         Xit_coop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | ii1 - ii_base - ARCH (PKG_II.vhd)              |          |                          |               |       |            |           |        | 1.3  |         |       |       |         |    |

| Wil_DOB         NonBOADQ_PREION         22         11_UOBD         NON_BOADQ_PREION         22         11_UIDB           Wil_DOB         NON_BOADQ_PREION         22         11_UIDB         NON_BOADQ_PREION         22         11_UIDB           Wil_DOB         NON_BOADQ_PREION         22         11_UIDB         NON_BOADQ_PREION         22         11_UIDB           Wil_DOB         NON_BOADQ_PREION         22         11_UIDB         NON_BOADQ_PREION         22         11_UIDB           Wil_DOB         NOND_DOADQ_PREION         22         11_UIDB         NOND_DOADQ_PREION         22         11_UIDB           Wil_DOB         NOND_DOADQ_PREION         23         11_UIDB         NOND_DOADQ_PREION         22         11_UIT_NOND           Wil_NOND_NOND_DOADQ_PREINT         11_UIDB         NOND_DOADQ_PREINT         11_UIT_NOTD         11_UIT_NOND           Wil_NOND_CLL_ST         11_UIDB         NOND_CLL_ST         1_UIT_NOND         NOND_CLL_ST         1_UIT_NACCESS           Wil_NOND_NOND_CLL_ST         1_UIT_NOND         NOND_CLL_ST         1_UIT_NACCESS         1_UIT_NACCESS           Wil_NOND_NOND_NOND_NOND_NOND_NOND_NOND_NON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Ø        | INST_CLK_DIV_CONFIG - ENT_SPI - Be             | 4        |                          |               |       |            |           |        |      |         |       |       |         |    |

| Wisj Acci. eMr Acc. Acc. MKR U         42         VII_ORD _ NOR_DARD_M_VENION         12, 1, 1, VII_MACC           Wisj McL. eMr Acc. Acc. MKR U         43         VII_ORD _ NOR_DARD_M_VENION         12, 1, 1, VII_MACC           Wisj McL. eMr Acc. MKR MKR Acc. Acc. MKR MKR Acc. MC _ MKR Acc. MKR _ MKR Acc. MC _ MKR Acc. MKR _ MKR Acc. MC _ MKR Acc. MKR Acc. MC _ MKR Acc. MKR Acc. MKR Acc. MC _ MKR Acc. MKR Acc. MC _ MKR Acc. MKR Ac                                                                                                                                                                                                                               |          |                                                | -        |                          |               |       |            |           |        |      |         |       |       |         |    |

| Image design module is selected.         Start @ Design Differs       File / Lishmt / / gestalter / fpss/153391_START VIEL_NORD_ NORD_DIGLAINC.       Image design module is selected.         Start @ Design Differs       File / Lishmt / / gestalter / fpss/153391_START VIEL NORD_ NORD_DIGLAINC.       Image design module is selected.         Start @ Design Differs       File / Lishmt / / gestalter / fpss/153391_START VIEL NORD_ / TESS95_START VIEL NORD_ NORD_DIGLAINC.       Image design module is selected.         Start @ Design Differs       File / Lishmt / / gestalter / fpss/153391_START VIEL NORD_ TESS START BIASHS       Image design module is selected.         Start @ Design Differs       File / Lishmt / / gestalter / fpss/153391_START VIEL NORD_ TESS START BIASHS       Image design module is selected.       Image design module is selected.         Start @ Design Differs       File / Lishmt / / gestalter / fpss/153391_START VIEL NORD_ TESS START BIASHS       Image design module is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |                                                | 76       |                          |               |       |            |           |        |      |         |       |       |         |    |

| i Sund Lu, Terrat, LL, ARC, Moz         i Sund Lu, Terrat, And Moz         i Sund Lu, Terrat, Sund Lu, Terrat, Sund Lu, Sund Lu                                                                                                                                                                                 |          |                                                | -        |                          |               |       |            |           |        | ON   |         |       |       |         |    |

| 0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                                | 10       |                          |               |       |            |           |        |      |         |       |       |         |    |

| Station       result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                                | 76       |                          | VII_W         | ORD   | , WORD_B   | DARD_TO_  | PROJ   |      |         | 32    | , 1 , | VII_W   | 10 |

| Static Design       Price       Ubrakes         Monthlinerseetinge       - File / distant // gealer / figs/15530 _ File / fi                                                                                                                                                                                                                                                                                                                                                                  |          |                                                |          | 45                       |               |       |            |           |        |      |         |       |       |         |    |

| Sussion enzy.ard       witz.comp.sc.2ss.       , 1, 1, 1, 1, 1, 1, 2000         Sussion enzy.ard       witz.comp.sc.2ss.       , 1, 1, 1, 1, 1, 1, 2000         Sussion enzy.ard       witz.comp.sc.2ss.       , 1, 1, 1, 1, 1, 1, 2000         Sussion enzy.ard       witz.comp.sc.2ss.       , 1, 1, 1, 1, 1, 1, 2000         Witz.sex.ard       wood_sc.2ss.       , 1, 1, 1, 1, 1, 1, 2000         Sussion enzy.ard       witz.sex.ard       , 1, 1, 1, 1, 1, 2000         No Processes Running       vitz.sex.ard       , 1, 1, 1, 1, 1, 1, 2000         Sussion enzy.ard       sex.ard       , 1, 1, 1, 1, 1, 2000         Sussion enzy.ard       sex.ard       sex.ard         Sussion enzy.ard       sex.ard       sex.ard       sex.ard <td></td> <td></td> <td>0</td> <td>46</td> <td>VII_W</td> <td>ORD</td> <td>, WORD_C:</td> <td>LK_MUX</td> <td>,</td> <td>2</td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |                                                | 0        | 46                       | VII_W         | ORD   | , WORD_C:  | LK_MUX    | ,      | 2    |         |       |       |         |    |

| Will_NOBD_JOBC_MIA       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                                                | 0        | 47                       | VII_W         | ORD   | , WORD_C:  | LK_RST    | ,      | 1    |         | 1 ,   | VII_P | ACCESS  |    |

| 49         VII_AREA, NOND_BFL_DIV         8, 1024, VII_ARCCES           49         VII_AREA, NOND_BFL_DIV         8, 1024, VII_ARCCES           50         VII_AREA, NOND_BFL_DIV         8, 1024, VII_ARCCES           50         VII_AREA, NOND_BFL_DIV         9, 1024, VII_ARCCES           50         VII_AREA, NOND_BFL_DIV         9, 2, 2, 5536, VII_ARCCES           51         VII_AREA, NOND_BFL_DIV         1, 1, VII_ARCCES           52         VII_ORD, NOND_IORDINAT_NEC, I, 1, VII_ARCCES         54, VII_NORD, NOND_IORDINAT_NEC, I, 1, VII_ARCCES           53         VII_ORD, NOND_IORDINAT_NEC, I, 1, VII_ARCCES         55, VII_ARCCES         54, VII_NORD, NOND_IORDINAT_NEC, I, 1, VII_ARCCES           54         VII_ORD, NOND_IORDINAT_NEC, I, 1, VII_ARCCES         55, VII_ARCCES         54, VII_NORD, NOND_IORDINAT_NEC, I, 1, VII_ARCCES           55         VII_ORD, NOND_IORDINAT_NEC, I, 1, VII_ARCCES         54, VII_NORD, NOND_IORDINAT_NEC, I, 1, VII_ARCCES           56         VII_ORD, NOND_IORDINAT_NEC, I, 1, VII_ARCCES         55, VII_ARCCES         54, VII_NOND, NOND_IORDINA, NOND_IORD, NOND_IORDINA, NONDANA, NONDANA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |                                                | 0        | 48                       | VII_W         | ORD   | , WORD_AI  | DC_ENA    |        | 1    |         |       |       |         |    |

| Source       50       VII_AREA , KNED_SPL_ADC , 8, 1024 , VII_ARCCESS         No bingle design module is selected.       51       VII_AREA , KNED_DADUZ , 22, 4533 , VII_ARCCESS         Source design module is selected.       52       VII_MORD , NORD_IDELAY_INC , 1 , 1 , VII_MACCESS         Source design module is selected.       53       VII_MORD , NORD_IDELAY_INC , 1 , 1 , VII_MACCESS         Source design module is selected.       54       VII_MORD , NORD_IDELAY_INC , 1 , 1 , VII_MACCESS         Source design module is selected.       55       VII_MORD , NORD_IDELAY_INC , 1 , 1 , VII_MACCESS         Source design module is selected.       55       VII_MORD , NORD_IDELAY_INC , 1 , 1 , VII_MACCESS         Source design module is selected.       54       VII_MORD , NORD_IDELAY_INC , 1 , 1 , VII_MACCESS         Source design module is selected.       55       VII_MORD , NORD_IDELAY_INC , 1 , 1 , VII_MACCESS         Source design module is selected.       55       VII_MORD , NORD_IDELAY_INC , 1 , 1 , VII_MACCESS         Source design module is selected.       55       VII_MORD , NORD_IDELAY_INC , 1 , 1 , VII_MACCESS         Source design module is selected.       56       VII_MORD , NORD_IDELAY_INC , 1 , 1 , VII_MACCESS         Source design module is selected.       56       VII_MACCESS , 59ACE, BOARD.vHod X ( ) , 1 , 1 , 1 , VII_MACCESS         AddRINS/Regleating reseleting e , File / (Lishmt/A/geselat//Spa/TERS)SE_TRATR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                                                |          | 49                       | VII_A         | REA   | , WORD_SI  | VIG_IS    |        | 8    | , 102   | 4 ,   | LII'  | ACCESS  |    |

| VII_AREA , AREA_DDR2 , 32,65536 , VII_KACCESS         No single design module is selected         No single design module is selected         Stat       ** Design Utilities         Stat       ** Design Utilities         MaxXXIIIS/irrojectMgmt - File /diskmt/a/gesaler/fpga/158308_STANTD/trank/DMT_SI38306_DTP_vhdl.pc) is missing.         MaxXXIIIS/irrojectMgmt - File /diskmt/a/gesaler/fpga/158308_STANTD/trank/DMT_SI38306_DTP_vhdl.pc) is missing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | - Manage and a                                 |          | 5.0                      | VII_A         | REA   | , WORD_SI  | PI_ADC    | ,      | 8    | , 102   | 4 .   | UII.  | ACCESS  |    |

| Start       ***       Design Utilities       Files       Utilition Discretion       Start       ***       Start       Start       Star                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | 4                                              |          | 51                       |               |       |            |           |        |      |         |       |       |         |    |

| Start       **       Design Utilities       **       Start       **       Design Utilities       **       Total and the selected.       **       Start       **       Design Utilities       **       Total and the selected.       **       Start       **       Design Utilities       **       Total and the selected.       **       Total and the selected.       **       Total and the selected.       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **       **                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          | No Processos Pupping                           |          | 52                       |               |       |            |           |        |      |         |       |       |         |    |

| No single design module is selected.         54         VIT_DORDHORD_IDELAY_INC         1         1         VIT_ACCES           Start         Ht         Design         This         VIT_HORDHORD_HORD_IDELAY_INC         1         1         VIT_ACCES           Start         Ht         Design         This         This         Unit source         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 <t< td=""><td>-</td><td>C2 No Processes Running</td><td></td><td></td><td>VII_W</td><td>ORD</td><td>, WORD_II</td><td>DELAY_SE</td><td>L</td><td></td><td>5,</td><td>1</td><td>, VI</td><td>I_WACCI</td><td>ES</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -        | C2 No Processes Running                        |          |                          | VII_W         | ORD   | , WORD_II  | DELAY_SE  | L      |      | 5,      | 1     | , VI  | I_WACCI | ES |

| Besign Utilities     Sont Int Design To Picks     Miss To Durates     mining Rie Generated X is ENT BOARD.vid X is Pick_ADDRESS_SPACE_BOARD.vid X     mong Rie Generated X is ENT_BOARD.vid X is Pick_ADDRESS_SPACE_BOARD.vid X     mong Rie Generated X is ENT_BOARD.vid X is Respectively.     Sont Internet in the Additional System of Additingenetic System of Additional System of Additional System of Addit                                                                                                   | met.     | No single design module is selected.           |          |                          |               |       |            |           |        |      |         |       |       |         |    |

| Start int Design C Ries D Ubravies       mming Rie Generated X is DAAD.vid                                                                                                                                      | * **     | * Se Design Utilities                          |          |                          |               |       |            |           | 161    | 1    | - 1     |       | 1.11  |         | -  |

| Start (ng Design ) Ries () Ubranes     mining Rie Generated) X () EXT_BOARD.vid X () RKG_ADDRESS_SPACE_BOARD.vid X     Gravita     Console     Console     File / diskmt/a/gesaler/fpga/TES305_STARTO/trusk/DMT_TES305_DTP_vidpt) is missing.     Sature in the interview of the interview gesaler/fpga/TES305_DTATO/trusk/DMT_TES305_DTP_vidpt) is missing.     Sature interview of the interview gesaler/fpga/TES305_DTATO/trusk/DMT_TES305_DTP_vidpt) is missing.     Sature interview of the interview gesaler/fpga/TES305_DTATO/trusk/DMT_TES305_DTP_vidpt) is missing.     Sature interview of the interview gesaler/fpga/TES305_DTATO/trusk/DMT_TES305_DTP_vidpt) is missing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 92C      |                                                |          |                          | UTT M         | ORD   | WORD DI    | DOT MACT  | C 100  |      |         | 20    | 1     | UTT MRD | -  |

| Consol<br>AUXANING/Frojectkyme - File /diskmt/a/genaler/fpga/IIS330_STAAT09/trank/EMT_IIS330_T00_whdi.prj is missing.<br>AUXANING/Frojectkyme - File /diskmt/a/genaler/fpga/IIS330_STAAT09/trank/EMT_IIS330_T00_whdi.prj is missing.<br>AUXANING/Frojectkyme - File /diskmt/a/genaler/fpga/IIS330_STAAT09/trank/EMT_IIS330_T00_whdi.prj is missing.<br>AUXANING/Frojectkyme - File /diskmt/a/genaler/fpga/IIS330_T00_whdi.prj is missing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                                                |          | <ul> <li>10-3</li> </ul> |               |       |            |           |        |      |         |       |       |         | •  |

| <pre>AMANINGSTrojectMpnt = 11e /diskmc/a/gesaler/fpg/161939 578ATUP/trusk/DTT_SIS300_70p_vhdl.pt is missing.<br/>AMANINGSTrojectMpnt = 71le /diskmc/a/gesaler/fpg/1619300_STAATUP/trusk/DTT_SIS300_70p_vhdl.pt is missing.<br/>AMANINGSTrojectMpnt = 71le /diskmc/a/gesaler/fpg/1619300_STAATUP/trusk/DTT_SIS300_70p_vhdl.pt is missing.<br/>AMANINGSTrojectMpnt = 71le /diskmc/a/gesaler/fpg/1619300_STAATUP/trusk/DTT_SIS300_70p_vhdl.pt is missing.</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | Start 🔍 Design 🕥 Files 🚺 Libraries             | mmir     | ig File G                | enerated) >   | (     | ENT_BOARD  | D.vhd 💥   | PK     | G_AL | DRESS_  | SPACE | BOAR  | D.vhd 💢 | 1  |

| AMARINETsejestejes - File /diakent/a/genale//pp//TESD00_TRANTO/tenk/IMT_IESD00_TO_F.di/jrj is mission-<br>wamminersjestejestejestejestejestejestejesteje                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Con      | sole                                           |          |                          |               |       |            |           |        |      |         |       |       |         | 20 |

| ARADINISTojectujet - File /diskmt/a/gealer/fpg/TESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/trank/ETA/ESS02_ETARTO/TRANE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | • 1      | ARNING:ProjectMont - File /disknnt/a/gessler   |          | /SIS83                   | 00 STARTUP    | trunk | VENT SIS83 | 00 TOP vh | dl.pri | is   | missing |       |       |         |    |

| AVABNING:ProjectWgmt - File /diskmot/a/gessler/fpga/SIS#300_STARTUP/trunk/ENT_SIS#300_TOP_ohdl.prj is missing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |                                                |          |                          |               |       |            |           |        |      |         |       |       |         |    |

| • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                                                |          |                          |               |       |            |           |        |      |         |       |       |         |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Ty       | ARNING:ProjectMgmt - File /diskmnt/a/gessler   | /tpga    | /SIS83                   | 00_STARTUP/   | trun) | /ENT_SIS83 | 00_TOP_vh | dl.prj | 15   | missing | 8     |       |         |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                                                |          |                          |               |       |            |           |        |      |         |       |       |         | _  |

| 🛓 Console 🔽 Errors 🧘 Warnings 🛄 Tcl Console 🙀 Find in Files Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4        | 1                                              |          |                          |               |       |            |           |        |      |         |       |       | _       |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | Console 💟 Errors 🔟 Warnings 🔛 Tcl Console      | 26       | Find in                  | Files Results |       |            |           |        |      |         |       |       |         |    |

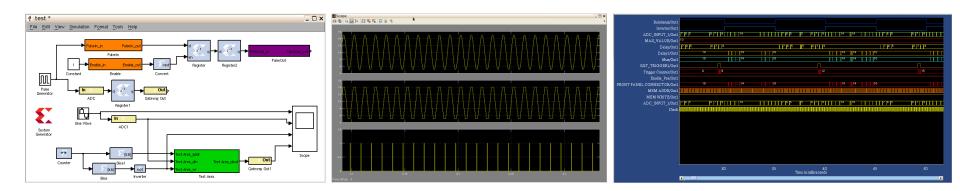

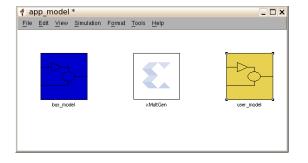

### **XFEL** FPGA Framework – Status (High-Level)

- We are in prototyping stage

- Tests of features like

- Automatic register and memory mapping

- Integrated image generation and deployment

- Algorithms for detector signal handling

- Library organization and distribution

- Successfully generated firmware for our digitizers

- Plan to consolidate and then collaborate with similar Framework developed for Astrophysics (e.g. SKA) within EU FP7 CRISP project

Time for questions and discussion...