### **BAM Electronics**

## **Overview & Specifications**

#### Marie Kristin Czwalinna

BAM Generation 3 - Overview on Specifications for Electronic System

Advanced Techniques in LLRF control for XFEL - Collaboration Workshop

19. - 21. February 2013, Otwock-Swierk

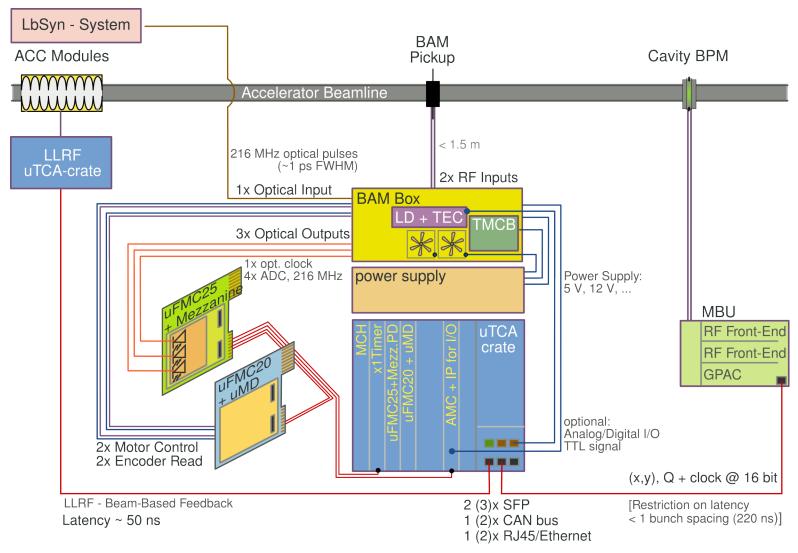

# **System Overview & Interfaces**

## Interfacing: open questions

#### > uFMC25 ↔ MD22

- communication via standard backplane

- which ports

- No. of signals for controlling both motors and reading back encoder data

- MD22: control of 2 Stepper motors + read-out of position encoder: EnDat2.2 data format

- data rates: 10 Mbit/sec

#### > uFMC25 ↔ I/O cards

- Option: control of optical switch (e.g. via TTL signal)

- > via backplane → which ports

- > Or: with RTM card

- synchronised to machine trigger

## uFMC25 + mezzanine & PD: open questions

### > Challenge:

- Conversion of laser pulses (~ps FWHM) to electr. Signal (clear pulse w/ flat baseline)

- Sampling rate of 216 MHz (laser rep. Rate):

- > 2 channels

- 2x ADCs per channel (peak & baseline)

### Requirements & Current Status:

PD input:

- PD output power level wrt optical input power

- set diff.. amplifier according to expected opt.power wrt. PD

- > characterisation of pulses (pronounced separation between peak & baseline)

- amplitude jitter at peak & baseline

- ADC performance:

- > dynamic range

- > buffer current for optimal SFDR

- > employment of time shifters

- > SNR

- ENOB

- > max. clock jitter wrt to full BW signals

- amplitude jitter (peak & baseline)

### Firmware & Server

#### Basic firmware

- clock shifter

- communication: PCI, IPMI

- read-out of ADC1-4

## Data processing in firmware

- divider implemented

- ratio A to B implemented

- sampling point

- calibration of unscaled data

- read-out of BPM data → correction of data

## Connection to timing system and remote access

- x2timer clock & trigger signal received

- stable trigger implemented

- remote trigger shift

- ....

# **Rough timeline**

- Boards ready for installation

- FLASH /FLASH II:

- > 1x needed June 2013

- » Test system for BAM.18(15)ACC7

- » Server development & tests

- at least 2 more until August/September 2013

- » BAM.3DBC2 & 4DBC3 → connection to LLRF for Feedback

- > 3 more by end of this year

- » BAM.1UBC2 and 2x FLASH II BAMs

- Europ.XFEL:

- > 1x for September 2014

- » XTIN: BAM.47.I1