## **PXD TB Status**

**C.** Marinas for the DEPFET Collaboration

cmarinas@uni-bonn.de

#### Introduction

- VXD common test beam in January 2014 (4 weeks)

- Small sector of the close to final prototype detectors and ASICs

2 PXD half ladders + 4 SVD single module layers

- Complete VXD readout chain: HLT, monitoring, event building, PocketDAQ

- CO<sub>2</sub> cooling, slow control, environmental sensors

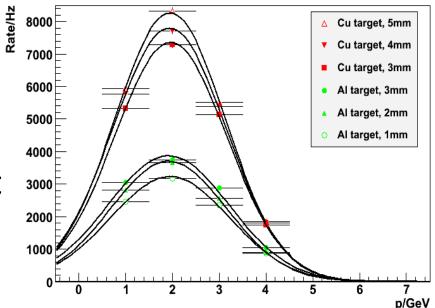

- Illumination with (up to) 6 GeV e<sup>-</sup> under solenoid magnetic field (PCMAG)

- Alignment, tracking algorithms, ROI

<u>Goal</u>: System integration test

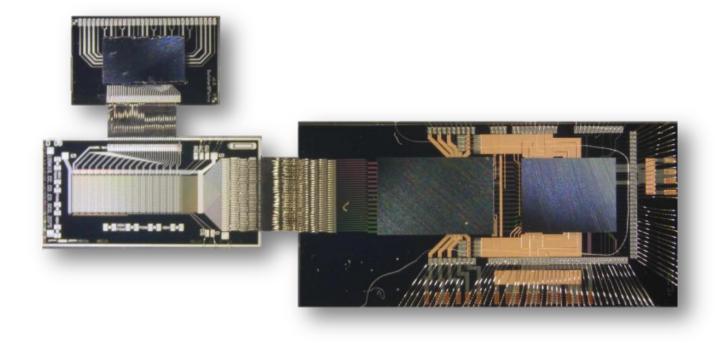

#### Long PXD6 – TB Devices Under Test

#### **Sensor Description**

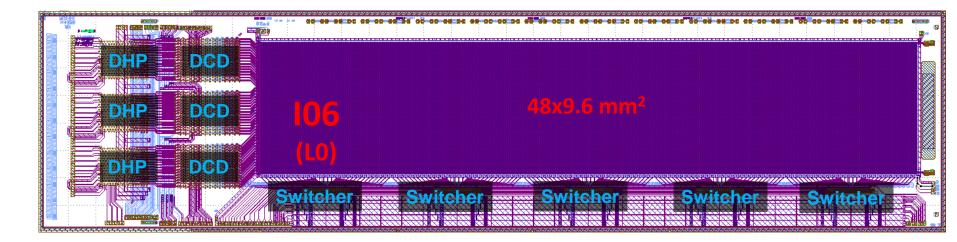

• 106

Belle II Standard Design 50x75 μm<sup>2</sup> 768 drain lines (256x3 DCD/DHP) 160 gate/clear lines (5 Switcher)

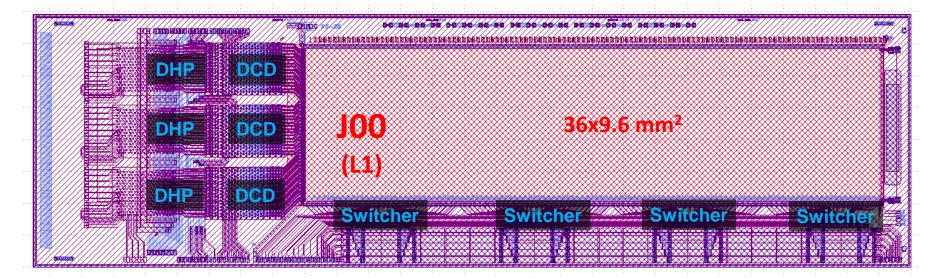

• J00

Capacitive Coupled ClearGate 50x75 μm<sup>2</sup> 768 drain lines (256x3 DCD/DHP)

120 gate/clear lines (4 Switcher)

• ASICs

DCDBv2, DHP0.2, SwitcherB1.8G (in non gated mode)

#### From this...

#### ... to this

+ all the DAQ, SlowControl, Cooling, PS, ...

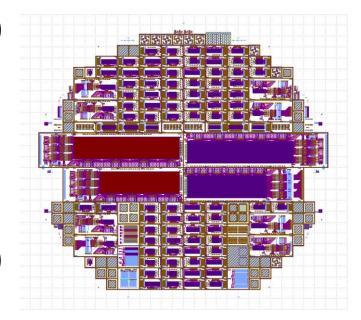

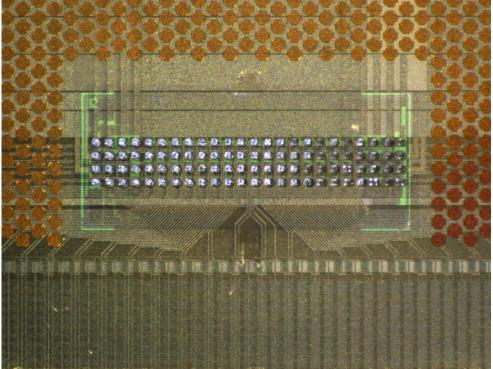

Belle II standard pixel cell design Close to final versions of ASICs 640x192 pixels matrix 50x75 μm<sup>2</sup> pitch

Final flip chip process

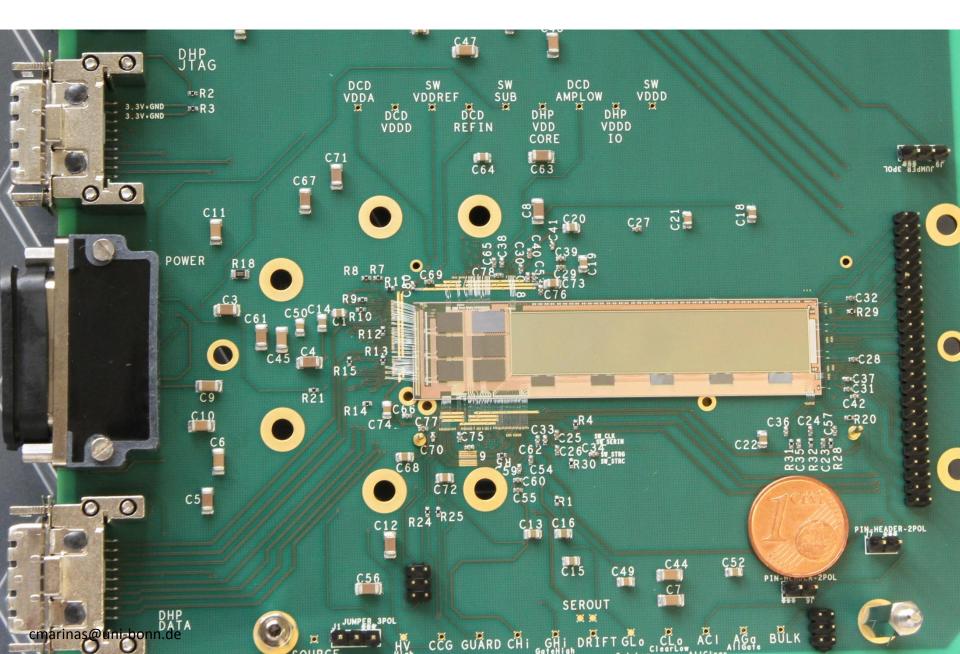

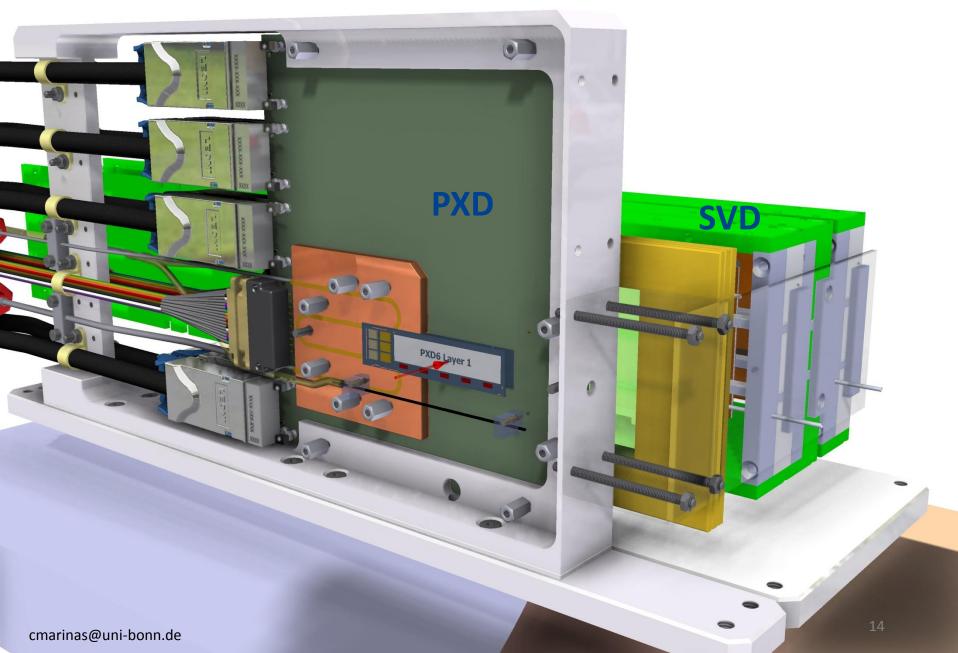

#### **PXD6 on Hybrid6**

#### **Damaged Detector**

- Differential to single ended converter chip has been operated at 3.3 V

- The Switcher technology is designed to be operated at 1.8 V

- Protection diodes were activated

- Switchers did not show any power consumption (current flow)

- ASICs were powered through the JTAG bus/pins

- Switchers has been damaged → need to be replaced

Rework at Finetech Switchers being replaced Expected end of this week

EMCM with PXD6 and Hybrid 5.0 as back up

cmarinas@uni-bonn.de

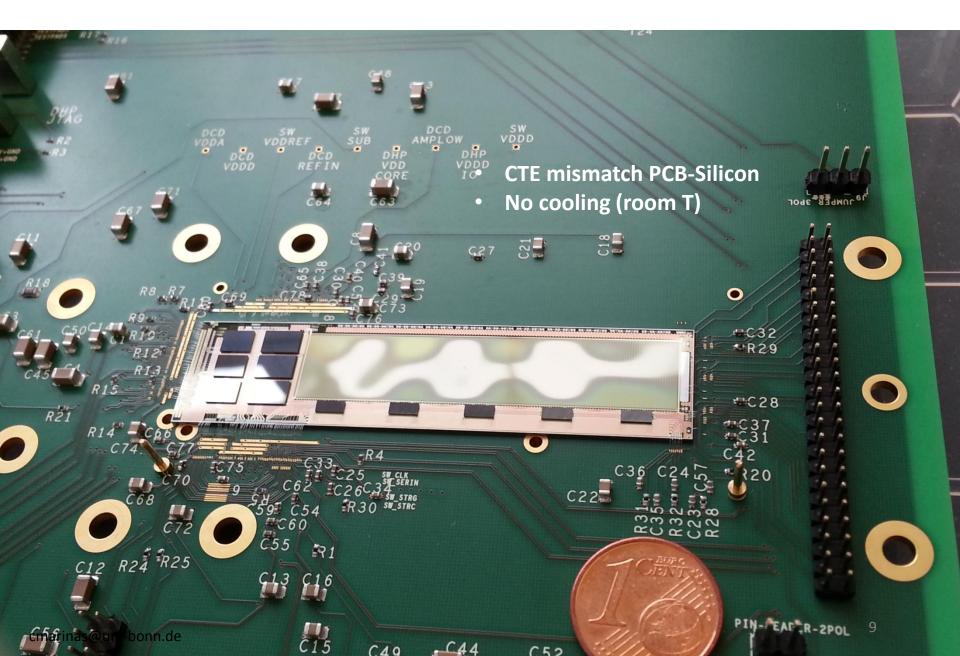

#### **Sensor Deformation**

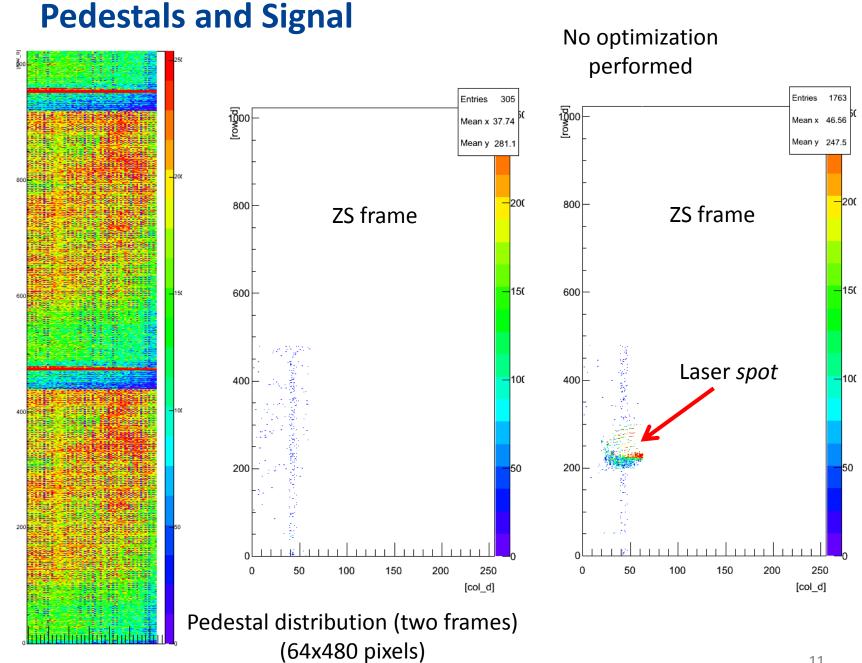

#### Laser Setup PXD6-J00

Temperature stable at 20 °C

13

T

cmarinas@uni-bonn.de

#### Schedule

| 14. Okt 13 | 42 |                                | CMS TrkPh2-J |      |             |              |              |            |       |          |

|------------|----|--------------------------------|--------------|------|-------------|--------------|--------------|------------|-------|----------|

| 21. Okt 13 | 43 |                                | CLICpix      |      |             | CALICE AHCAL | LorAngle     |            |       | 0        |

| 28. Okt 13 | 44 | no beam 2/11/2013              | CMS FPIX     |      |             | GSI-DIRC     | LorAngle     |            |       |          |

| 04. Nov 13 | 45 |                                | CMS Pix      |      |             | GSI-DIRC     | LorAngle     |            |       | n        |

| 11. Nov 13 | 46 |                                | ALICE ITS    |      | APIX PPS    |              |              |            |       |          |

| 18. Nov 13 | 47 |                                | CMS TrkPh2-E |      | APIX PPS    |              |              |            |       | C<br>C   |

| 25. Nov 13 | 48 |                                | CMS TrkPh2   |      | APIX PPS    |              |              |            |       | e        |

| 02. Dez 13 | 49 |                                | CLICpix      |      | APIX PPS    |              |              | d          |       |          |

| 09. Dez 13 | 50 |                                | SiPM         |      |             | CALICE AHCAL |              |            |       |          |

| 16. Dez 13 | 51 | End of beam 19/12/2013<br>0800 |              |      |             |              |              |            |       |          |

| 23. Dez 13 | 52 |                                |              |      |             |              |              |            |       |          |

|            |    |                                |              |      | 2014        |              |              |            |       |          |

| 6-Jan-14   |    |                                | FCAL         |      |             | CALICE AHCAL | Belle II VXD |            |       |          |

| 13-Jan-14  | 3  |                                | FCAL         |      |             | CALICE AHCAL | Belle II VXD |            |       |          |

| 20-Jan-14  | 4  |                                | SBS GEM      |      | APIX 3D     |              | Belle II VXD |            |       |          |

| 27-Jan-14  | 5  |                                | SBS GEM      | -    | DIAPIX      |              | Belle II VXD |            |       |          |

| 3-Feb-14   | 6  |                                | LHCb VELO    |      | MuPix       |              | LorAngle     |            |       | ğ        |

| 10-Feb-14  | 7  |                                | LHCb VELO    |      | ATLAS Strip |              |              |            | PLUME | 5        |

| 17-Feb-14  | 8  |                                | ATLAS Lucid  |      | ATLAS Strip |              |              | LCTPC Time |       | Announce |

| 24-Feb-14  | 9  |                                |              | SiPM | APIX PPS    |              |              | LCTPC Time |       | Ö        |

| 3-Mar-14   | 10 |                                | CMS TrkPh2-E |      | APIX PPS    |              |              |            |       | d        |

Test beam preparations at the experimental hall started end of November Two months of 'test beam-like' (*sort of*) life

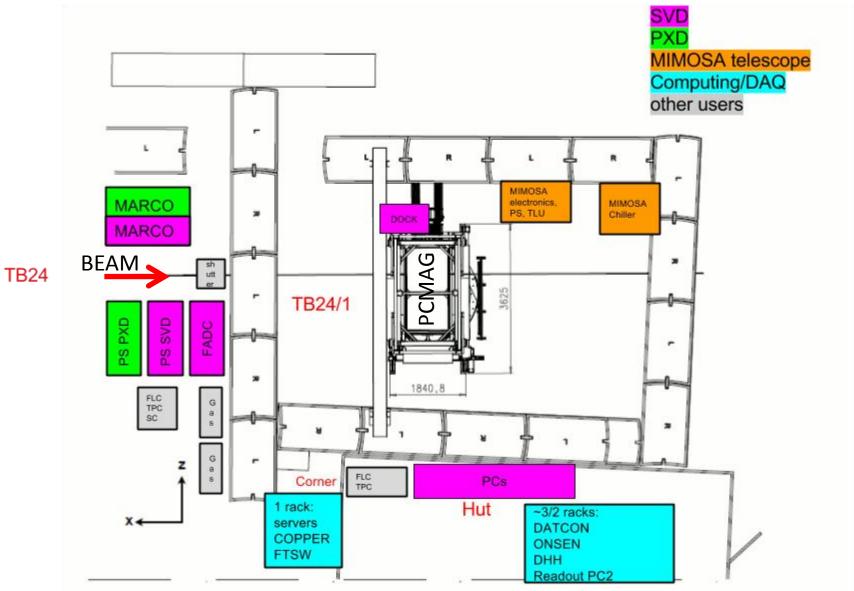

#### **General Layout**

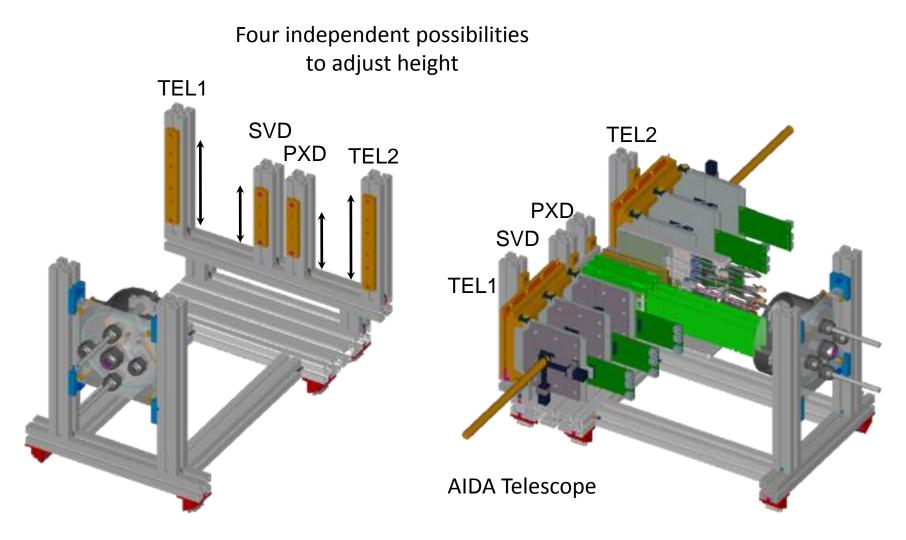

#### **Mechanical Set-up**

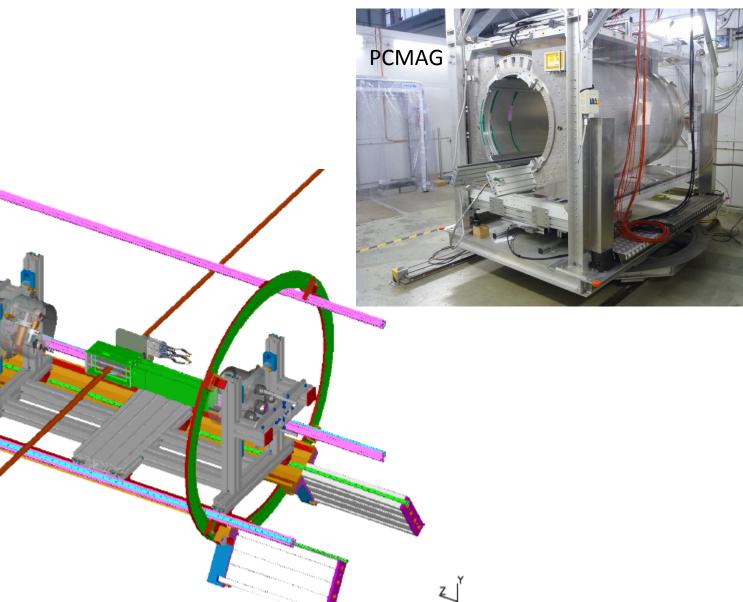

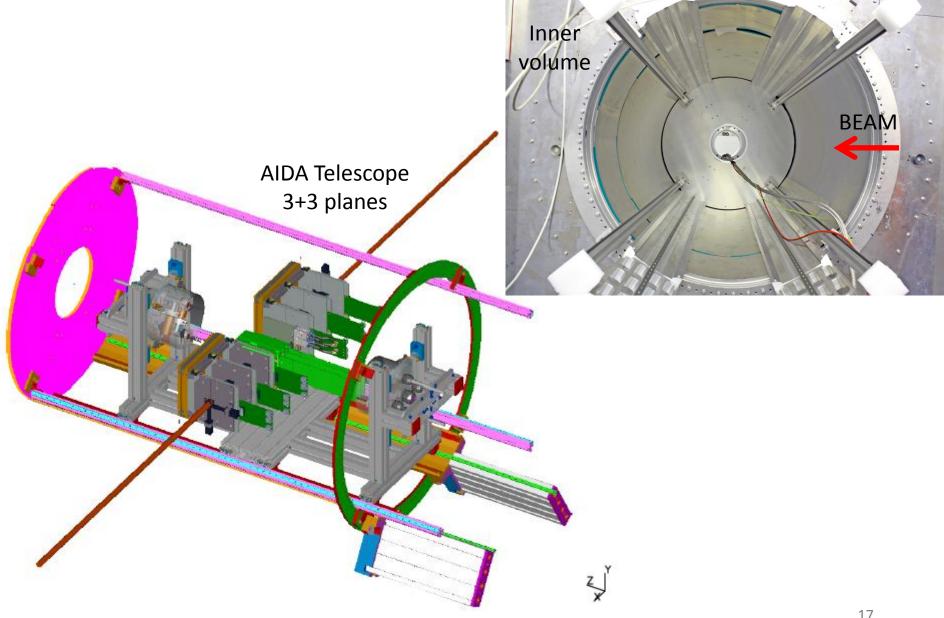

#### VXD and AIDA Telescope

Support frame

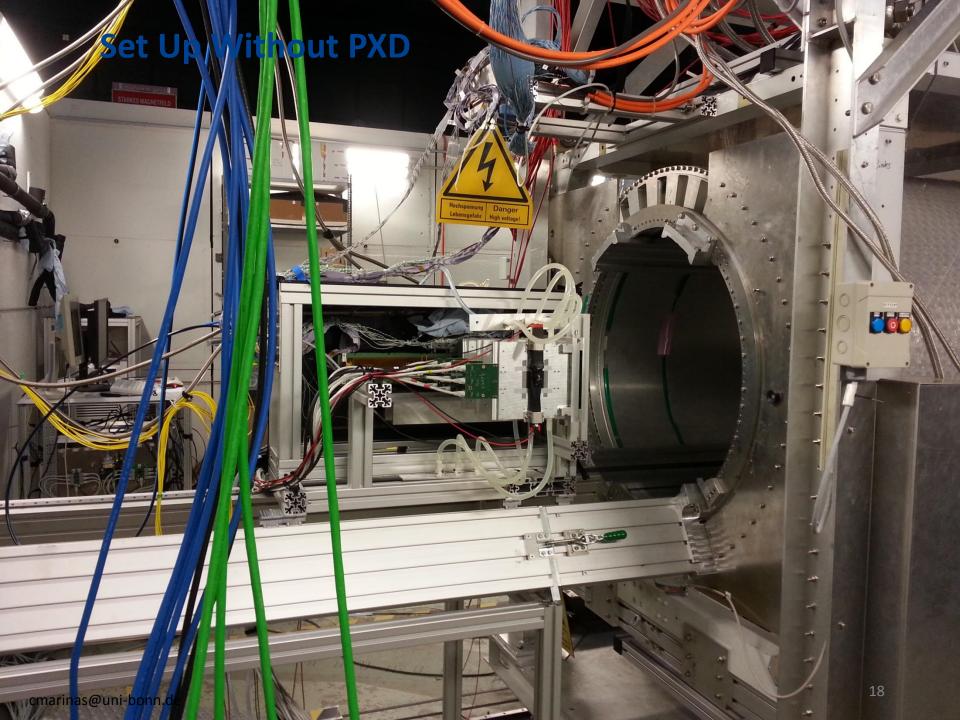

#### **Integration into the PCMAG**

#### **Integration into the PCMAG**

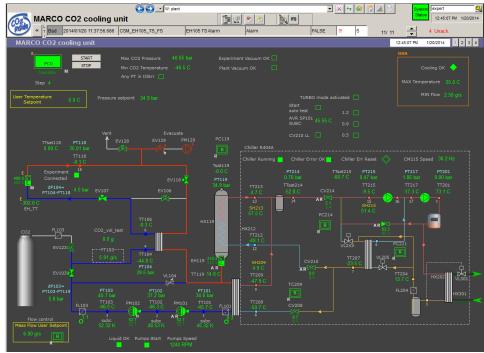

- Connected (only) to the SVD

- Additional close loops with heaters for tuning

#### **Temperature Stability**

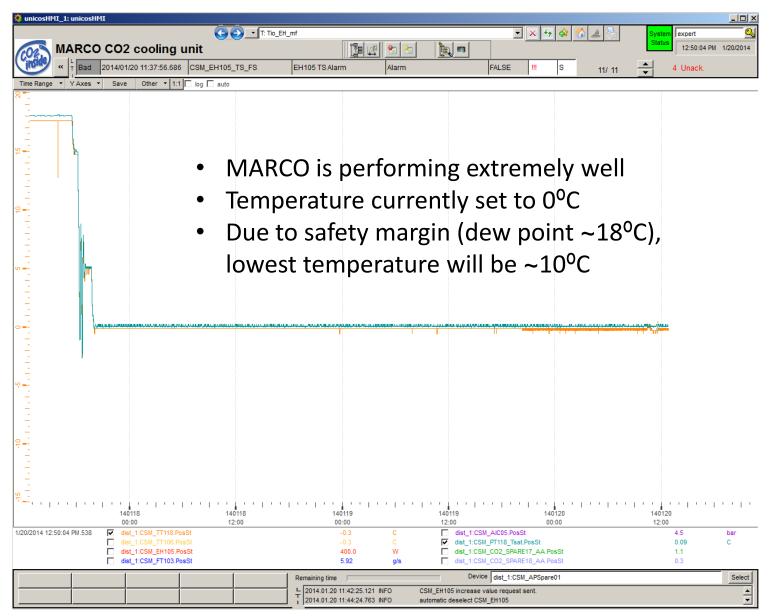

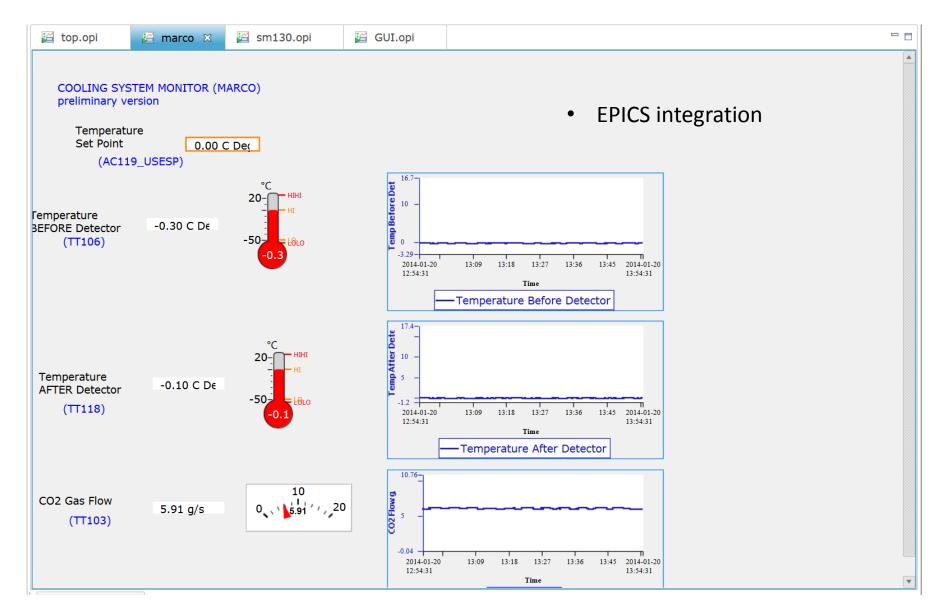

#### **MARCO Slow Control**

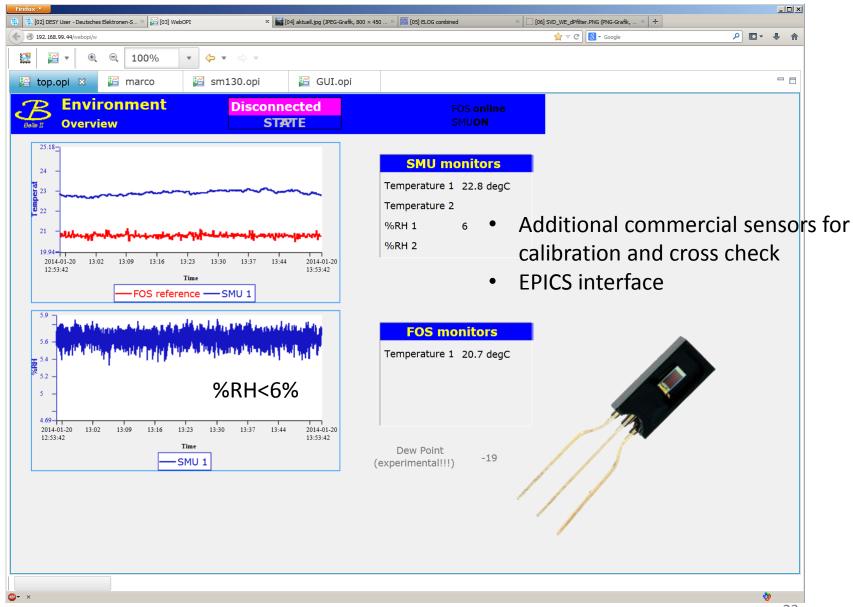

#### **Environmental Monitors**

| <ul> <li>192. 168.99.44/webopi/w</li> <li>192. 168.99.44/webopi/w</li> <li>192. 168.99.44/webopi/w</li> </ul> | 150% 🔻 🔶 🔻                           |                                                        |                                                       | <u></u> ₹                                        | C Soogle                                                         | 9- + |

|---------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------|------|

|                                                                                                               | marco 🔀 sm130                        |                                                        | i                                                     | T <sub>CO2</sub> =0°C                            |                                                                  |      |

| IDN<br>S/N                                                                                                    | Micron Optics s<br>SIABNM            | m130, 2.0h-50                                          | -105-14                                               |                                                  | online 🕒<br>fan 1 🔍<br>fan 2 💿                                   |      |

| Peak 1<br>作品的 1 (°<br>C)<br>Peak 2<br>作品的 2 (°                                                                | Channel 1<br>1550.44 nm<br>20.8 degC | Channel 2<br>1529.93 nm<br>20.5<br>1535.06 nm<br>-1.24 | Channel 3<br>1569.52 nm<br>1.05<br>T <sub>inlet</sub> | Channel 4<br>0 nm<br>T <sub>outlet</sub><br>0 nm | calibration<br>fault                                             |      |

| C)<br>Peak 3<br>作品的 3 (°<br>C)<br>Peak 4<br>作品的 4 (°                                                          |                                      | 1540.06 nm<br>18.05<br>1549.89 nm<br>20.3              |                                                       | 0<br>0.01                                        | Temp<br>Disp                                                     |      |

| C)<br>Peak 5<br>femp 5 (°<br>C)                                                                               |                                      | 1559.97 nm<br>20.88                                    | • In<br>• Te<br>• Co                                  | emperature                                       | VD CO <sub>2</sub> lines<br>of the chamber<br>ng and integration |      |

#### **Environmental Monitors**

#### **Operation with Bench PS**

| Power Sup   | ply Cont | trol Softv   | vare   |               |               |                   |         |                       |         |            | □ X  |

|-------------|----------|--------------|--------|---------------|---------------|-------------------|---------|-----------------------|---------|------------|------|

| Loggir      |          | :\<br>:\ini\ |        | Path<br>Path  |               |                   |         | 1-46-35.txt<br>UNLOCK | ED      | Only Digit | tal  |

| HMP404      | 0 DHP+S  | w COM1       | 2 👻    | Digital Volta | ges okay!     | Ir                | nit all | Close                 | all     | DHP(s)     |      |

| HMP404      | 0 DCD    | COM1         | 3 👻    | DEPFET Vo     | oltages okay! |                   | Po      | werUp digi            | tal     | DCD(s) 4   | 00mA |

| GHi GLo     | CHi CLo  | COM1         | 1 🔻    | opened        |               | -                 | Pow     | er Up DEP             | FET     | DCD(s) 8   | 00mA |

| Bulk CC     | G        | COM6         | •      | opened        |               |                   | Pow     | er Down D             | EPFET   |            |      |

| Source I    | Drift    | COM8         | •      | opened        |               | STOP              |         |                       |         | Switchen   | (s)  |

| PolyCov     | er HV    | COM5         | j 👻    | opened        |               |                   |         | wer Down o            | digital |            |      |

|             | Write    | Data         | Read I | Data          | l             | write to<br>Write |         | ):\\test.txt<br>Read  | Data    | LVDS 2.0   |      |

|             | [V]      | [A]          | [V]    | [mA]          |               | [V]               | [A]     | [V]                   | [mA]    | LVDS 2.1   |      |

| DCD VDDD    | 1.8      | 0.900        | 1.800  | 508.3         | ClearLow      | 19.0              | 0.050   | 19.000                | 16.4    | LVDS 2.3   | 3V   |

| DCD VDDA    | 1.95     | 0.800        | 1.950  | 545.8         | ClearHigh     | 22.0              | 0.050   | 22.000                | 3.4     |            |      |

| DCD RefIn   | 1.1      | 0.300        | 1.100  | 74.6          | GateLow       | 7.3               | 0.050   | 7.300                 | 10.1    |            |      |

| DCD AmpLow  | 1.55     | 0.600        | 1.550  | 354.7         | GateHigh      | 3                 | 0.050   | 3.000                 | 6.2     |            |      |

| DHP VDDD    | 1.8      | 0.250        | 1.800  | 60.3          | ClearGate     | 2.0               | 0.012   | 002.00                | 0       |            |      |

| DHP VDD     | 1.2      | 0.400        | 1.200  | 89.5          | Source        | 7                 | 0.05    | 007.00                | 40      |            |      |

| LVDS-single | 2        | 0.050        | 2.001  | 9.1           | Bulk          | 10.0              | 0.010   | 010.00                | 0       |            |      |

| Switcher    | 1.8      | 0.050        | 1.800  | 10.1          | Drift         | 3.0               | 0.060   | 003.00                | 0       |            |      |

| Debug       | jging    |              | se     | end           | HighVoltage   | 19                | 0.010   | 019.00                |         |            |      |

|             |          |              |        |               | Polycover     | 2.1               | 0.010   | 002.10                | 1       |            |      |

|             | -        | •            | r•     |               | . / 1         |                   |         |                       |         |            |      |

| •           | S        | peci         | ric p  | ower          | up/dov        | vn se             | eque    | ences                 | _       |            |      |

PS with sense lines → patch panel → 15 m cable → breakout board → Glenair → H6

cmarinas@uni-bonn.de

#### **Belle II Power Supplies**

| POWERSUPPLY RUNNING \$(DEVICE) Disconnu |                |                      |                     |   |                                                      |                    |                       |  |  |

|-----------------------------------------|----------------|----------------------|---------------------|---|------------------------------------------------------|--------------------|-----------------------|--|--|

| ENABLED                                 | CONNECT        | red <b>RU</b>        | JNNING              |   | <ul> <li>OVP</li> <li>THERM,</li> <li>UPS</li> </ul> | AL                 | Emergency<br>Shutdown |  |  |

|                                         | Set Current    | Set Voltage          | Regulator<br>Status |   | Voltage at<br>Regulator                              | Voltage at<br>Load | Current               |  |  |

| NOT_USED_1                              | 0 mA           | 0 mV                 |                     | 1 | 0 mV                                                 | 0 mV               | 0 mA                  |  |  |

| NOT USED 2                              | 0 mA           | 0 mV                 |                     | 1 | 0 mV                                                 | 0 mV               | 0 mA                  |  |  |

| NOT USED 3                              | 0 mA           | 0 mV                 |                     | 1 | 0 mV                                                 | 0 mV               | 0 mA                  |  |  |

| NOT USED 4                              | 0 mA           | 0 mV                 |                     | 1 | 0 mV                                                 | 0 mV               | 0 mA                  |  |  |

| NOT_USED_7                              | 0 mA           | 0 mV                 |                     | 0 | 13 mV                                                | 6 mV               | 1 mA                  |  |  |

| NOT_USED_8                              | 0 mA           | 0 mV                 |                     | 0 | 9 mV                                                 | 12 mV              | 1 mA                  |  |  |

| buffer                                  | 50 mA          | 1800 mV              |                     | 0 | 3 mV                                                 | 0 mV               | 1 mA =                |  |  |

| bulk                                    | 10 mA          | 17000 mV             |                     | 0 | 5 mV                                                 | 7 mV               | 0 mA                  |  |  |

| ccg                                     | 10 mA          | 5000 mV              |                     | 0 | 24 mV                                                | -24 mV             | 8 mA                  |  |  |

| clear-off                               | 30 mA          | 10000 mV             |                     | 0 | 28 mV                                                | 29 mV              | 0 mA                  |  |  |

| clear-on                                | 30 mA          | 29000 mV             |                     | 0 | 27615 mV                                             | -7559 mV           | -3 mA                 |  |  |

| dcd-amplow                              | 600 mA         | 350 mV               |                     | 0 | 270 mV                                               | -89 mV             | 0 mA                  |  |  |

| dcd-avdd                                | 900 mA         | 1900 mV              |                     | 0 | 406 mV                                               | 0 mV               | 7 mA                  |  |  |

| dcd-dvdd                                | 800 mA         | 1800 mV              |                     | 0 | -5 mV                                                | -3 mV              | -1 mA                 |  |  |

| dcd-refin                               | 400 mA         | 1100 mV              |                     | 0 | 363 mV                                               | -2 mV              | 8 mA                  |  |  |

| dhp-core                                | 400 mA         | 1200 mV              |                     | 0 | -1 mV                                                | 9 mV               | 5 mA                  |  |  |

| dhp-io<br>drift                         | 400 mA         | 1800 mV              |                     | 0 | 2 mV                                                 | 6 mV               | 2 mA                  |  |  |

|                                         | 10 mA          | 4000 mV              |                     | 0 | 0 mV                                                 | 22 mV              | 0 mA                  |  |  |

| gate-off<br>gate-on                     | 30 mA          | 10000 mV             |                     | 0 | 5 mV                                                 | 6 mV               | -1 mA                 |  |  |

| hv                                      | 30 mA<br>10 mA | 4000 mV<br>-12000 mV |                     | 0 | 17 mV<br>-34 mV                                      | 13 mV<br>-13 mV    | 0 mA<br>0 mA          |  |  |

| polycover                               | 10 mA          | 4900 mV              |                     | 0 | - 34 mv<br>13 mV                                     | -15 mV<br>8 mV     | 0 mA                  |  |  |

| source                                  | 50 mA          | 7000 mV              |                     | 0 | 7366 mV                                              | 7000 mV            | 25 -1 mA              |  |  |

| sw-dvdd                                 | 50 mA          | 1800 mV              |                     | 0 | 51 mV                                                | 8 mV               | 3 mA                  |  |  |

- PS ready in TB24 ٠

- **EPICS** interface ullet

- Interlock to MARCO ٠

- Development of special power ٠ up sequence

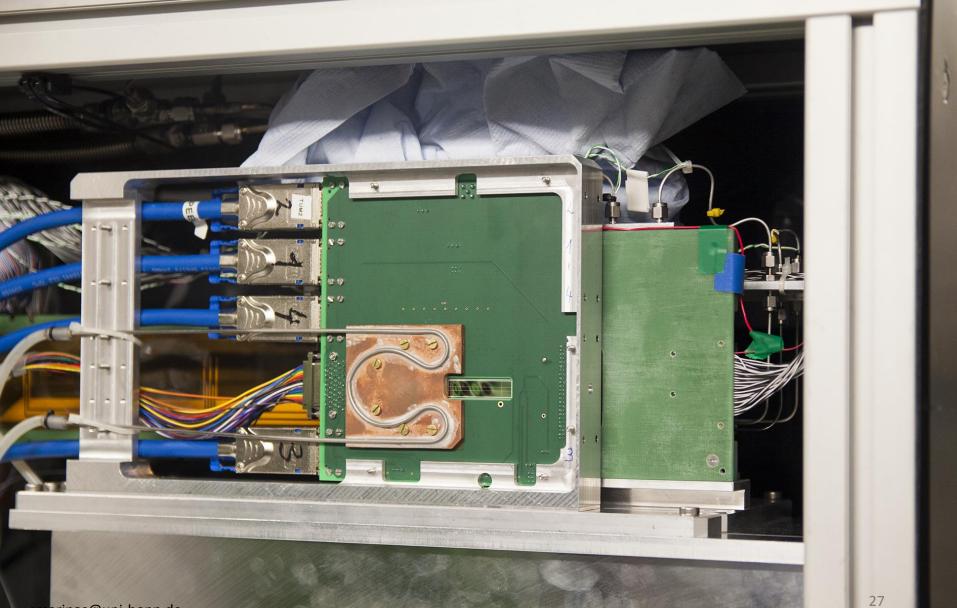

#### **Hybrid6 Installation**

#### **L1 Final Position**

## Telescope and PCMAG

Closed box  $N_2$  flow

05

cmarinas@uni-bonn.de

### Final Position

. CCC

cmarinas@uni-bonn.de

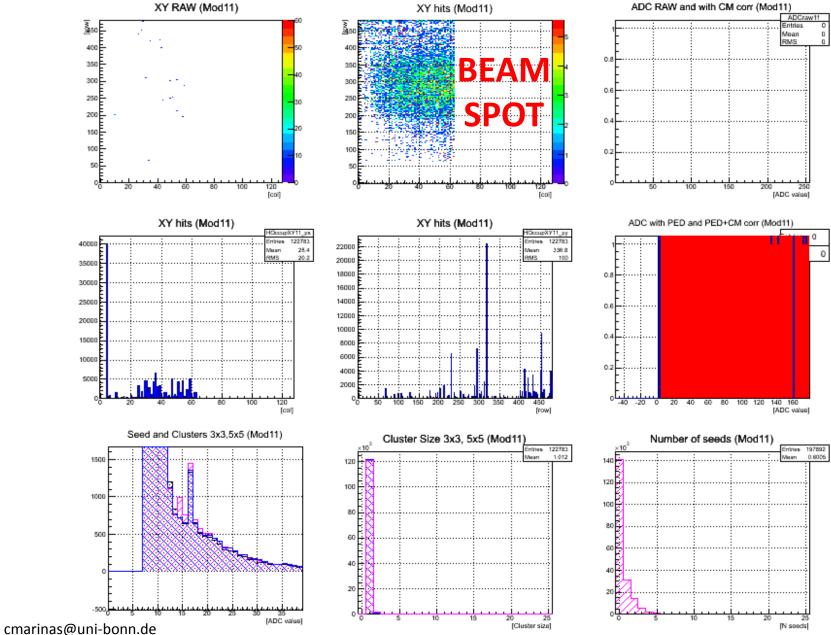

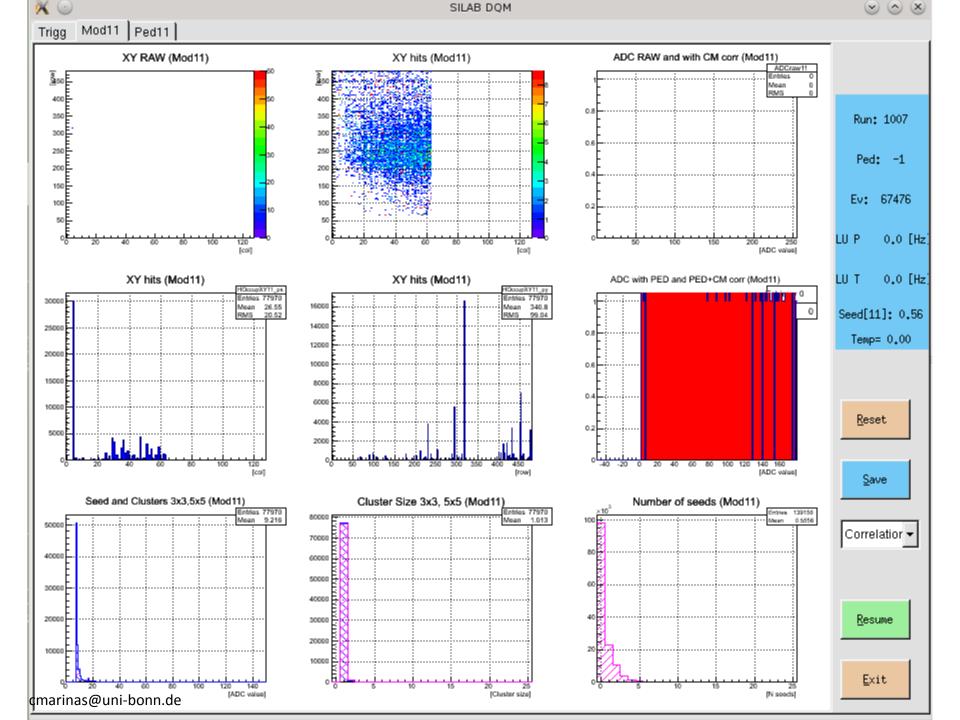

#### **DAQ via BonnDAQ**

[N seeds]

30

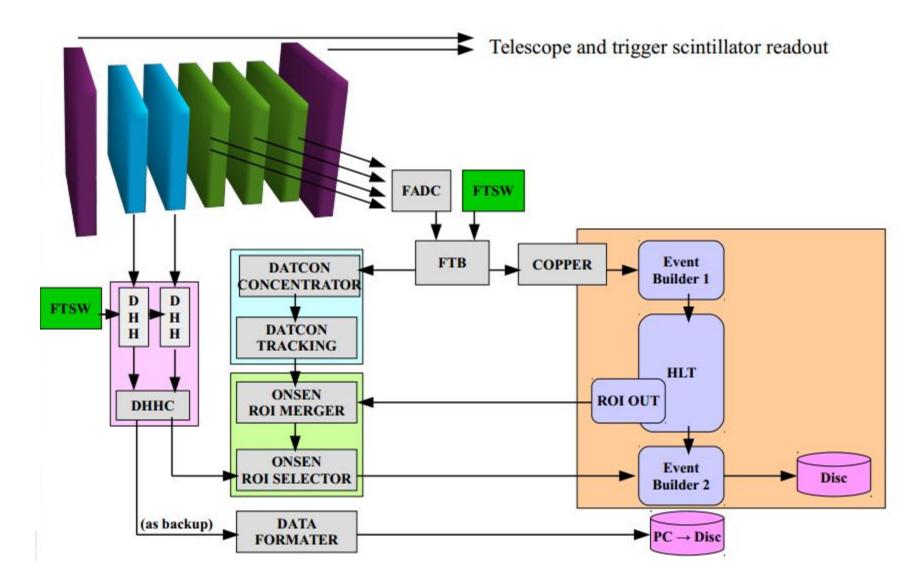

#### **Test Beam VXD DAQ Estructure**

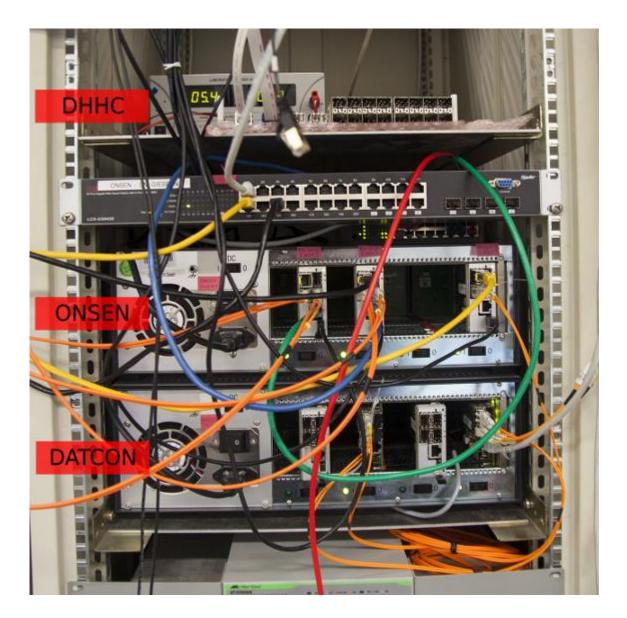

#### DATCON

- Two AMC rev. 2:

- Concentrator for receiving SVD data from FTB and preprocessing

- Tracking for track extrapolation, ROI creation and transmitter to ONSEN

- Link between FTB and DATCON stable

- Proper decoding of zero-suppressed SVD data

- Correct coordinate translation

- Event and data management works

- Track extrapolation and ROI creation, functional

- Hough transformation and ROI management still not fully verified

#### **DHH and DHHC**

- DESY test beam configuration : full readout chain

- PXD matrix  $\rightarrow$  1(2)xDHH  $\rightarrow$  DHHC  $\rightarrow$  ONSEN

- DHH

- Up to 4 x (DHP+DCD) + Switchers

- Full EPICS control via IPBUS

- Triggers+127MHz clock from DHHC via optical link

- UDP for pedestal (full frame readout) and Bonn DAQ || PocketDAQ

- DHHC

- FTSW interface

- Interface to ONSEN @ 3.125 Gbps with backpressure flow control

- Full EPICS control via IPBUS

- Current firmware supports 2 DHH modules i.e. 2 detectors

$\rightarrow$  System tested with the PXD6 detector @ 1kHz random trigger rate and 200 µs dead time. (Additional tests at higher rate ongoing)

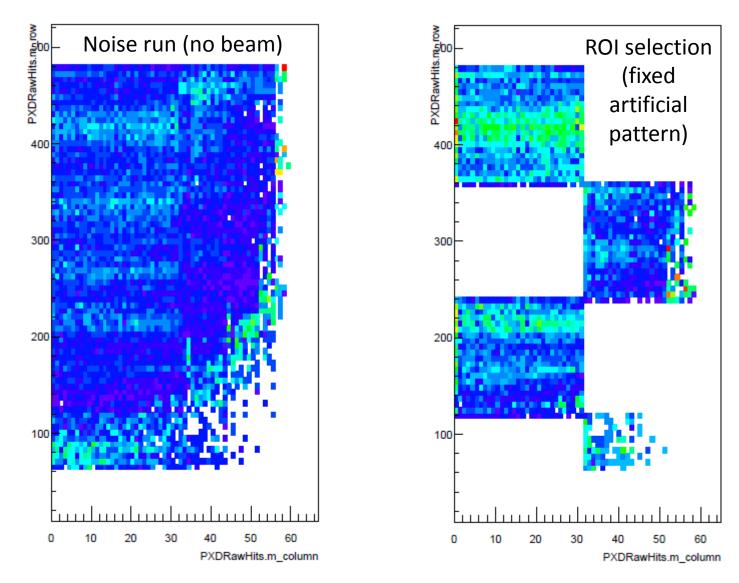

#### **ONSEN**

- "Pocket ONSEN" debugging system with four Compute Node cards is used.

Running stably after initial troubles with most current firmware.

- First real data (with dummy ROIs) processed and written to EVB on Monday.

- Full DAQ chain is established: DEPFET  $\rightarrow$  DHP  $\rightarrow$  DHH  $\rightarrow$  DHHC  $\rightarrow$  ONSEN ( $\leftarrow$  HLT)  $\rightarrow$  EVB

#### **Full Data Path with ROI Selection**

Although fine tuning is necessary, the test beam is already a <u>big success</u>!

All the PXD hardware, software and firmware is ready to declare run conditions

Decisive step forward towards the Belle II PXD

# Congratulations for the hard work!

## Thank you

cmarinas@uni-bonn.de

Power Up sequence:

- 1. Apply DHP (IO 1.8V and Core 1.2V) & Switcher voltage (1.8V) and converter voltage (around 2.0V in order to switch it on => decrease to 1.8V)

- 2. Configure DHPs (switch off clock for DCDs)

- 3. Apply DCD voltages (VDDD, VDDA, RefIn, Amplow, current limits at 400mA)

- 4. Configure DCDs, switch off analog part of the DCDs

- 5. Increase the current limits (VDDD 800mA, VDDA 900mA, Amplow 600mA) DCD(s) 800mA

- 6. Switch on DHP clocks and analog part of the DCDs

- 7. Switch on the DEPFET (in the normal sequence) [Bulk, Clearhigh, Clearlow, GateHi, Gatelow=0V, Source, Cleargate, Gatelow, Highvoltage/Backplane, Drift, Polycover) [Power Up DEPFET]

#### Power Down sequence:

- 1. Switch off DEPFET Power Down DEPFET

- 2. Switch off ASICs

Power Down digital

0.050

LVDS-single

2

2.001 9.1