# SPADIC – Self-triggered charge pulse processing ASIC

Tim Armbruster, Peter Fischer, Michael Krieger, Ivan Peric

ZITI, Universität Heidelberg michael.krieger@ziti.uni-heidelberg.de

TPC Workshop, Bonn 28.02.2013

### Introduction

- <u>Self-triggered Pulse Amplification and Digitization ASIC</u>

- main application: TRD subsystem of CBM (FAIR/GSI)

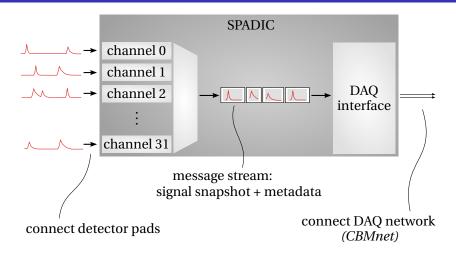

### Concept

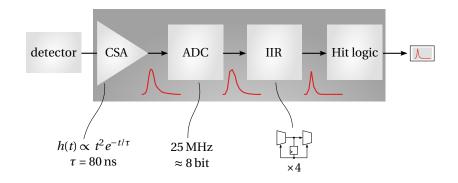

### Channel overview

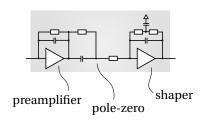

# Charge amplifier

■ input range: 75 fC

shaping time: 80 ns

■ noise: 800 e<sup>-</sup> @ 30 pF

two amplifiers per channel selectable:

- positive polarity (4 mW)

- negative polarity (10 mW, not optimized)

layout & schematics: modular, scalable

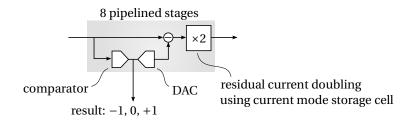

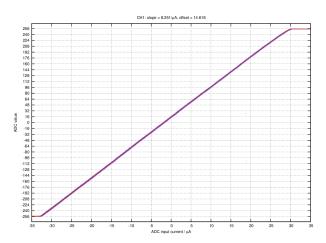

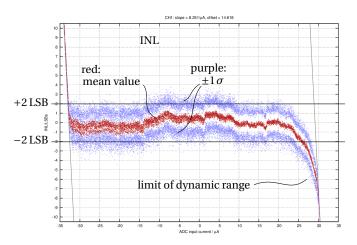

### **ADC**

- current mode pipelined design

- 25 MHz sample rate, continuously running

- 9 bit nominal output

- resolution ≈ 8 bits

- 4.8 mW, rad-hard layout,  $400 \times 300 \,\mu\text{m}^2$

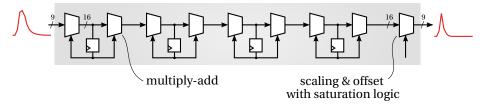

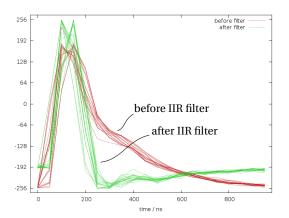

### IIR Filter

- 16 bit internal resolution

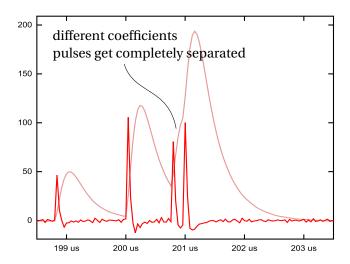

- 6 bit coefficients

- freely programmable  $(\frac{-32,...,31}{32})$

- instability excluded

### IIR Filter

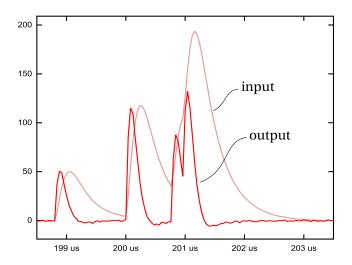

#### purpose: "tail cancellation"

shorten pulses → reduce pileup/help hit logic

- model signal as sum of exponential terms:

- $x_n \propto \sum w_i q_i^n$

- recursion:  $y_n = x_n + bx_{n-1} + ay_{n-1}$

- each filter stage shifts relative weights:  $w'_i = \frac{q_i + b}{q_i a} w_i$

## IIR filter: examples (simulation)

## IIR filter: examples (simulation)

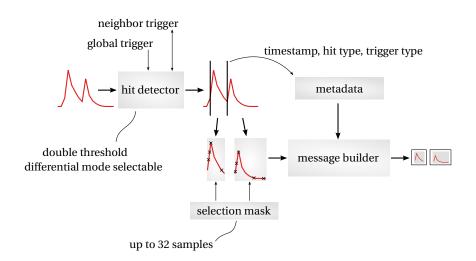

### Hit logic

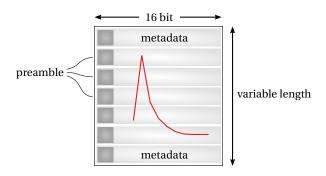

# Message format

- every word has a preamble (4 or 1 bit)

- easy recovery of message stream

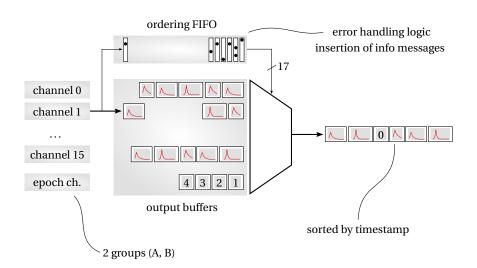

# Message output multiplexing

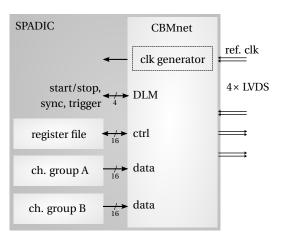

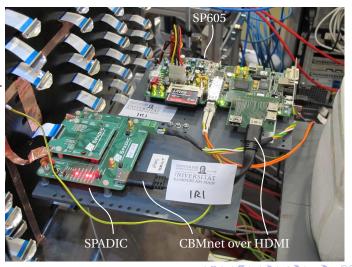

## DAQ interface (CBMnet)

- error checking, retransmission

- deterministic latency messages (DLM)

- different traffic classes share single serial link

- 500 Mbit/s (DDR), 8b/10b encoded, LVDS (1 input, 2 outputs)

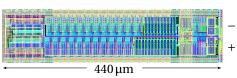

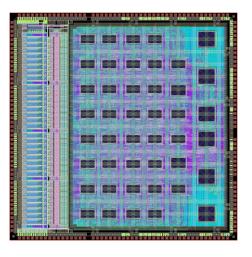

### Layout view

- UMC 180 nm

- overall size:  $5 \times 5 \,\mathrm{mm}^2$

- digital part:

- $3.5 \times 4.5 \,\mathrm{mm}^2$

- home-made standard cell library

- 2.5 million transistors, 23k FF, 81k gates

- 44 Faraday SRAMs

- total wire length: 14.4 m

- Power (200 MHz): 600 mW

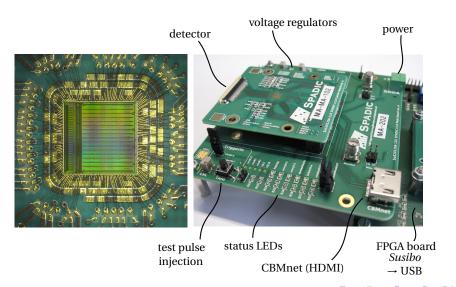

### Test setup

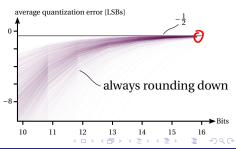

ADC curve: taken at 20 MHz sample rate, preliminary bias settings

ADC curve: taken at 20 MHz sample rate, preliminary bias settings

#### measured pulses (20 MHz sample rate)

$CSA \rightarrow ADC \rightarrow IIR \ Filter \rightarrow \ hit \ logic \rightarrow \ message \ building \ \checkmark$

#### CBM beamtime October 2012 @ CERN: first time CBMnet readout

TRD prototype

# Development status & lookout

- shown measurements done using auxiliary readout (bypassing CBMnet, limited capabilities)

- no major bugs discovered, everything so far tested works

- lab setup not yet CBMnet compatible → in progress

- full characterization (CSA, ADC) to be done, optimal settings to be found

### Summary

#### **SPADIC**

complete system for charge pulse readout

- 32 channels

- self-triggered recording of whole pulse shapes (programmable selection mask)

- neighbor trigger, global trigger

- flexible digital signal processing

- time-sorted output message stream with notification of error conditions

- CBMnet: built-in DAQ connection with reliable data transmission and synchronization features using 4 LVDS pairs

Self triggered Pulse Amplification and Digitization asIC

http://spadic.uni-hd.de